设计和基于SP Builder和HDL Coder的FIR滤波器设计与比较

1. 引言

随着超大规模集成电路的快速发展,数字信号在越来越多的应用领域中逐渐取代模拟信号,并表现出强大的优势[1]。在数字电路领域,大多数设计都需要软件编程来辅助硬件设计。在涉及数字集成电路行业的大多数领域中,需要使用VHDL/Verilog代码来描述系统功能,而手写VHDL/Verilog代码是一件非常耗时且繁琐的工作。

SP Builder 是由 Altera公司推出的工具箱[2]。它可以将 Simulink模型转换为可编译的 VHDL/Verilog代码,并通过在 Simulink模型中完成系统仿真、在 Modelsim 中完成硬件电路仿真,大大简化了设计流程;HDL Coder 是由 MathWorks 推出的可将 MATLAB代码/Simulink模型转换为 VHDL/Verilog代码 的工具箱[3]。它使工程师能够使用 MATLAB 实现 FPGA 和专用集成电路 设计,显著提高了 系统工程师 的工作效率,加快了 FPGA 系统级设计与开发进程。

本文中,我们重点研究上述两种代码生成工具的使用。以16阶FIR低通滤波器为例,采用Altera的 SP Builder和MathWorks的HDL Coder生成 Verilog代码,并在Modelsim中完成仿真波形。根据Quartus II提供的技术报告,对比资源消耗情况,以识别这两种工具的优缺点。

2. FIR滤波器理论

数字滤波器的目的是通过数学运算处理采样数据。一个M抽头FIR滤波器系统的系统函数如[4]所示:

$$

H(z) = \sum_{k=0}^{M} b_k z^{-k}

\quad (1)

$$

其中,延迟段数量也称为FIR滤波器的抽头。基本的 FIR滤波器可以表示如下:

$$

y(n) = \sum_{i=0}^{L-1} x(n-i)h(i)

\quad (2)

$$

其中,$x(n-i)$是输入采样序列,$h(i)$是滤波器系数,$L$是滤波器系数长度,$y(n)$表示滤波器输出序列。卷积也可用来表达输出序列 $y(n)$ 与 $x(n)$、$h(n)$之间的关系,如:

$$

y(n) = x(n) * h(n)

\quad (3)

$$

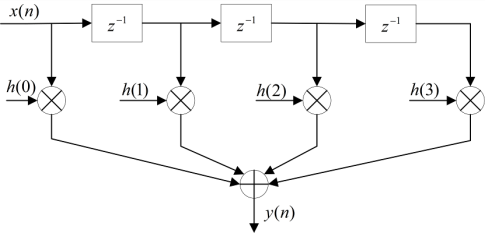

图1显示了一个典型的直接I型3抽头FIR滤波器,其输出序列满足以下方程:

$$

y(n) = h(0)x(n) + h(1)x(n-1) + h(2)x(n-2) + h(3)x(n-3)

\quad (4)

$$

如图1所示,该3抽头FIR滤波器包含四个乘法单元、三个延迟周期和一个四输入加法器。如果使用传统的SP,则指令只能串行执行,因此无法在同一个指令周期内完成整个过程。使用现场可编程门阵列的优势在于可以采用并行结构,从而在单个时钟周期内获得FIR滤波器的输出。

3. 代码生成工具

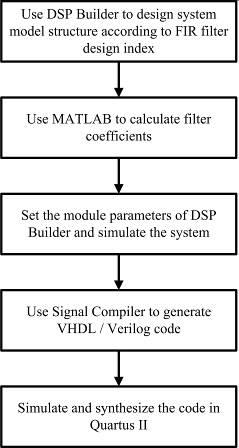

3.1 DSP Builder

DSP Builder 是一种可将 Simulink 系统级模型转换为 VHDL / Verilog 代码的设计与开发工具。基于 DSP Builder 的 FIR滤波器 设计的一般流程如图 2[5] 所示。

我们采用窗函数法,设置滤波器类型为低通,设计方法为FIR,滤波器抽头为15(因为一般16抽头FIR滤波器的常数项为0),窗类型为凯泽,β为0.5,采样频率为 12.5MHz,截止频率为2MHz。系统函数 $H(z)$ 表达式如下:

$$

H(z) = \sum_{k=1}^{16} b_k z^{-k} = \sum_{k=0}^{15} b_k z^{-k}

\quad (5)

$$

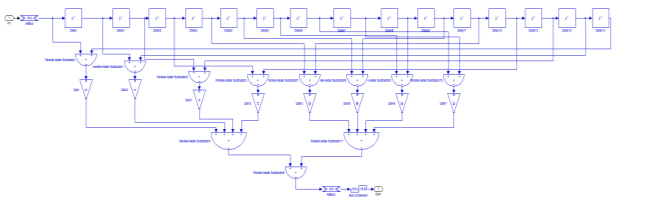

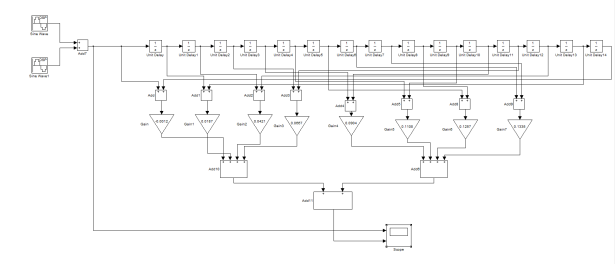

通过FDATool可以获取优化后的滤波器系数。为了节省资源,在DSP Builder中采用整数运算。输入端口使用了优化后的滤波器系数。16抽头FIR滤波器的模型原理图如图3所示。

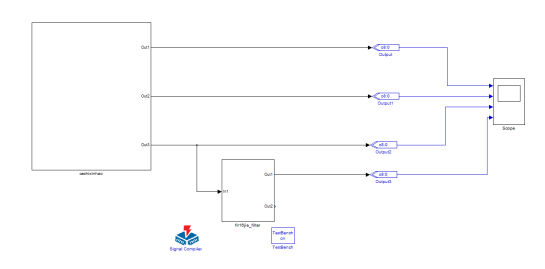

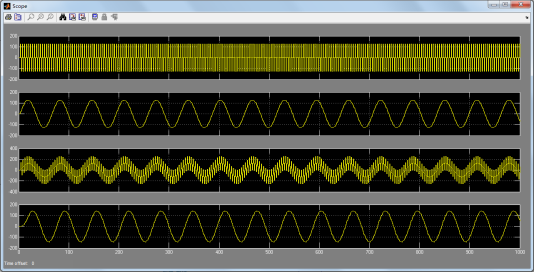

构建一个信号发生器作为信号输入,总体测试原理图如图4所示。左侧的模块是信号发生器,下方的模块是FIR滤波器。MATLAB中的仿真结果如图5所示。

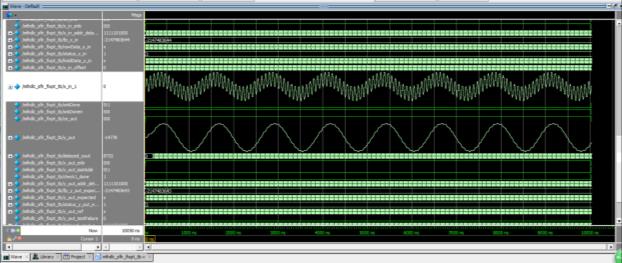

如图5所示,第一行为12MHz的高频波,第二行为0.8MHz的低频波,第三行为两个波形叠加的结果,第四行为滤波后的结果。可以看出,高频波被完全滤除。然后我们使用Signal Compiler生成Verilog代码,在Modelsim中的仿真结果如图6所示。

3.2 HDL Coder

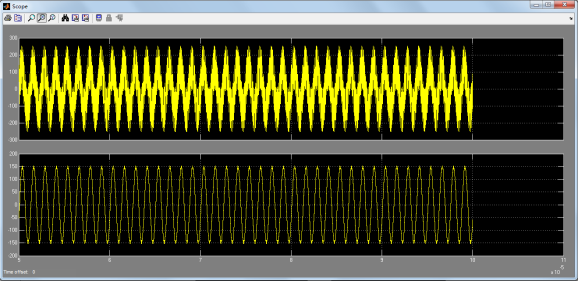

HDL Coder 是由 MathWorks 开发的工具。其主要功能是将 MATLAB代码/Simulink模型 转换为 VHDL/Verilog 代码。为了完成 DSP Builder 与 HDL Coder 之间的比较,我们在滤波器结构、字长和滤波器系数相同的情况下,使用 HDL Coder 设计一个 FIR滤波器。MATLAB代码 和 Simulink模型 在功能上是等效的,而 Simulink模型 更直观易用。这里我们使用 Simulink模型 来设计 FIR滤波器。具有相同指标的 16抽头FIR低通滤波器 的 Simulink模型 如 图7 所示,MATLAB 中的仿真结果如 图8 所示。

使用 HDL Coder 生成 Verilog代码 主要分为三个部分:生成定点功能;生成 Verilog文件;生成测试平台文件。我们在 Modelsim 中对生成的 Verilog文件 进行仿真,结果如 图9 所示。

4. 讨论

我们选取了几款FPGA器件,使用DSP Builder/HDL Coder生成的Verilog代码在 Quartus II中进行综合,然后对比总逻辑单元和总引脚数的消耗情况。比较结果如表1所示。

| 器件 | 技术 | 逻辑单元 | Pins |

|---|---|---|---|

| EP1S10 F484C5 | DSP Builder | 311/10570 (3%) | 38/336 (11%) |

| EP1S10 F484C5 | HDL Coder | 212/10570 (2%) | 102/336 (30%) |

| EP2S15 F484C3 | DSP Builder | 151/12480 (1%) | 38/343 (11%) |

| EP2S15 F484C3 | HDL Coder | 112/12480 (1%) | 102/343 (30%) |

| EP2C5 F256C6 | DSP Builder | 248/4608 (5%) | 38/158 (24%) |

| EP2C5 F256C6 | HDL Coder | 156/4608 (3%) | 102/158 (65%) |

| EP4CE6F17C6 | DSP Builder | 249/6272 (4%) | 38/180 (21%) |

| EP4CE6F17C6 | HDL Coder | 156/6272 (2%) | 102/180 (57%) |

在总逻辑单元方面,上述FPGA器件中DSP Builder占用的数量多于HDL Coder,因此在该指标上HDL Coder相较于DSP Builder具有显著优势。在总引脚数方面,DSP Builder生成的代码占用38个引脚,而HDL Coder生成的代码占用102个引脚。这提示我们在某些实际工程应用中,若更关注引脚资源的消耗,则应选择DSP Builder生成Verilog代码;若更关注逻辑单元的消耗,则应选择HDL Coder。

5. 结论

本文以FIR滤波器的设计为例,比较了DSP Builder/HDL Coder在FPGA中生成的Verilog代码的资源消耗情况。结果表明,DSP Builder在引脚消耗方面具有优势,而HDL Coder在逻辑单元消耗方面具有优势。我们应根据实际需求选择 VHDL/Verilog代码生成工具。

1188

1188

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?