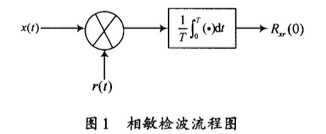

原理是从网上论文找到的,大家自己找一下。相敏检波利用互相关原理,能够十分有效地从噪声中提取出与参考信号具有相关性的待测信号的幅度和相位信息,同时忽略不相关的背景噪声的干扰。

一、数字相敏检波原理

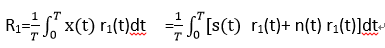

待测信号:x(t)为待测信号s(t)与系统噪声n(t)的叠加,表达式为: x(t) = s(t) + n(t) = A cos(wt +θ)+n(t)

r(t)为与待测信号s(t)同频率的参考信号,在r(t)与s(t)的相位关系不明确的情况下,欲测得s(t)的幅度A与相位差Θ,需要采用两组正交的参考信号r1(t)和r2(t)同时完成相敏检波流程。假设参考信号幅值为1,相位为0,既:

r1(t)=cos(wt), r2(t)=sin(wt),

经过运算:

若认为噪声为随机噪声,与参考信号无关,则要积分时间足够长,n(t)的影响可以被消除得

本文介绍了数字相敏检波(DPSD)原理,通过利用互相关技术从噪声中提取待测信号的幅度和相位信息。在FPGA中实现DPSD,涉及AD转换、乘法和累加操作,算法输出的信噪比与测量时间成正比。FPGA逻辑功能框图展示了实现过程。

本文介绍了数字相敏检波(DPSD)原理,通过利用互相关技术从噪声中提取待测信号的幅度和相位信息。在FPGA中实现DPSD,涉及AD转换、乘法和累加操作,算法输出的信噪比与测量时间成正比。FPGA逻辑功能框图展示了实现过程。

订阅专栏 解锁全文

订阅专栏 解锁全文

1464

1464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?