一、SPI 简介

1.1 SPI 简介

SPI 是一种主从式、全双工、同步串行通信协议,由 Motorola 在 1980 年代提出,常用于 MCU 与外设 (如 Flash、ADC、传感器、显示屏) 之间的高速通信。

Motorola 所定义的 SPI 标准为业界广泛引用,但不同半导体公司的实施细节可能有所不同,这些区别体现在寄存器设置、信号定义、数据格式等。业界没有统一的 SPI 标准,具体应用需要参考特定器件手册。

1.2 特性

1.2.1 优点

- 支持全双工通信

- Push-Pull 驱动性能相比 Open Drain 信号完整性更好,支持高速应用 (100MHz以上)

- 协议支持字长不限于 8bits,可根据应用特点灵活选择消息字长

- 相比 I2C 和 SMbus 节省上拉电阻

- 相比 I2C 和 SMbus 不需要仲裁机制

- 从设备使用主设备时钟,节约时钟要求

- 从设备无需地址寻址

1.2.2 缺点

- 相比 I2C 两根线,SPI 四根线更多

- 没有寻址机制,只能靠设备片选 (chip select) 选择不同从设备

- 没有数据流控制 (但主设备可以通过延缓时钟边缘降低传输速度)

- 没有从设备接收数据 ACK,主设备对于发送成功与否不得而知

- 典型应用只支持单主控

- 没有定义数据校验机制

- 没有统一的国际组织维护,变种多不利于不同厂商设备的互操作性 (interoperability)

- 相比于 RS232、RS422、RS485 和 CAN,SPI 传输距离短

- 不支持热插拔

二、的物理层

2.1 物理层定义

物理层是 OSI 模型的第一层 (最底层),它负责 在物理媒介上发送和接收原始比特流,也就是把 0 和 1 转换成实际可传输的信号。它完全和数据内容无关,只关注 信号如何在介质上传播。

物理层的主要定义有:

- 电气特性:电压幅度、逻辑电平、信号极性 (高电平/低电平表示 0/1)

- 传输速率:比特率 (bps) 或以太网的 (Mbps) 等

- 物理拓扑:点对点 (串口) 、总线 (CAN)、星型 (以太网) 等

- 传输模式 :单工、半双工、全双工

2.2 连线定义

SPI 只有 4 条基本线:

| 名称 | 方向 (主→从) | 作用 |

| SCLK | 输出 | 时钟信号 |

| MOSI | 输出 | 主设备发送数据 |

| MISO | 输入 | 从设备返回数据 |

| SS/CS | 输出 | 片选信号 (低有效) |

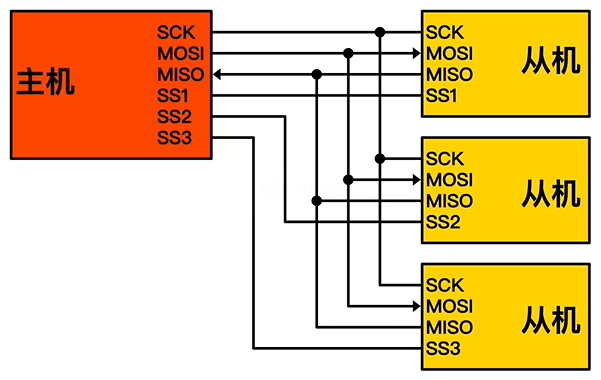

其连线方式如下:

其中 SS/CS 是芯片的片选信号,置高或置低则代表选中这个从设备,在 SPI 总线中,同一时刻只能有一个从设备被选中。

2.3 电气规范与原理图

SPI 不使用差分电路,仅是高低电平判断逻辑,常见逻辑电平标准如下:

| 逻辑标准 | 逻辑 1 (高) | 逻辑 0 (低) | 典型工作电压 | 说明 |

| TTL | ≥ 2.0V | ≤ 0.8V | 5V | 早期MCU常见 |

| CMOS 5V | ≥ 0.7×VCC | ≤ 0.3×VCC | 5V | 常见于老芯片 |

| CMOS 3.3V | ≥ 2.31V | ≤ 0.99V | 3.3V | 当前主流 |

| CMOS 1.8V | ≥ 1.26V | ≤ 0.54V | 1.8V | 低功耗设备 |

2.3 通讯距离

SPI 是板级通讯,一般不会进行过长的数据传输:

| SPI时钟频率 | 推荐最大距离 | 应用场景 |

| 50 MHz | < 10 cm | MCU 与 Flash、ADC、DAC 同板通信 |

| 20 MHz | < 20 cm | 模块间、主板与子板 |

| 10 MHz | < 30 cm | 短排线连接、屏幕或传感器 |

| 5 MHz | < 50 cm | 稍长排线、屏蔽线连接 |

| 1 MHz | < 1 m | 工业布线、屏蔽双绞线 |

| 400 kHz | 1–2 m | 降速通信、低噪声环境 |

| 100 kHz | 3–5 m(极限) | 带隔离器或差分驱动器的 SPI |

2.4 通讯速率

SPI 是 同步串行通信,每个时钟周期传输 1 位数据 (在全双工时主从各自同时传输一位)。

因此:

数据速率 (bps) = 时钟频率 (Hz) × 每时钟传输的位数

也就是说,SPI 每时钟传输的位数就是 1,时钟频率等于 bps。假设主机 SPI 的时钟是 1MHz,那么总线也获得 1Mbps 的传输速度。

但是由于 SPI 是帧结构通信,一帧包括,片选信号、地址/命令字节、数据字节和等待状态。实际数据率约为理论速率的 60%~95%。

三、数据链路层

物理层定义了 0 和 1 的信号形式。数据链路层则提供可靠的数据传输,进行帧的封装、错误检测、流量控制。

- 帧封装:把目标数据封装成一帧 (Frame),加上帧头、帧尾,使接收方能识别帧的起止。

- 物理寻址:每个链路设备都有一个地址,用于在同一总线中识别发送方和接收方。

- 差错检测与纠正:CRC、奇偶校验等方式检测 (有时纠正) 比特错误。

- 流量控制:控制发送速度,防止发送方过快导致接收方缓冲区溢出。

- 重传控制:通过确认(ACK)机制与超时重传,提高传输可靠性。

2.3 SPI 的四种模式

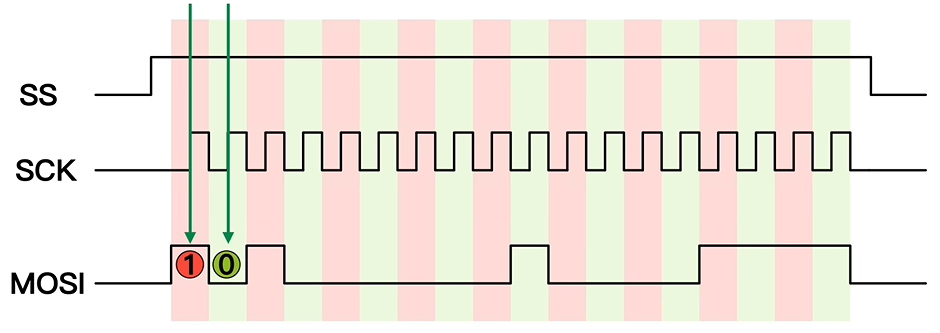

一段 SPI 波形实际如下图:

当选中这个设备后,SS 片选即拉高,之后 SCK 时钟线开始工作,在 SCK 每个上升沿时刻,如果 MOSI 为高电平,则为 1,为 低电平则为 0。

以上的波形为 SPI 0 模式,其实 SPI 共有 0、1、2、3 四种模式。

不同的从设备可能在出厂是就是配置为某种模式,这是不能改变的;但我们的通信双方必须是工作在同一模式下,所以我们可以对我们的主设备的 SPI 模式进行配置,通过 CPOL (时钟极性) 和CPHA (时钟相位) 来控制我们主设备的通信模式,具体如下:

时钟极性 (CPOL) 定义了时钟空闲状态电平:

- CPOL=0,表示当 SCLK=0 时处于空闲态,所以有效状态就是 SCLK 处于高电平时

- CPOL=1,表示当 SCLK=1 时处于空闲态,所以有效状态就是 SCLK 处于低电平时

时钟相位 (CPHA) 定义数据的采集时间:

- CPHA=0,在时钟的第一个跳变沿 (上升沿或下降沿) 进行数据采样,在第2个边沿发送数据

- CPHA=1,在时钟的第二个跳变沿 (上升沿或下降沿) 进行数据采样,在第1个边沿发送数据

| SPI 模式 | CPOL | CPHA | 空闲时 SCK 时钟 | 采样时刻 MIOS | 输出时刻 MOSI |

| 0 | 0 | 0 | 低电平 | 第1个边沿 (奇) | 第2个边沿 (偶) |

| 1 | 0 | 1 | 低电平 | 第2个边沿 (偶) | 第1个边沿 (奇) |

| 2 | 1 | 0 | 高电平 | 第1个边沿 (奇) | 第2个边沿 (偶) |

| 3 | 1 | 1 | 高电平 | 第2个边沿 (奇) | 第1个边沿 (奇) |

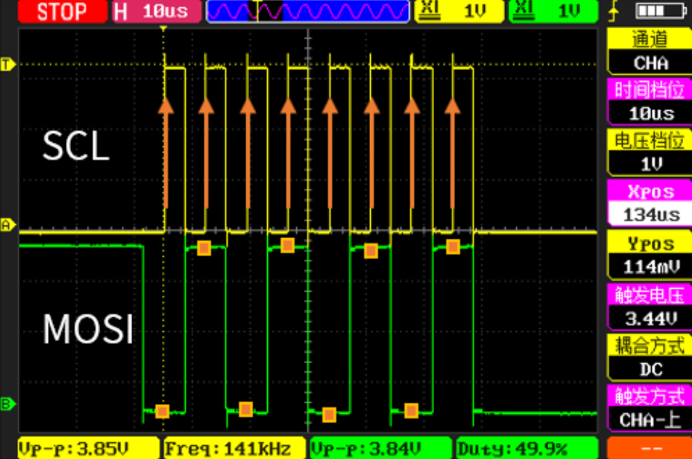

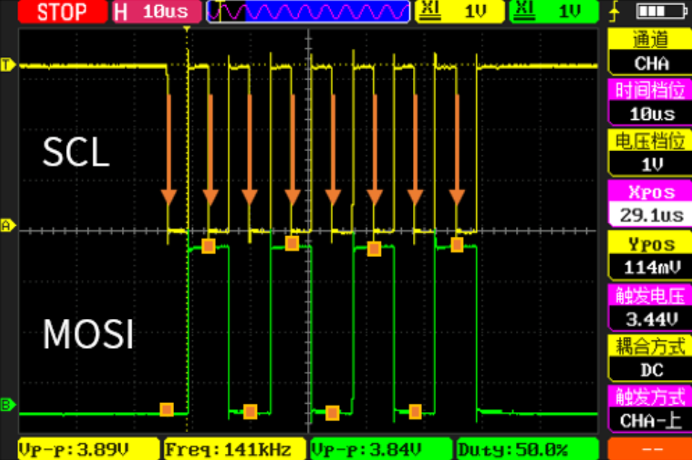

2.3.1 SPI 0 模式

SPI 0 模式下,SPOL = 0,CPHA = 0

可见 SCL 空闲状态是低电平,MOSI 在第一个边沿传输。

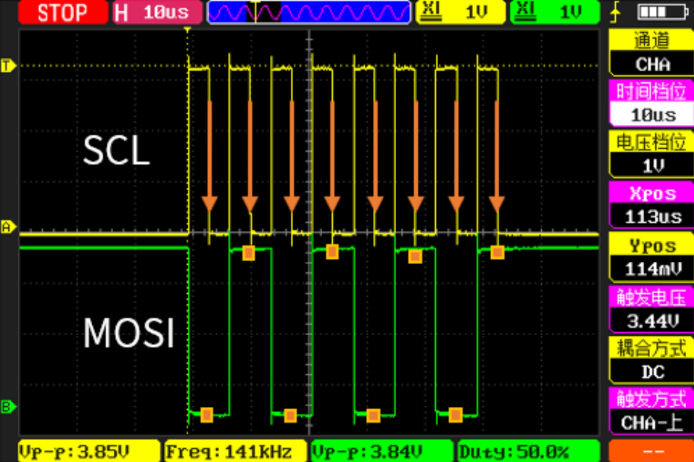

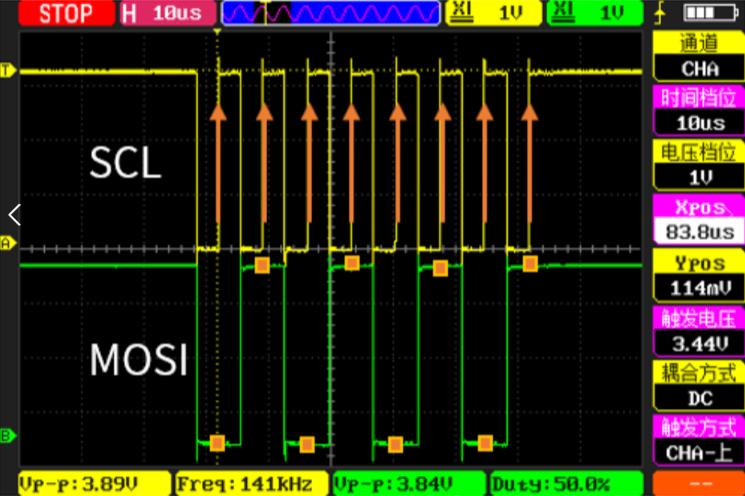

2.3.1 SPI 1 模式

SPI 0 模式下,SPOL = 0,CPHA = 1

可见 SCL 空闲状态是低电平,MOSI 在第二个边沿传输。

2.3.1 SPI 2 模式

SPI 0 模式下,SPOL = 1,CPHA = 0

可见 SCL 空闲状态是高电平,MOSI 在第一个边沿传输。

2.3.1 SPI 3 模式

SPI 0 模式下,SPOL = 1,CPHA = 1

可见 SCL 空闲状态是高电平,MOSI 在第二个边沿传输。

四、的应用层

4.1 应用层定义

OSI 模型中的应用层 (Application Layer) 是第七层,也是最靠近用户的一层。它直接为用户应用程序提供网络服务,是网络通信的最上层接口。

应用层的主要作用是:

- 为用户或软件提供网络访问接口

- 定义应用程序之间如何通信

- 规定数据格式、消息结构、命令集等

4.2 SPI 驱动 93C46 EEPROM 格式

93C46 是一款容量为 1 Kbit (1024 位) 的串行 EEPROM 应用层以驱动 93C46 EEPROM 举例:

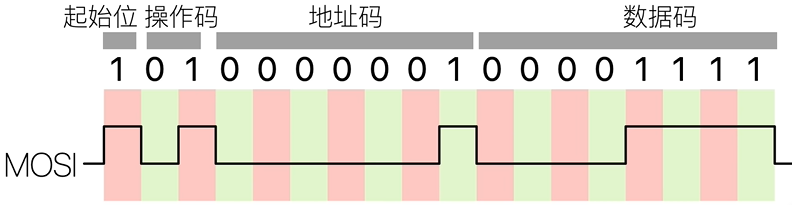

其一帧包括:起始位、操作码、地址和数据,如果我们使用七位地址、八位数据模式读写,则一帧的内容如下:

| 指令 | 起始位 (1位) | 操作码 (2位) | 地址 (7位) | 数据 (8位) |

| 写数据 | 1 | 01 | 7位 | 8位 |

| 读数据 | 1 | 10 | 7位 | 8位 |

如果我们要向 000 0001 地址写入 0000 1111,这样我们的 MOSI 的波形是:

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?