一直都在讨论应该使用同步复位还是异步复位,以及复位和置位是否同时使用的问题。也基本达成一致,我将简要分析一下这么做的原因,不足之处,还请指教:

1.复位和置位不能同时使用,因为很多基本电路单元不同时包含复位和置位端;2.异步复位同步化。

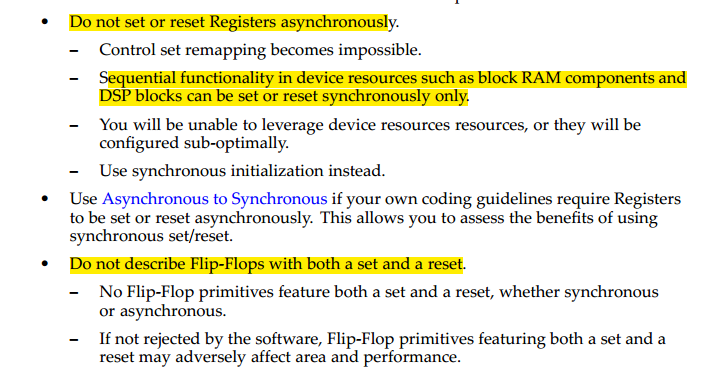

这里只想讨论一下FPGA内部的情况,官方文档推荐:

1.使用同步复位,因为像block ram、DSP等只包含同步复位或置位;

2.复位和置位不能同时使用,因为很多基本电路单元不同时包含复位和置位端,如果同时使用可能会增加面积及影响性能。

相应截图如下:

为此,我简单写了一段代码,分析一下FPGA里的情况,如果有不对的地方,还望大神指教:

always@(posedge clk or negedge rst_n or posedge set ) //or negedge rst_n or posedge set

begin

if(!rst_n)

begin

rxd_data_reg1 <= 8'h0 ;

rxd_data_reg2 <= 8'h0 ;

end

else if(set)

begin

rxd_data_reg1 <= 8'h55 ;

rxd_data_reg2 <= 8'h55 ;

end

else

begin

if(rxd_flag)

begin

rxd_data_reg1 <= rxd_data ;

rxd_data_reg2 <= rxd_data_reg1 ;

end

else

begin

rxd_data_reg1 <= rxd_data_reg1 ;

rxd_data_reg2 <= rxd_data_reg2 ;

end

end

end

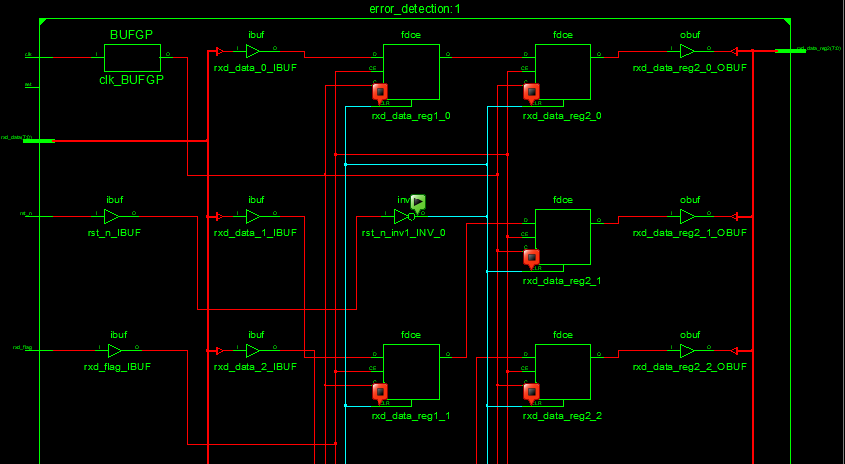

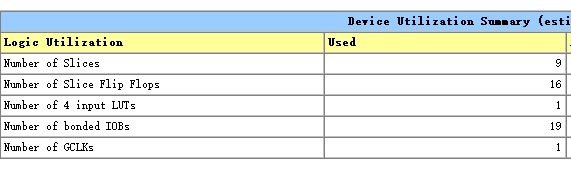

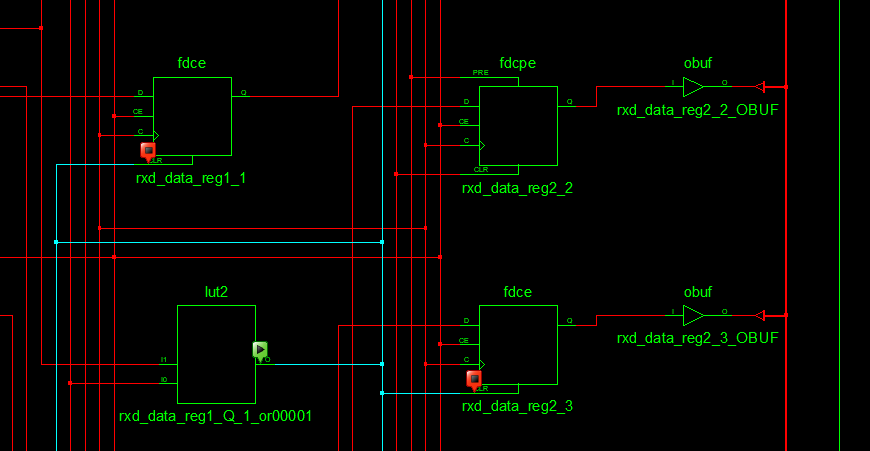

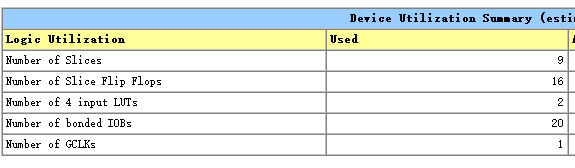

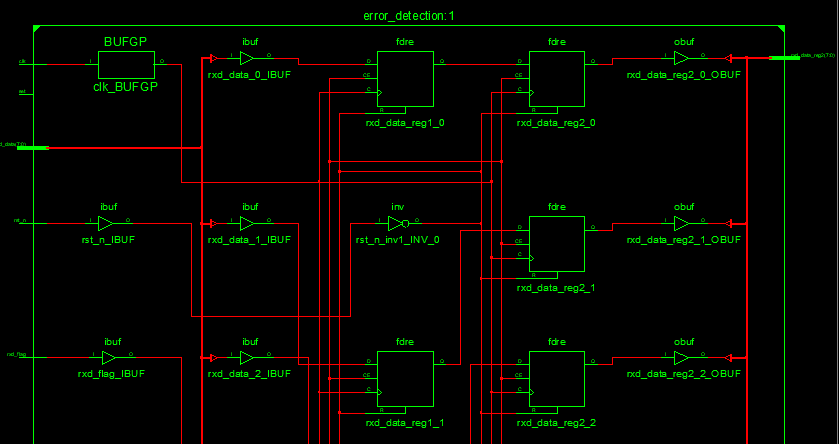

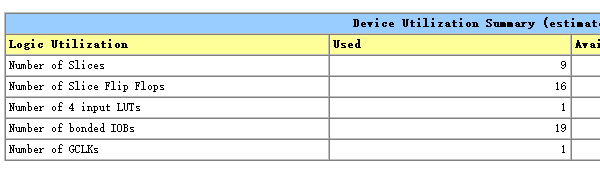

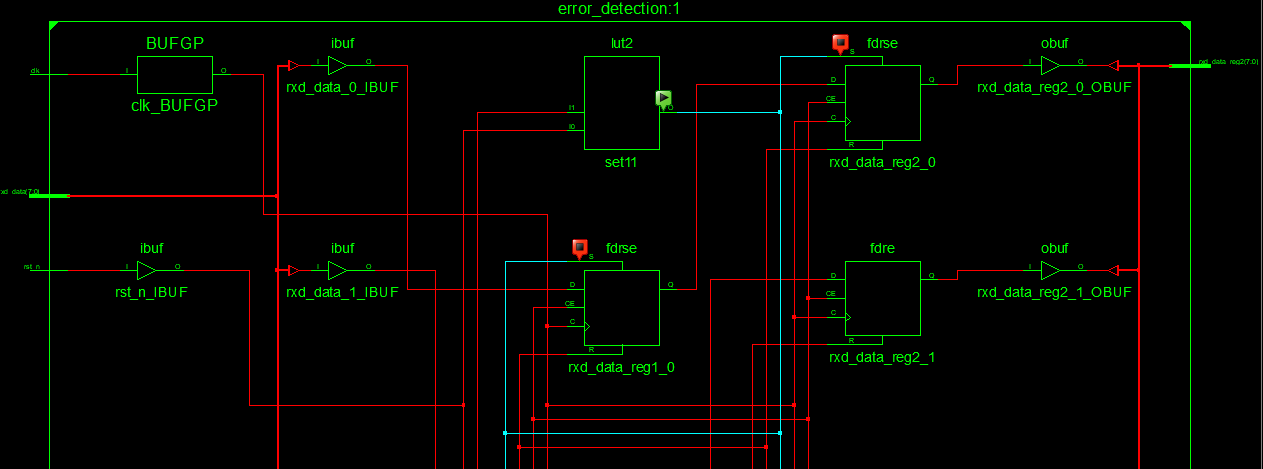

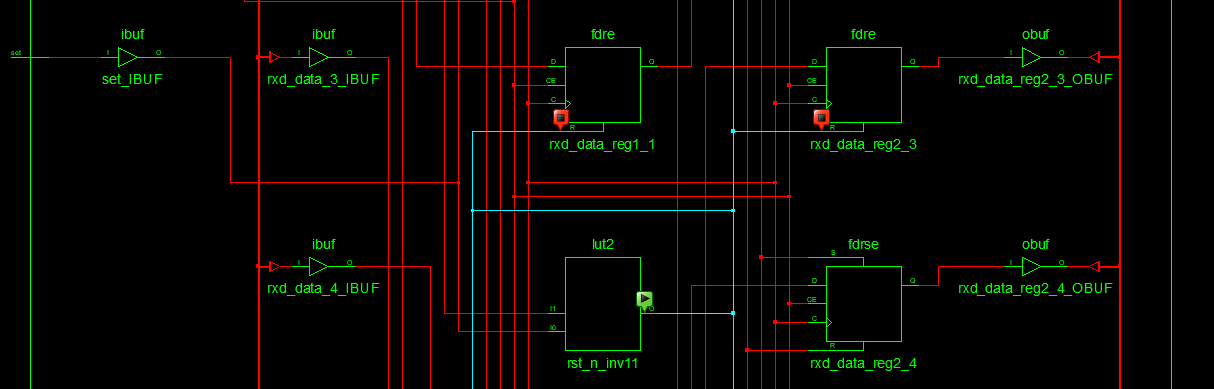

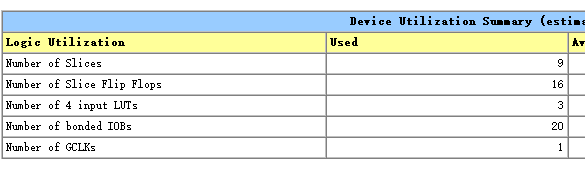

下面贴出相应的RTL原理图及资源报告:

1.异步复位:全部使用FDCE

2.异步复位置位:部分使用FDCPE,比异步复位多用一个LUT

3.同步复位:全部使用FDRE,资源与异步复位一致

4.同步复位置位:部分使用FDRSE,比异步复位多用两个LUT

总结及问题:

1.同时使用复位和置位会增加面积;

2.对于同步复位和异步复位,个人推荐异步复位同步化,该复位也可直接共block ram及DSP等模块使用;

3.对于不同型号的FPGA,综合出来的原理图及资源可能是不一样的,但都能体现出类似差异。

本文探讨了同步复位与异步复位的选择,并对比了复位与置位的同时使用情况。通过实验验证,发现同步复位更适合blockram和DSP模块,而异步复位同步化则有助于减少资源消耗。

本文探讨了同步复位与异步复位的选择,并对比了复位与置位的同时使用情况。通过实验验证,发现同步复位更适合blockram和DSP模块,而异步复位同步化则有助于减少资源消耗。

1296

1296

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?