目录

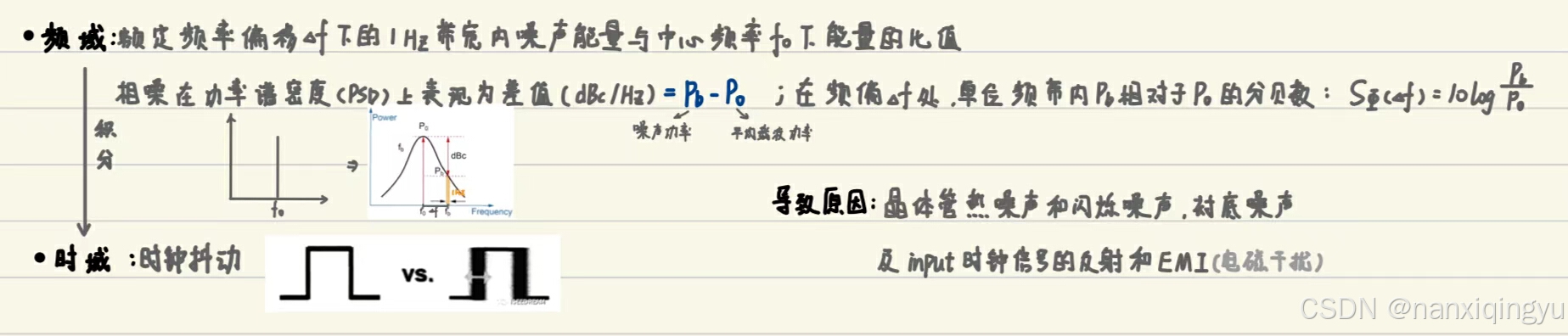

相噪定义:

一、PLL中噪声源的组成

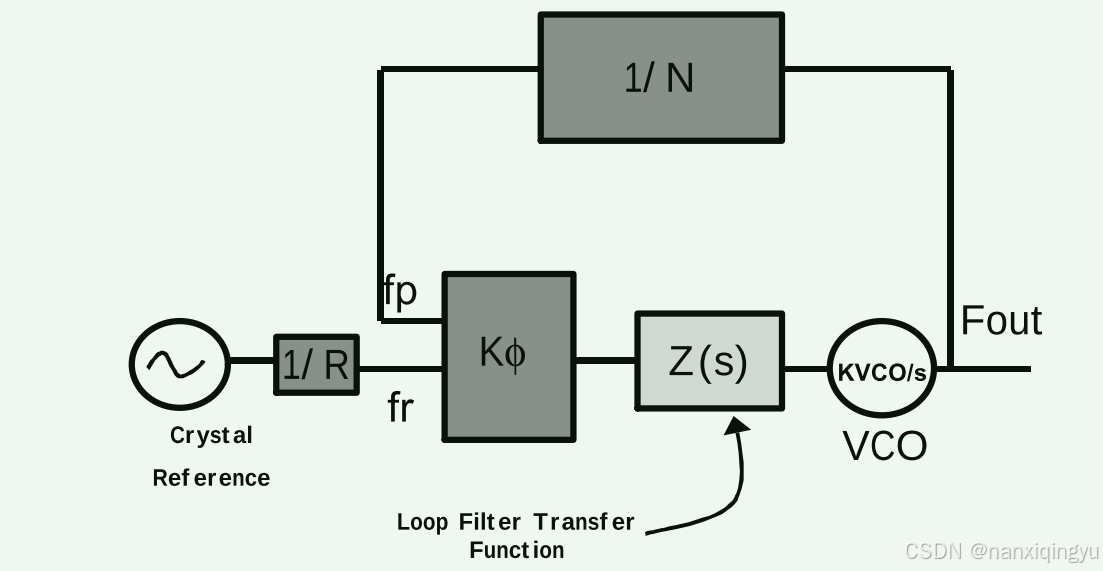

一个基本的PLL结构如下图所示,主要由:R计数器,检鉴频鉴相器,环路滤波,VCO,N计数器组成,而这些结构以及提供参考频率的晶振都会对系统引入噪声,都称为噪声源。同时噪声被分为近端/带内噪声和远端/带外噪声:

至于如何区分带内和带外噪声,我们从各结构的传递函数入手。已知PLL系统的闭环传递数:

也可以写成 ,其中:

(开环传递函数),

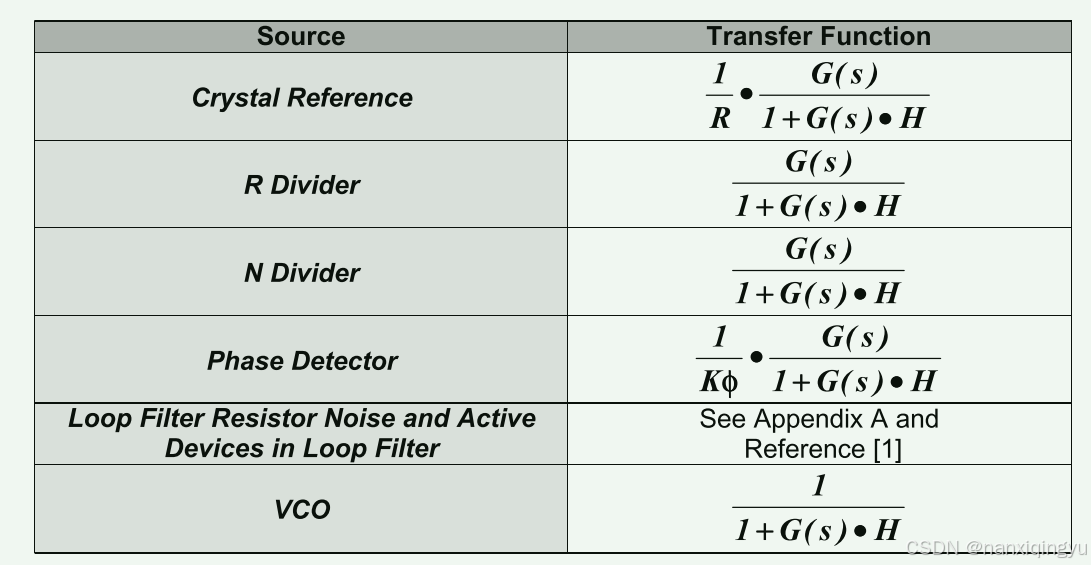

由此各噪声源的传递函数如下表所示:

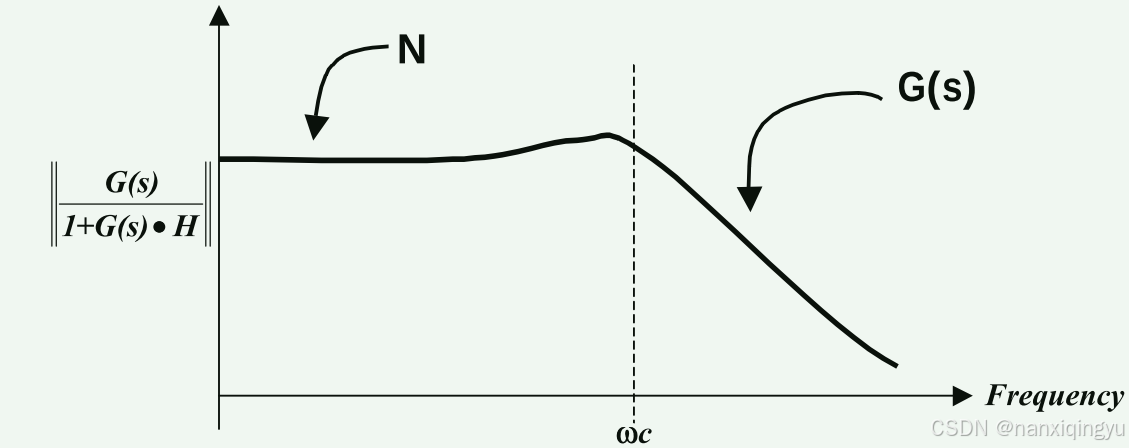

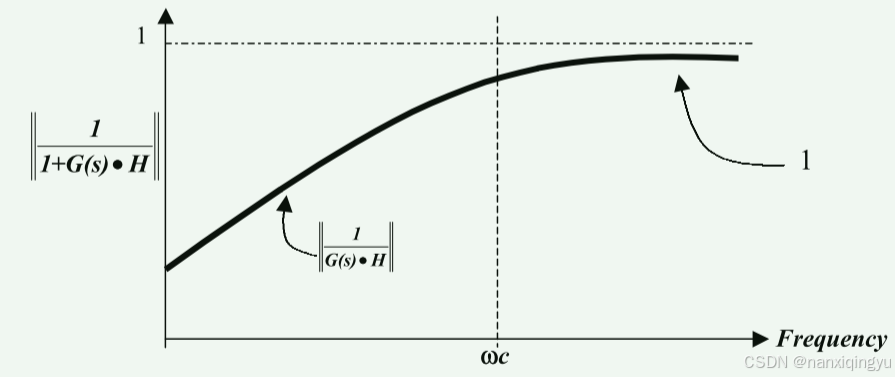

如果在表中标记的源处引入噪声源,则该噪声乘以对应的传递函数。注意:晶体噪声乘以1/R的系数,相位检测器乘以1/Kφ的系数。显然,鉴相器、N分频器、R分频器和晶体噪声的传递函数都包含一个公因子:,由于G(s)在

中单调递减(

是环路滤波带宽),所以

主要在的带内影响更大,所以鉴相器、N分频器、R分频器和晶振都为近端噪声源

同理,VCO噪声乘的是,

主要在的带内影响更大,所以VCO为远端噪声源

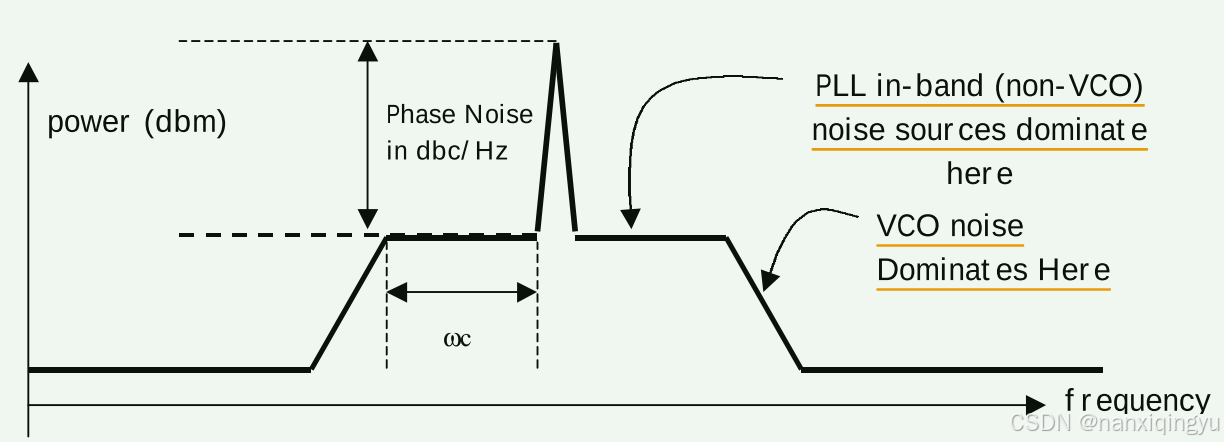

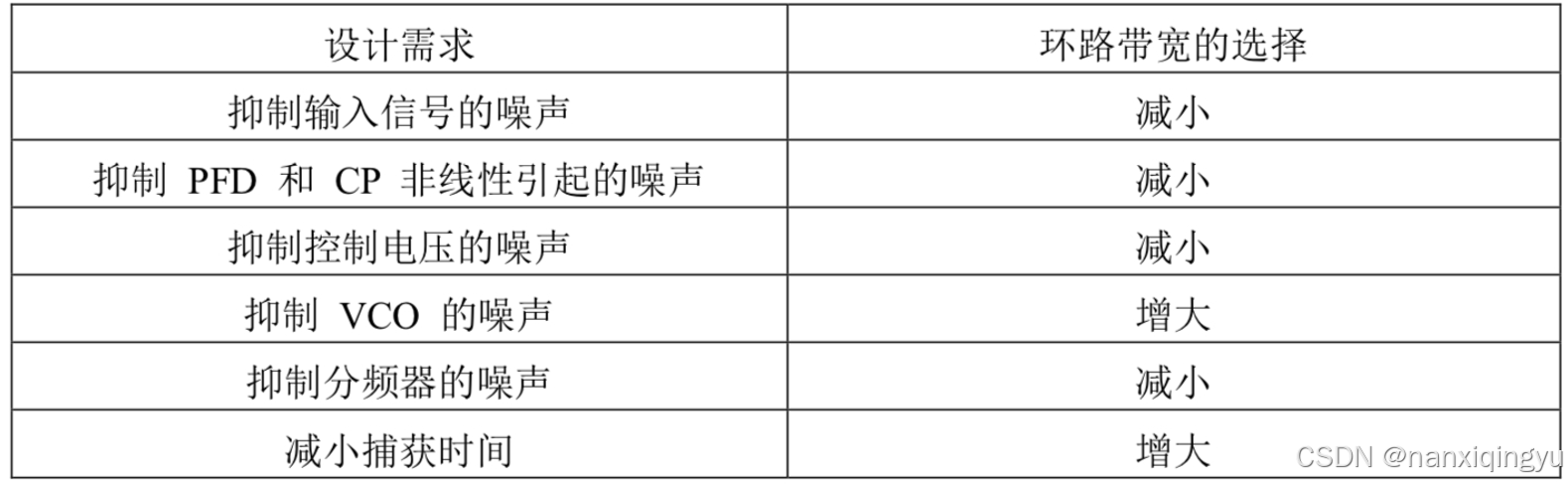

综上所述,环路滤波器对鉴相器、N分频器、R分频器和晶振噪声呈低通,对VCO噪声呈高通,因此环路滤波带宽对在近端噪声和远端噪声的滤除效果上是矛盾的,既不能太宽也不能太窄(如下图所示),一般取10-20分之一的参考带宽。

二、近端噪声源分析

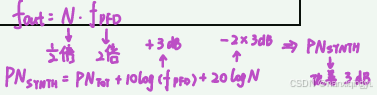

环路带宽内,VCO噪声贡献很小,其他的噪声源在带内都要乘以N(因为时,

),且是以噪声电压的形式表现,因此噪声功率与N²成比例,换算成dB为20log(N²)。同时相频噪声也是主要的噪声源,与鉴相频率

成比例。然而,鉴相频率与N成反比 (因为

),因此,鉴相器产生的噪声按照10log(N)衰减。

1、固定输出频率下近端相噪

由此可得,固定输出频率下近端相噪由传递函数引起的20log(N)噪声和鉴相器噪声引起的10log(N)噪声衰减相结合,对相位噪声的净影响为10log(N)。

以上解释对应了芯片手册给出的噪声公式

2、一般情况下近端相噪预测

分频器、晶振基准电压源和VCO对带内相位噪声产生影响,但这些噪声通常主要由鉴相器的噪声决定。由于相位检测器噪声取决于鉴相频率,因此针对1 Hz鉴相频率的相位检测器噪声理论上是什么进行了归一化。近端相噪为:

ps:以上相位噪声计算仅适用于PLL的环路带宽内。在环路带宽之外,相位噪声乘以闭环传递函数,该函数可近似为杂散增益。

三、其它可能影响相噪的因素

1、带内VCO相位噪声贡献

一般VCO对带内相噪的影响可忽略,担当环路带宽较窄或VCO噪声太大时,也会对带相噪产生影响;

2、低电荷泵增益相位噪声

芯片手册中给出的预测相噪适用于以最高电荷泵增益工作的锁相环,如果不是这种情况,那么相位噪声可能会降低。 一个粗略的经验法则是:低于1 mA的电荷泵增益对相位噪声的影响很小;但高于1 mA,电荷泵增益确实影响相位噪声;

3、双PLL

在双通道PLL中,最佳相位噪声性能是PLL的另一端未使用、关断且未连接VCO时的性能。如果是这种情况,那么这将导致比芯片手册预测的相噪改善2 dB。若两个PLL通道都输出,且输出频率越接近,相位噪声退化越严重。

4、噪声晶体参考

如果晶体参考有噪声,则可能不是电荷泵噪声占主导地位。晶体噪声会除以R,再乘以N。一种观察信号发生器是否噪声过大的方法是将频率和R值加倍,如果相位噪声减小,则表明信号发生器噪声占主导地位。

5、 电阻噪声(热噪声)

通常情况下,环路带宽内电阻噪声的贡献可以忽略不计。然而在距离载波较远的偏移量处、电阻R3较大的情况下的近端,这种噪声贡献可能更为显著。如果环路滤波器中的电阻减小,则电阻噪声相位噪声的贡献减小。

6、 输入灵敏度冲突问题

VCO或晶体功率水平不足以驱动计数器时、高频VCO引脚匹配问题等灵敏度问题都会产生相噪,同时(也有但是很少)PLL输入缓冲器产生相位噪声,对于这些锁相环,需要更高的晶体振荡器驱动电平才能获得最佳性能。

7、频谱分析仪校正系数未被考虑

1514

1514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?