第6章 用于宽带DSM的连续时间 MASH架构

柴田一、董云志、杨文华和理查德·施赖尔

6.1 引言:用于通信应用的宽带模数转换器

连续时间†模数转换器广泛应用于各种现代无线通信系统的射频信号链中。

连续时间†模数转换器不仅对输入信号进行数字化,还提供过采样和固有抗混叠等额外优势。这些附加优势降低了滤波要求,简化了射频信号链。由于连续时间转换器中的优化电路模块在满足给定噪声要求的情况下比其离散时间对应模块功耗更低,因此采用连续时间†模数转换器的射频系统也实现了更低的功耗。

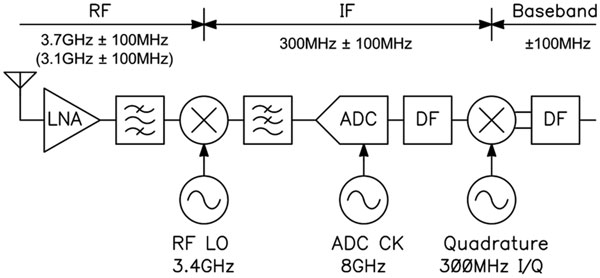

在蜂窝基站等高性能射频应用中,通常采用如(图6.1)所示的中频(IF)采样无线电架构,以避免正交匹配问题。系统的中频通常位于高于1.5倍射频带宽的位置,以避免下变频后的中频信号的二次谐波落入带内而产生干扰。对于LTE应用,需要高达200MHz的带宽。因此中频需设置在300MHz以上,信号范围在中频周围跨度达˙100兆赫。若在此应用中采用低通†模数转换器,该模数转换器需要实现超过400兆赫的带宽。

在基站射频应用中,模数转换器的功耗主要受限于热考虑因素,因为发射机的功耗远高于接收机。由于基站设计的趋势是包含多个接收机(用于分集),几瓦的集成电路功率预算导致模数转换器的功率目标低于500毫瓦。因此,模数转换器设计者的任务是设计一种低噪声、低失真和高动态范围的模数转换器,在不超过500毫瓦功耗的情况下对超过400兆赫的带宽进行数字化。

过采样ADC的带宽由下式给出

$$

BW = \frac{f_S}{2 \cdot OSR}

$$

其中OSR为过采样率,$f_S$为采样频率,BW为†模数转换器[1]的原始带宽。最大时钟频率受限于量化器中比较器的再生时间常数以及从量化器到反馈DAC的逻辑延迟。[2]纳米CMOS工艺技术使得连续时间†模数转换器能够在GHz范围内的时钟频率下工作[3–6]。在28纳米CMOS工艺中,可实现4皮秒再生时间常数,支持约8吉赫的最大时钟频率。因此,为了在8吉赫时钟频率下实现超过400兆赫的带宽,宽带无线射频应用需要满足OSRD8的要求[6]。

6.2 背景:高效能模数转换器

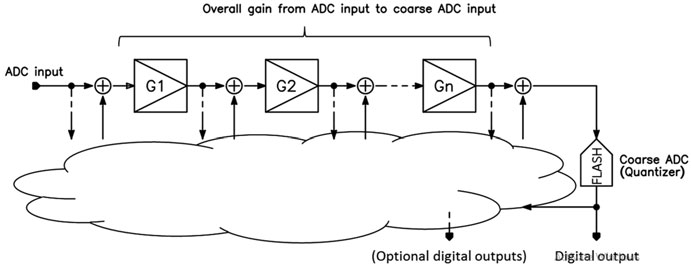

典型的高分辨率ADC系统由级联的增益级和随后的粗略ADC(量化器)组成,如图6.2所示。最终粗ADC的量化噪声功率取决于满量程、位数

位数和过采样率。从ADC输入到最终粗ADC的总增益G1G2 Gn DQGn,以及粗略ADC的量化噪声决定了整个模数转换器的输入参考量化噪声。在典型的高分辨率模数转换器中,需要超过40分贝的总增益。为了使后续论述更简单,我们假设所有增益级允许的最大输入和输出信号电平相等。每个增益级可能具有额外的反馈或前馈路径,以防止增益级发生饱和。

一种高分辨率模数转换器的例子是流水线模数转换器。假设五个增益级,每个具有 4增益,串联连接,并且最终的模数转换器具有4位分辨率。在这种情况下,总增益为 $4^5 = 60$分贝,将量化噪声抑制60分贝,当量化噪声折算到输入端时,提供额外10位。因此,整个模数转换器实现10加4等于14位分辨率。

同样的论证也适用于†模数转换器。对于†模数转换器,总增益是频率相关的,表示为传递函数L0,而反馈路径[1]的频率相关增益则用传递函数L1表示。为了简化起见,假设L0 DL1 DL。为了保持†环路的稳定性,L必须在接近$f_S/2$时将其增益降低到0分贝以下。然而,由于感兴趣带宽为$BW = f_s/(2 \cdot OSR)$,因此最重要的参数是$jL1(BW)j$,即带内区域边缘处的环路增益。

现在让我们讨论此类模数转换器系统的功率效率。每一级增益级的功耗与其电导水平成正比。每一级的热噪声功率谱密度与阻抗水平成正比。因此,各级的最优功率分配是在每级增益为pT时,将阻抗水平按T进行缩放。(该论证假设所有级的比例常数相同。)这也表明,低功耗低噪声系统需要更高的级增益T,尤其是在第一级。较高的增益还有助于减小后端非理想性(如失真)的影响。

对于† ADC,需要考虑的第一级增益是在f D带宽处的第一级增益。该增益可用作评估给定过采样率下ADC架构功率效率的指标。我们将在后续章节中基于此论述讨论† ADC系统的功率效率。

6.3 用于低过采样率应用的单环†模数转换器

如第6.1节所述,连续时间†模数转换器非常适合无线射频应用。然而,†模数转换器系统属于过采样系统,由于环路增益必须在$f_s/2$以下降低至0分贝,因此本质上是窄带的。因此,在宽带射频应用中,†系统的挑战在于保持通带边缘处的模数转换器功率效率,并使用高频时钟驱动调制器。本文从这一角度回顾了采用反馈和前馈环路滤波器结构的传统†模数转换器,并讨论了这些传统方法的局限性。

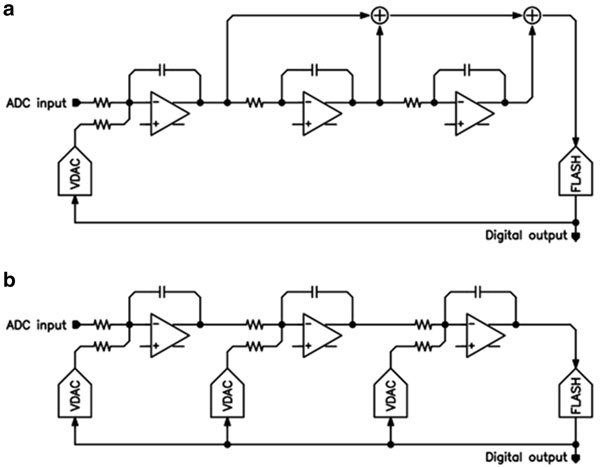

图6.3展示了传统的三阶†模数转换器;图6.3a是前馈†模数转换器,图6.3b是一个反馈†模数转换器。在这些模数转换器中,三个级联连接的积分器提供了从ADC输入到末级量化器的总增益,如第6.2节所述。

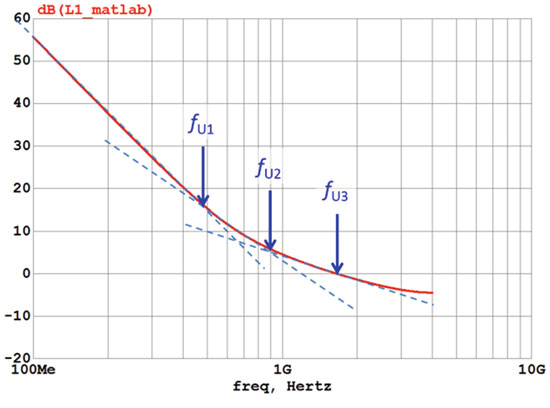

该环路增益L1(z)的整体形状可通过DeltaSigma工具箱[7]计算得出,并在图 6.4中展示,假设带宽D500MHz,OSRD8,$f_s = 8$吉赫,且jjHjj1 D2.5,未进行噪声传递函数零点优化。如图所示,L1(z)在带宽处具有16dB增益。

由Delta Sigma工具箱计算的三阶†模数转换器。 f U1、f U2和f U3是内部积分器的单位增益频率)

由Delta Sigma工具箱计算的三阶†模数转换器。 f U1、f U2和f U3是内部积分器的单位增益频率)

表6.1显示了在动态范围和其他缩放之后,环路滤波器中每个积分器在反馈和前馈结构下的单位增益频率。表中还给出了在带宽处的增益。如表所示,反馈结构的第一级增益低于0分贝,而前馈结构为11分贝。这种差异也可以通过图L1中图6.4的形状直观理解。在反馈结构中,前端级构成三阶路径。因此,第一级积分器设计为环路滤波器三个积分器中单位增益频率最低的。而在前馈结构中,第一级积分器构成一阶路径,因此第一级积分器具有三个积分器中最高的单位增益频率。

| 三阶反馈 | 三阶前馈 | |

|---|---|---|

| 第一级单位增益频率 | 169兆赫 | 1.73吉赫 |

| 带边第一级增益(OSR=8) | 9 dB | 11分贝 |

| STF峰值 | 0 dB | 13分贝 |

根据第6.2节中关于效率的论述,每一级都需要具有T> 0 dB的增益,尤其是在第一级。传统反馈的增益分配†模数转换器违背了这一要求。因此,传统反馈†模数转换器不适用于需要OSR 8的应用。

前馈结构基于第一级增益论证具有功耗高效特性。然而,如文献[4, 8], 所述,前馈架构本质上存在STF峰值。在无线通信应用中,最具挑战性的使用场景之一是带外阻塞场景。在此场景下,STF峰值需要在射频链中增加额外滤波或进行满量程放宽,从而限制了带内信号的动态范围。这两种修改都削弱了连续时间架构所带来的简化射频架构的优势。†模数转换器。基于这些论点,我们得出结论:传统的单环路†模数转换器不适用于过采样率 8的宽带射频系统。

6.4 连续时间多级噪声整形模数转换器用于低过采样率应用

我们指出,对于宽带无线通信系统而言,采用OSR=8的传统单环†模数转换器效率低下。多环或称为多级噪声整形(MASH)的模数转换器是一种†模数转换器,其内部的子ADC或子†模数转换器通过残差生成级以串联方式连接[5, 6, 8–11]。

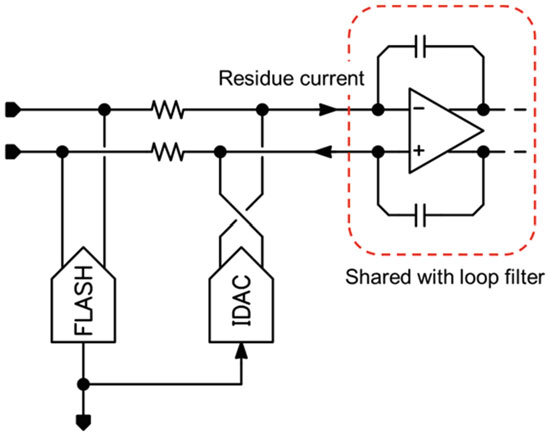

残差生成级的简化框图如图6.5所示。输入信号被分为两条路径:一条直接进入加法器,另一条则经过闪存型ADC、粗DAC后连接至加法器。通过这种结构,加法器将原始输入信号减去量化后的输入信号,从而产生输入信号与量化信号之间的连续时间差值作为残差。当两条路径设计得相互匹配时,残差的主要成分即为粗略ADC的量化噪声。在理想情况下,当输入信号频率远小于采样频率时,残差幅度受限于$(1/M) VFS$,其中M 是粗略ADC的量化电平数,VFS 是粗略ADC的满量程。然而在实际情况下,残差幅度可能大于此限值。因此我们定义一个抵消因子k<M,使得残差的上限为$(VFS/k)$。

由于信号电平降低了k倍,因此可以添加一个增益为k的增益模块,而不会使处理的信号饱和,如图6.5所示。因此,从模数转换器输入到图6.2中所示的最终粗略ADC的总增益可以通过抵消增益k来提高。

残差消除级和(b) 残差消除波形)

残差消除级和(b) 残差消除波形)

残差生成电路可以使用传统†模数转换器系统中的常规电路模块来实现,包括一个粗略ADC、一个粗DAC,以及由有源RC滤波器中的运算放大器提供的求和节点,如图 6.6所示。

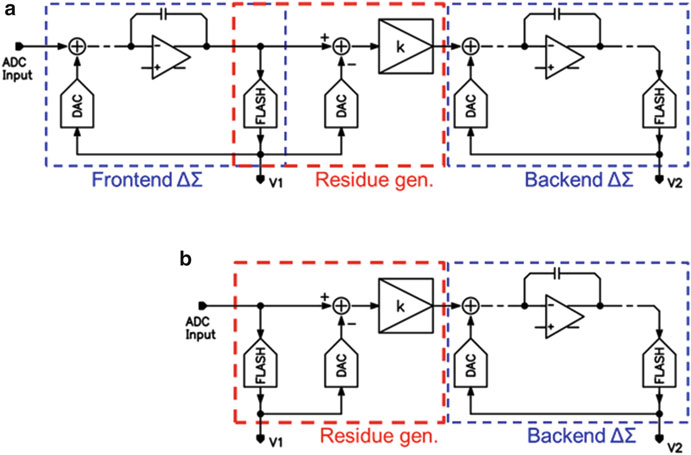

示例MASHADC系统如图6.7所示。6.7a 是一种传统MASHADC,其中前端† ADC和后端†ADC通过残差生成电路连接。从ADC输入到最终粗ADC的总增益可以提高,原因有两个。第一个原因是上述讨论的残差抵消增益k,该增益在频率上可以是平坦增益。第二个原因是MASH结构提供的额外低阶通路增益。在单环†ADC中,可以根据需要插入增益级,但附加级的带宽必须降低以满足稳定性要求。而在MASH结构中,附加增益级可以

位于不同的环路中,以便在从ADC输入到末级量化器的增益链中增加低阶宽带宽增益级。因此,这些额外的级数提高了频带边缘的增益。

图6.7b所示的MASHADC结构是一种0‐x MASHADC,其由残差生成级后接一个传统的†模数转换器[5, 12–15]组成。在此配置中,提供给†模数转换器的信号幅度被抵消因子k减小,从而可使后端†模数转换器的第一级增益提高k倍。因此,该配置也增加了从ADC输入到末级量化器的总增益。

在图6.7的多级噪声整形示例中,图示为了说明目的以冗余方式绘制。在实际实现中,增益模块k可以通过缩放后端†模数转换器中的第一数模转换器和第一积分电容,将其合并到后端†模数转换器中。

在第6.2节中,我们讨论了如何根据带宽下的第一级增益来估算模数转换器功率效率。接下来,我们以相同的方式研究MASHADC的功率效率。传统MASH的第一级增益与传统† ADC相同,因为前端ADC与传统的单环†ADC相同。但在MASH结构中,可以通过级联低阶† ADC来实现所需的总增益,其中每一级增益在带宽下仍可提供高于0分贝的增益。因此,采用级联低阶† ADC的MASHADC可以作为实现OSRD8的宽带模数转换器的候选方案。同样,0‐x MASHADC的第一积分器增益可以高于传统†ADC,因为后端ADC提供的信号幅度被抵消因子k所降低。

0‐x MASH的其他有趣特性包括实现成本和热噪声影响。0‐x MASH需要四个额外的模块:粗略ADC、粗DAC、加法器和增益模块。然而,加法器和增益模块k可以合并到后端†模数转换器中。此外,该DAC可以与传统†模数转换器中的第一数模转换器相同。因此,剩余的额外模块仅为残差生成级中的闪存型ADC和后端中的数模转换器。†模数转换器。然而,由于后端ADC中的数模转换器是按比例缩小的,其功耗仅为第一数模转换器功耗的一小部分。此外,额外的闪存型ADC可以替换为更高效的SAR或基于VCO的ADC,因此0‐x架构相关的功耗代价可能很小。因此,传统MASH和0‐x MASH可用于OSRD8应用,且我们预计0‐x MASH将更加功耗高效。

6.5 连续时间MASH†ADC中的残差生成

如第6.4节所述,连续时间MASH†模数转换器是一种由两个或更多子 ADC(通常为†模数转换器)通过连续时间残差生成电路连接而成的模数转换器。由于模数转换器的性能基本上受限于增益链中的电路,因此我们现在详细讨论残差生成电路的特性。

离散时间余数生成电路几十年来一直被用于流水线模数转换器或离散时间MASH†ADCs[10]。相比之下,连续时间MASHADCs中使用的残差生成电路在文献中尚未得到充分讨论。对于离散时间残差生成电路,在组件均为理想的情况下,残差幅度被限制在粗DAC的 ˙0.5LSB以内。然而,在连续时间残差生成中,残差幅度可能超过粗DAC的 ˙0.5LSB,原因有两个:第一个原因是主路径与抵消路径之间的传递函数失配;第二个原因是由于 DAC镜像信号所致。

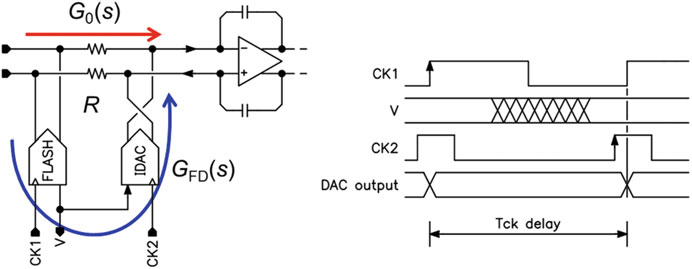

图6.8显示了一个基本余数生成电路以及闪存型DAC时序图。传递函数 G0(s)表示主路径,GFD(s)表示抵消路径。如时序图所示,数模转换器基于早一个时钟周期(TCK)的量化信号输出信号。此外,假设为非归零波形,数模转换器在整个时钟周期内输出恒定电流。因此,这两个传递函数可以表示为

$$

G_0(s) = \frac{1}{2R} \quad \text{and} \quad G_{FD}(s) = \frac{I_{FS}}{V_{FS}} \cdot \frac{1 - \exp(-T_{CK}s)}{s} \cdot \exp(-T_{CK}s)

$$

其中G0(s)和GFD(s)分别为通过电阻R和FLASH‐DAC路径的跨导。IFS和VFS分别为电流输出型DAC和闪存型ADC的满量程。满量程经过调整,以使传递函数在直流处匹配。

$$

\frac{I_{FS}}{V_{FS}} = \frac{1}{2R}

$$

利用这两个传递函数,可以写出残差误差电流

$$

I_{RES}(s) = \left[G_0(s) - G_{FD}(s)\right] V_{IN}(s)

$$

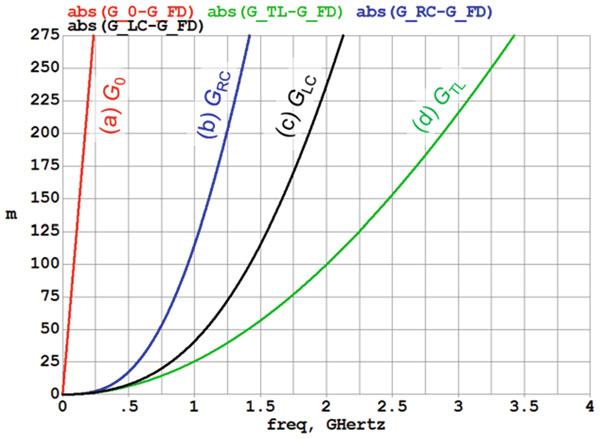

如该公式所示,即使两个传递函数在直流处的幅度匹配,残差误差电流也会随着频率的增加而增大。图6.9a绘制了归一化残差误差电流与频率的关系。如图所示,在OSRD50时,误差已达10%。在OSRD8时,误差为58%,因此即使在余数抵消级中使用了高分辨率闪存型ADC和数模转换器,抵消增益也仅限于k < 1/0.58 = 1.7。显然,在连续时间MASH型ADC中,传递函数的匹配至关重要。

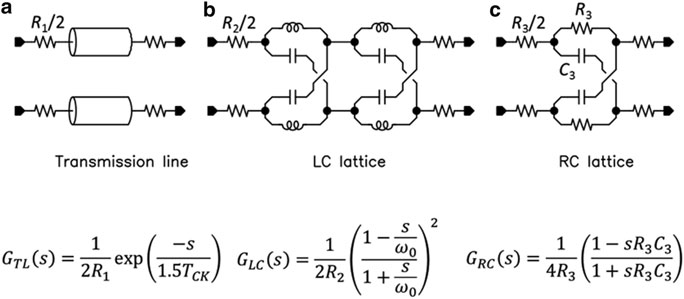

这种匹配误差可以通过在其中一个或两个传递函数中引入附加元件来减小[5, 6, 13, 16, 17]。由于数模转换器的sinc响应在过采样率D8时幅度变化小于1%,在过采样率D4时为2.5%,因此相位或延迟的匹配更为重要。由于 DAC脉冲的中间点位于0.5TCK,因此FLASH‐DAC路径的有效延迟为1.5TCK。等效相位旋转可以通过将主路径中的跨导 1/2R替换为全通网络来实现,例如:(a)终端延迟线,(b)终端LC格型延迟线,或(c)RC格型延迟线,如图 6.10所示。所有这些网络都具有恒定跨导,但会旋转其相位。也可以通过在 FLASH‐DAC路径中添加反延迟传递函数来实现匹配改善。然而,由于需要满足因果性,其频率范围受到限制[16]。

每种情况的残差误差也在图6.9中示出。如图6.9所示,传输线提供了最佳的抵消效果,因为两个传递函数的相位响应完全匹配,唯一的差异是sinc幅度差异。然而,在硅片上实现1.5TCK延迟所需的传输线走线长度为

$$

l_{TL} = 1.5 \cdot T_{CK} \cdot c / \sqrt{\epsilon_r} = 28\,\text{mm}

$$

其中c为光速,$\epsilon_r$为硅的相对介电常数。即使将走线折叠,该长度对于集成而言仍不实用。级联LC格型延迟线效果次之,在OSR=4时仍能支持k > 20。然而,由于片上电感可能受外部磁通量影响,在电路中引入此类组件会带来模数转换器前端是一个需要关注的问题。此外,实现所需值的电感器占据了较大的硅面积。因此,最具吸引力的选择是RC格型实现。采用RC格型结构时,在OSR=8时误差幅度为满量程的1.7%,仍小于4位抵消残差的1/16 = 6%。然而该误差在高频时迅速增加。在OSR=4时,抵消误差达到12%,因此对带外信号的抵消能力最终受到限制。

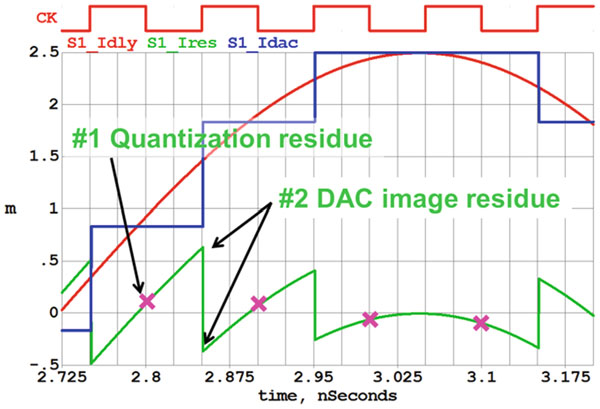

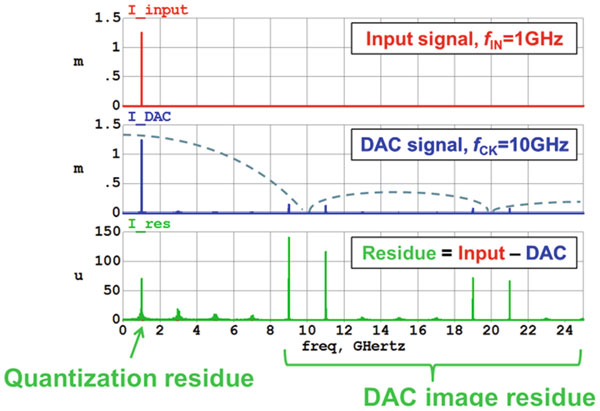

在连续时间残差生成的情况下,抵消DAC还会根据sinc(s)包络,在第二、第三及更高奈奎斯特频率处注入镜像信号。图6.11和6.12分别显示了时域和频域中的残差生成波形。在频域图中可以明显看出,仅第一奈奎斯特分量被用于抵消,而其他分量仍然存在。这些残留的镜像信号也可能限制可实现的抵消增益k。由于第二和第三奈奎斯特镜像信号遵循sinc(s)包络,当基波信号频率增加时,其幅度也随之增大。例如,当OSRD8且$f_s = 8$吉赫时,500MHz信号会在7.5和8.5GHz处产生镜像信号,每个镜像信号的幅度为基波幅度的6%。对于1GHz输入信号,镜像信号出现在7和9GHz,幅度达到基波幅度的14%。这些镜像信号的电平高于第一奈奎斯特区中的4位抵消残差电平,如图6.12所示。因此,由残差生成电路驱动的子ADC需要能够处理此类高频镜像信号。

6.6 MASH†模数转换器在28纳米CMOS中的实现

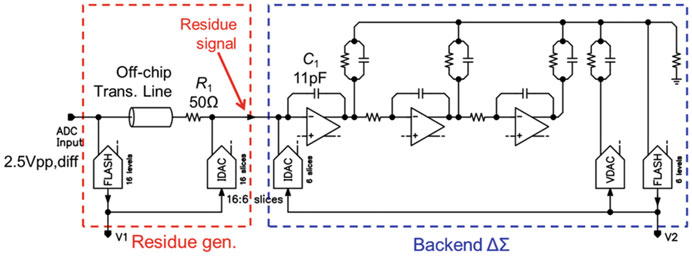

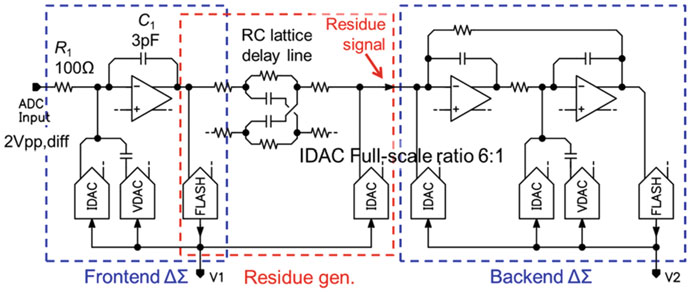

我们报道了两款在28纳米CMOS技术中实现的宽带连续时间MASHADC [5, 6]。在本节中,我们将讨论这两种ADC架构在宽带无线通信应用背景下的优缺点。两个ADC系统的简化框图如图6.13和6.14所示,架构对比总结于表6.2中。图6.13所示的第一个设计是一款0‐x MASH结构,其前端ADC采用4位FLASHADC,后端ADC采用三阶前馈†ADC(0‐3FFMASH)。该前端和后端子ADC通过一个残差生成电路连接。残差生成电路中的相位匹配网络由片外传输线构成。第二个设计是一款连续时间MASH,采用一阶† ADC作为前端,二阶反馈†模数转换器作为后端(1‐2FBMASH)。两个子ADC通过第6.5节中讨论的 RC延迟线连接。第二个设计的OSR目标是OSRD8。在此OSRD8目标下,一阶RC全通延迟网络已足够。1‐2FBMASH中的FLASHADC具有17级。

两个MASH模数转换器都通过残差生成电路来提高抵消增益。0‐3FF和 1‐2FB的抵消增益分别为16/6 ≈ 2.7 和 6。这些抵消增益的确定考虑了抵消DAC分辨率、传递函数失配以及DAC镜像信号幅度,同时还考虑了电路非理想性,例如闪存型ADC中比较器的偏移。

| 3FB† | 3FF† | 0-3FF MASH† | 1-2FB MASH† | |

|---|---|---|---|---|

| 第一级单位增益频率 第一级增益在带边(OSR=8) | 169 MHz($f_s = 8$ GHz) 9 dB | 1.73 GHz($f_s = 8$ GHz) | 1.2 GHz($f_s = 3.2$ GHz) | 1.1 GHz($f_s = 8$ GHz) |

| 11 dB | 15 dB | 6 dB | ||

| 能效 (OSR=8) | 差 | 好 | 非常好(FOM=171 dB) | 好(FOM=159 dB) |

| 抗混叠性能 | 很好 | 好 | 中等 | 好 |

| STF峰值 | 0 dB | 13 dB | 中等 | 0 dB |

| 带外阻塞鲁棒性 | 很好 | 差 | 中等 | 很好 |

在无线通信应用中,对带外阻塞信号的抗干扰能力是†ADC的重要指标。1‐2FB设计比0‐3FF设计具有更好的抗干扰能力,因为其前端†ADC还提供了低通滤波功能,而0‐3FF架构中的前端ADC不提供任何滤波功能,还会注入镜像信号。

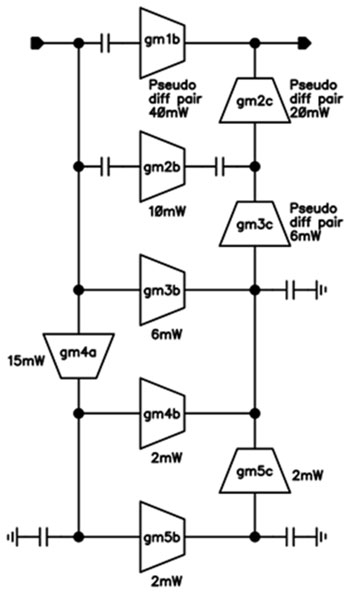

所有†模数转换器由三个主要电路模块组成:环路滤波器、量化器和数模转换器。在有源RC环路滤波器中,放大器是主要的有源电路。在1‐2FB多级噪声整形结构中,积分器中采用了一个五阶前馈放大器,如图 6.15所示。[4, 18]前馈运放设计用于满足两个相互冲突的要求,即在$f_s/2$处具有适中相移,以及在带宽处具有高增益。放大器中的低增益、高带宽一阶路径满足第一个要求。通过gm4a‐gm5b‐gm5c‐gm3c‐gm2c路径的高增益、低带宽路径满足第二个要求,从而为带内信号提供低失真操作。

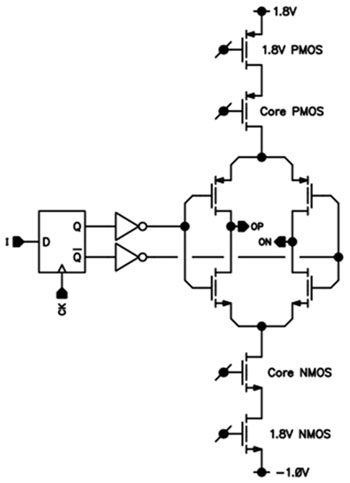

0‐3FFMASH和1‐2FBMASH中使用的数模转换器均为推挽式电流导向数模转换器 [19]。其中一个DAC切片如图6.16所示。PMOS和NMOS子 DAC由相同的数字信号驱动,以最小化热噪声被注入到给定满量程电流的求和节点。该模块的大部分电路由1.0V的核心电压供电,同时为数模转换器电流源提供额外的1.8V和1.0V电源电压,以降低其热噪声。

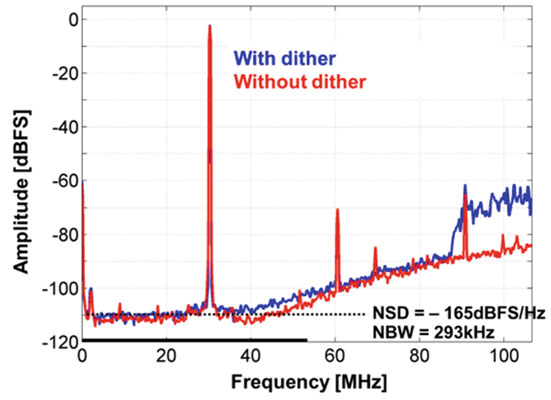

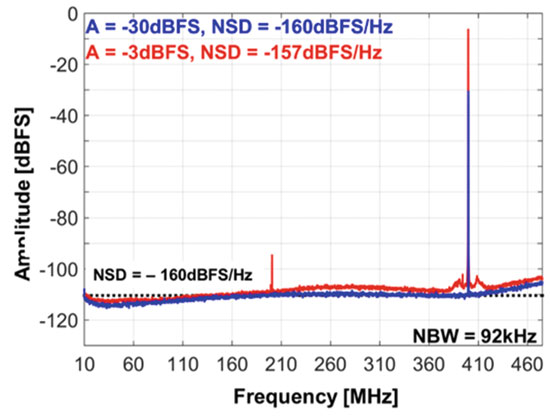

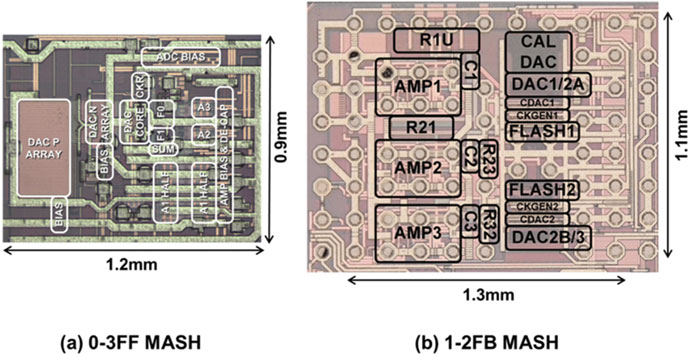

模数转换器的性能总结见表6.3。0‐3FFMASH设计和1‐2FBMASH的过采样率分别为D30和8,时钟频率分别为3.2和8吉赫。图6.17和6.18 中的单音频谱显示带宽分别为53和465MHz,噪声密度为 166和 160分贝满量程每赫兹。在这两种设计中,前端和后端ADC的数字输出流V1和V2通过数字滤波器组合,以最小化带内噪声。1‐2FB设计的性能满足第6.1节讨论的宽带高性能中频无线电应用需求。

| 0‐3FFMASH[5] | 1‐2FBMASH[6] | |

|---|---|---|

| 工艺技术 | 28纳米CMOS | 28纳米CMOS |

| 有源面积 | 0.9mm² | 1.4mm² |

| 电源电压 | 0.9V/1.8/1.0V | ˙1 V/1.8V |

| 功率(P) | 235mW | 890mW |

| 采样率($f_s$) | 3.2GHz | 8吉赫 |

| 带宽(BW) | 53MHz(OSR=30) | 465MHz(OSR=8.6) |

| 输入满量程 | 2.5Vp‐p,差分 4.3纳伏每平方根赫兹(166分贝满量程每赫兹) | 2.0Vp‐p,差分 7.1纳伏每平方根赫兹(160分贝满量程每赫兹) |

| 平均噪声谱密度(小信号) | ||

| 动态范围(DR) | 87dB | 72分贝 |

| 峰值信噪比 | 83分贝 | 68分贝 |

| 峰值信噪失真比 | 70分贝 | 67dB |

| FOMDDR C10log10(带宽效率) | 171dB | 159dB |

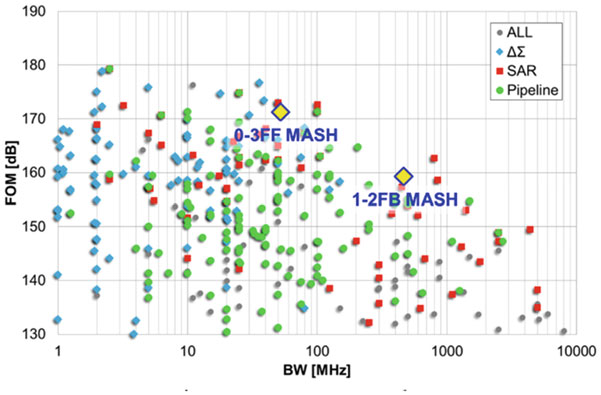

芯片照片如图6.19所示。每个模数转换器的功率效率可通过热噪声优值 FOM = DDR + 10 log10(BW/P)[1]进行量化。使用已发表的模数转换器数据点绘制的FOM图如图6.20[20]所示。0‐3FFMASH设计实现了171dB的FOMD,在带宽达到BW =50MHz的转换器中具有较强的竞争力。1‐2FBMASH在本文撰写时发布的†模数转换器中实现了最宽的带宽。然而,由于较高的时钟频率和较低效率的ADC架构,该模数转换器的FOM降至159dB。

6.7 结论

在宽带无线通信应用中采用连续时间MASH†模数转换器的原因已进行了讨论。在过采样率小于十的宽带应用中,从效率角度来看,多级噪声整形模数转换器结构是不可避免的。多级噪声整形架构需要连续时间残差生成电路,并详细讨论了该电路的重要特性。在宽带无线电接收机的背景下,比较了两种宽带MASHADC实现方案,结果表明,可以设计出满足高性能无线电要求的MASHADC,其中频为300MHz、带宽为200MHz,同时实现较高的功率效率。

742

742

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?