创建项目

因为这是第一次写Verilog编程的博客,所以我把创建项目的步骤也写下:

我用的是Vivado.2019.1版本:

-

在Quick Start界面点击Create Project

-

在接下来的界面一直点击next,不用修改,直到这个界面,可以输入项目名称以及地址

-

点击next,这个界面注意要把方框Do notxxxx的勾打上

-

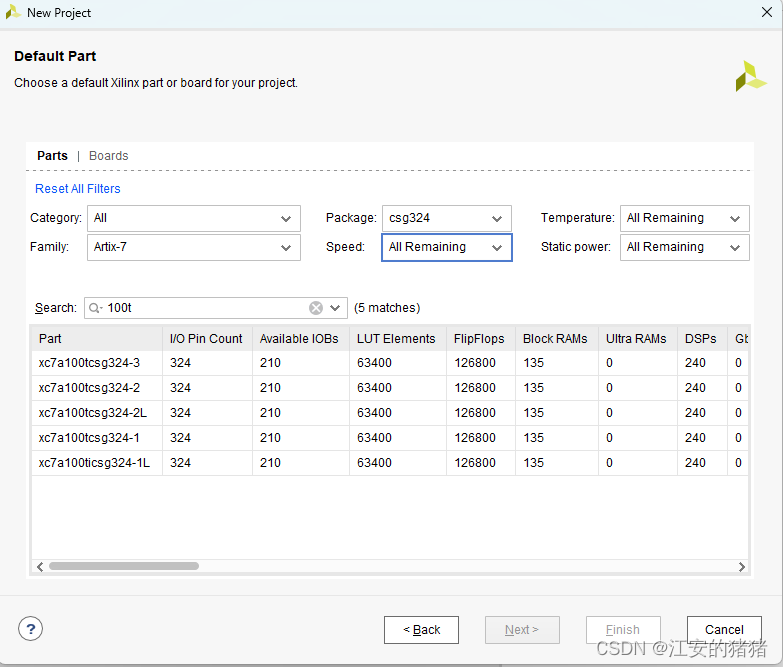

下一个界面选择FPGA板子的型号,一般在板子正中央会写,我这里的型号是ARTIX-7 100T CSG324版本

首先在Family界面找到ARTIX-7,然后在package找到csg324,再直接搜索100t,出现的结果随便选一个, 对于新手问题不大。

5. 然后Finish就完成了。创建编程文件

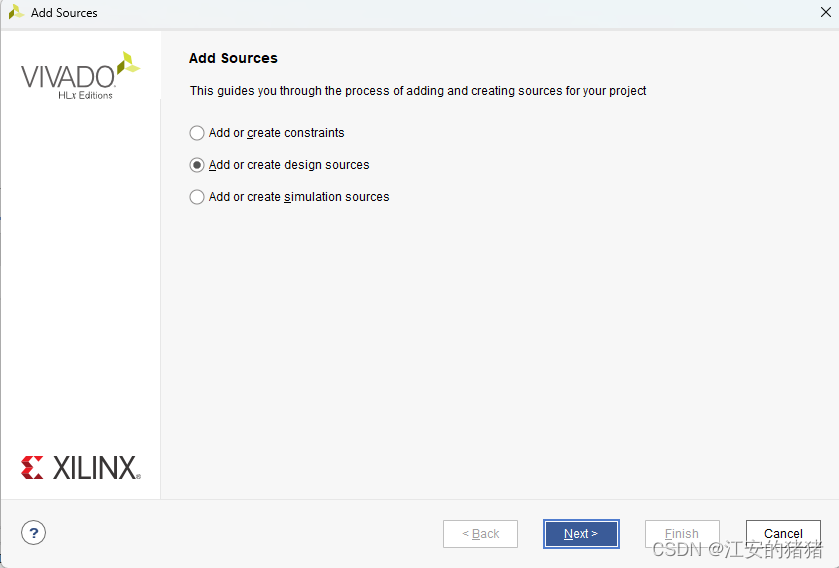

1.右键constraints(或者design sources),选择add sources

2.选择Add or Create design sources

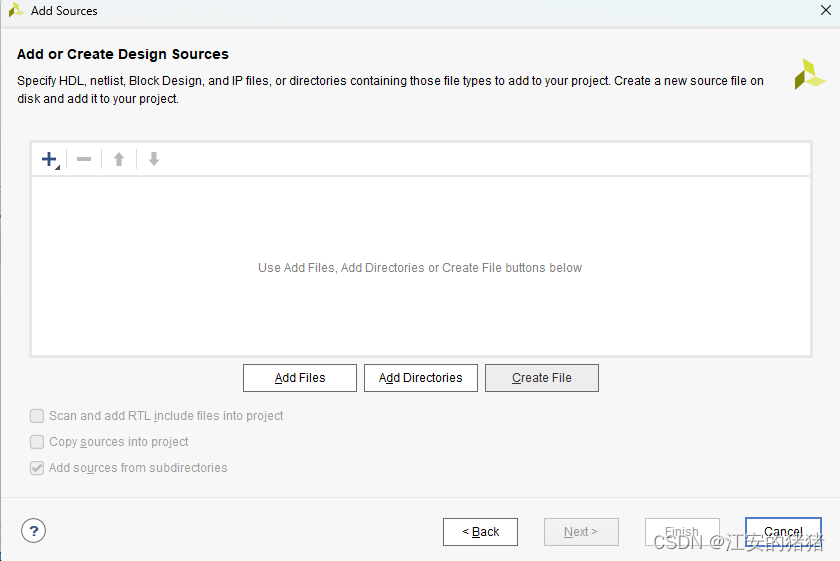

3.选择create file

4.随便输入个名字

5.然后所有的选项直接finish+ok,结束;双击蓝色圆圈的文件就可以开始编程了

编程

编写分频器模块

由于该芯片提供的原始频率为100MHz,这过于高了,所以我们需要分频器将它分频为2Hz,原理很简单,可以理解为让一个counter在原始的时钟下运行24999999次后,就让新的时钟反向,在后面的时钟我们只使用这个新的时钟就可以实现2Hz的目标。

module clk_100MHz_2_2Hz(

input wire clk_in,//原始频率

input wire reset,//复位信号

output reg clk_out//输出频率

);

reg [31:0]counter;//32位计数器,计数到24999999返回

always@(posedge clk_in or posedge reset)//在clk_in或者_reset的上升沿无限次执行

begin

if(reset)//复位信号时,全部清零

begin

counter<=32'd0;

clk_out<=1'b0;

end

else

begin

if(counter==32'd24999999)//counter到24999999,直接复位,同时clkout反向

begin

counter<=32'd0;

clk_out<=~clk_out;

end

else//如果counter没到,那就直接counter+1

begin

counter<=counter+1;

end

end

end

endmodule

编写计数器模块

计数器模块就比较简单了,我们有一个counter计数,到指定模数就返回,同时设置一个light标志进位

module counter_1(

input wire clk,//分频时钟信号

input wire reset,//复位信号

output reg light,//进位信号

output reg [3:0] counter//计数器

);

always@(posedge clk or posedge reset)

begin

if(reset)//复位时全部清零

begin

counter<=4'd0;

light<=1'b0;

end

else

begin

if(counter==4'd9)//到头来就复位

begin

counter<=4'd0;

light<=1'b1;//进位信号亮起

end

else//没到头就+1

begin

counter<=counter+1;

light<=1'b0;

end

end

end

endmodule

顶层模块

顶层模块主要干两件事情,将以上两个模块实例化,并且设置数码管亮起

module top_module(

input wire clk_in,

input wire reset,

output wire clk_out,

output reg light_out,

output reg [6:0]c

);

wire light;

wire [3:0] internal_counter;

//实例化分频器

clk_100MHz_2_2Hz clk_div_inst(

.clk_in(clk_in),

.reset(reset),

.clk_out(clk_out)

);

//实例化计数器

counter_1 counter_1_inst(

.clk(clk_out),

.reset(reset),

.light(light),

.counter(internal_counter)

);

//将light的值赋给light_out

always@(posedge clk_out)

begin

light_out<=light;

end

//数码管设置

always@(posedge clk_out or posedge reset)

begin

if(reset)

begin

c<=7'b0000000;//复位信号时全亮(低电平有效)

end

else begin

case(internal_counter)//设置10个不同数字时的数码管亮编码

4'd0:c<=7'b1000000;

4'd1:c<=7'b1111001;

4'd2:c<=7'b0100100;

4'd3:c<=7'b0110000;

4'd4:c<=7'b0011001;

4'd5:c<=7'b0010010;

4'd6:c<=7'b0000010;

4'd7:c<=7'b1111000;

4'd8:c<=7'b0000000;

4'd9:c<=7'b0010000;

default:c<=7'b0000000;

endcase

end

end

endmodule

之后进行保存即可

后续步骤

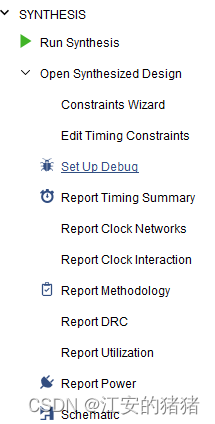

- 运行Synthesis,点击即可,只要没有error就不用管。

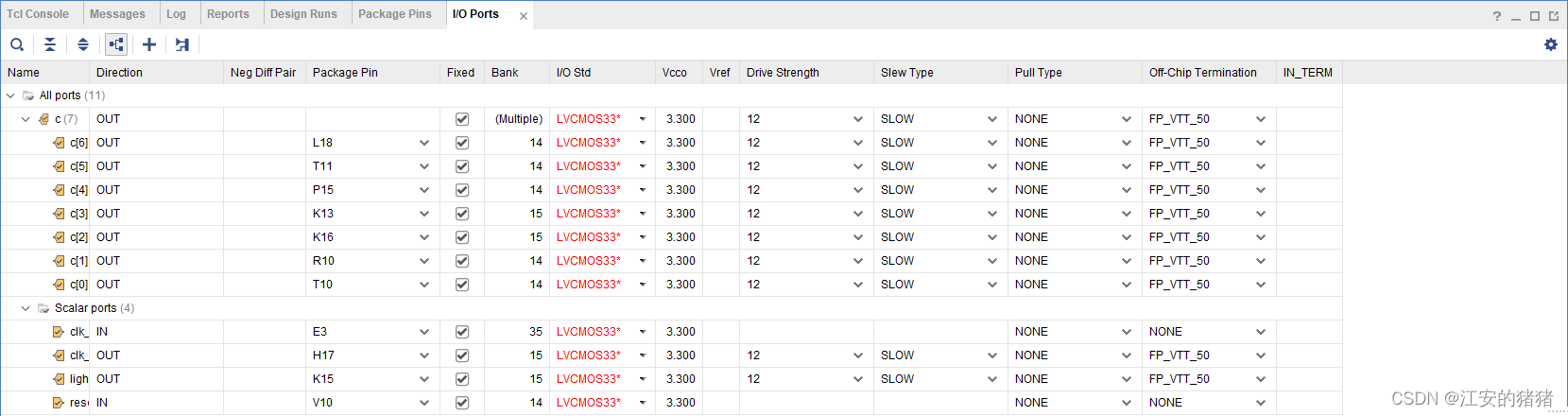

- 在如下界面找到Schematic,点击,然后在I/Oports界面设置端口,具体设置需要查看相应手册。

3.再次运行Synthesis,再点击运行Implementation,Generate Bitstream

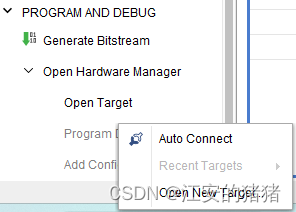

4.连接FPGA板,在如下位置找到Open Target,点击auto connected

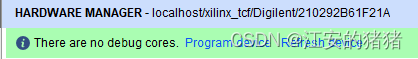

5.点击Program device,就大功告成了。

3670

3670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?