计数器是数字电路中基本逻辑部件,其功能是记录输入脉冲的个数。计数器的输入端接入一个或多个信号,输出端则显示当前计数值。

计数器的工作原理是:当输入端的敏感信号发生变化时,计数器的计数器自加1。

而计数器也有着常见的几种类型,如二、十进制计数器、BCD计数器、格雷码计数器这些不同进制的计数器,以及置位、加减、环形、Johnson计数器等类型。

下面以二进制计数器为例,介绍计数器的基本原理。

先以HDLBIT上的一道基础计数器题目进行介绍:

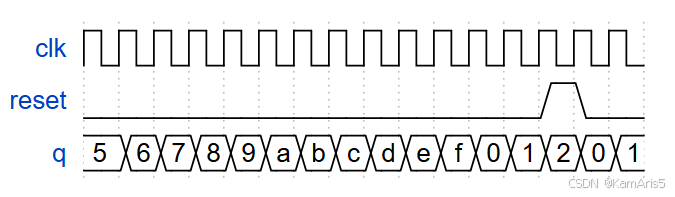

通过题目的波形图,很明显是让我们写一个时钟边沿敏感的0-15且带有复位置数清零的计数器。

module counter(

input wire clk,

input wire reset,

output reg [3:0] q

);

always @(posedge clk) begin

if(reset)begin

q <= 0;

end

else if(q == 4'd15)begin

q <= 0;

end

else begin

q <= q + 1;

end

end

endmodule

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?