随机只读存储器(简)

一、静态RAM(SRAM)

存储01的方式:采用触发器

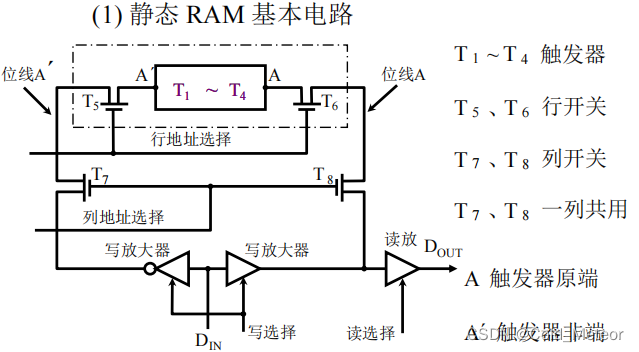

SRAM基本电路图

T1到T4是一个由MOS管所组成的触发器基本电路,T5,T6则是行地址选择信号控制开关。这里由T1到T6这6个MOS管共同构成一个基本单元电路。

T7、T8受列地址选择控制。分别与位线A和位线A`相连。他们不包含在基本单元电路内,而是由芯片内同一列的各个基本单元电路所共有的。

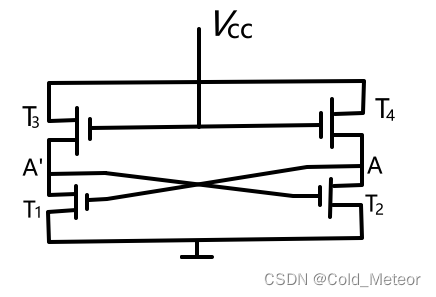

T1~T4内部电路图

上面T3与T4和下面的T1与T2是倒向器,不过上面那两个栅极接好了电压相当于开关打开,来改变下面的高低电平

内部触发器存储1

举个例子,假如T2导通,A因为连接地,所以为低电平0,A和T1的栅极相连,因此T1截止,A’为高电平1,A’的高电平有会保证T2导通,这就相当于稳定了状态1,即存入了1。

读写操作

读操作:

假设触发器已存有"1"信号,即A点为高电平。当需读出时,只要使行、列地址选择信号有效,则使T5、T6、T7、T8均导通,A点高电平通过T6后,再由位线A通过T8作为读出放大器输入信号,在读选择有效时,将"1"信号读出。

写操作:

写入时,不论触发器原状态如何,只要将写入代码送至Din端,在写选择有效时,经两个写放大器,使两端输出为相反电平。当行、列地址选择有效时,使T5,T6,T7,T8导通,并将A与A’点置成完全相反的电平。这样,就把欲写入的信息写入到该基本单元电路中。如欲写入"1",即Din=1,经两个放大器使位线A为高电平,位线A’为低电平,结果使A点为高,A’点为低,即写入了"1"信息。

二、动态RAM(DRAM)

存储01方式:利用电容

电容当中如果保存了电荷,则认为他所保存的是1,如果没有电荷则保存的就是0

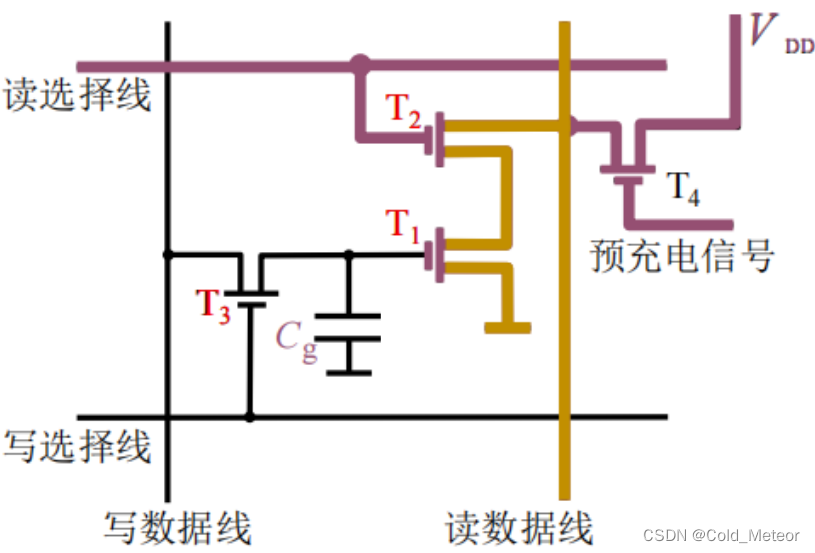

DRAM基本单元电路图

注:

读出与原存信息相反

写入与输入信息相同

读写操作

下面我们来看一下DRAM是如何进行

读操作的:

假如Cg带高电平(即里面存的是1),读出时,先对预充电管T4置一预充电信号(在存储矩阵中,每一列共用一个T4管),使读数据线达高电平Vdd。然后由于读选择线打开T2导通,又因为Cg存的为高电平所以T1导通,则因T1、T2导通接地,使读数据线降为零电平,读出"0"信号。从此可以看出读出信号是与原存的信息相反的。

写操作的话:

我们假设写入信号为高电平(即写入1),我们将写入信号加到写数据线上,然后由写选择线打卡T3,这样,Cg便能随输入信号进行充电(写入"1",因为电容带电即为1嘛)。

总结

本文仅仅简单介绍了随机存储器的读写操作,初学者能力有限,知识点不全面,只是简单记录自己每日所学。如果能帮助到你,我会感到十分的开心。

328

328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?