一、简答

一. HLS是什么?与VHDL/Verilog编程技术有什么关系?

HLS(High-Level Synthesis,高层次综合)是一种允许开发者使用高级编程语言(如C/C++)来描述硬件设计的技术,然后这些高级语言代码可以转换成硬件描述语言。

二. HLS有哪些关键技术问题?目前存在什么技术局限性?

关键技术

- 输入语言采用了类 C语言而非前两代的 HDL 语言,如 C、C++、SystemC 以及SpecC、HandelC等,这能够使得系统模型得到复用,进行进一步的软硬件实现。

- 实现了对时序(timing)比较精确的评估和调度。

- 实现了对验证环境的重复使用,通过 TLM 建模技术可以将系统验证环境复用于 RTL 级验证,降低了验证的复杂度。

局限性

- 没有早期的性能估计以及任何违反设计和平台限制的行为

- 没有利用所有可能的数据通信方式

- 没有功能概述,也没有对用户代码进行优化转换

- 支持代码报告得太晚了

- 在某些情况下,工具的高效实施是不可能的,例如当必须将太多的加速器映射到硬件部分时。HLS工具无法预先检测到这种情况,也无法在用户坚持的情况下尽量减轻其影响。

二、HLS入门级程序实现

1、项目配置

1.新建项目

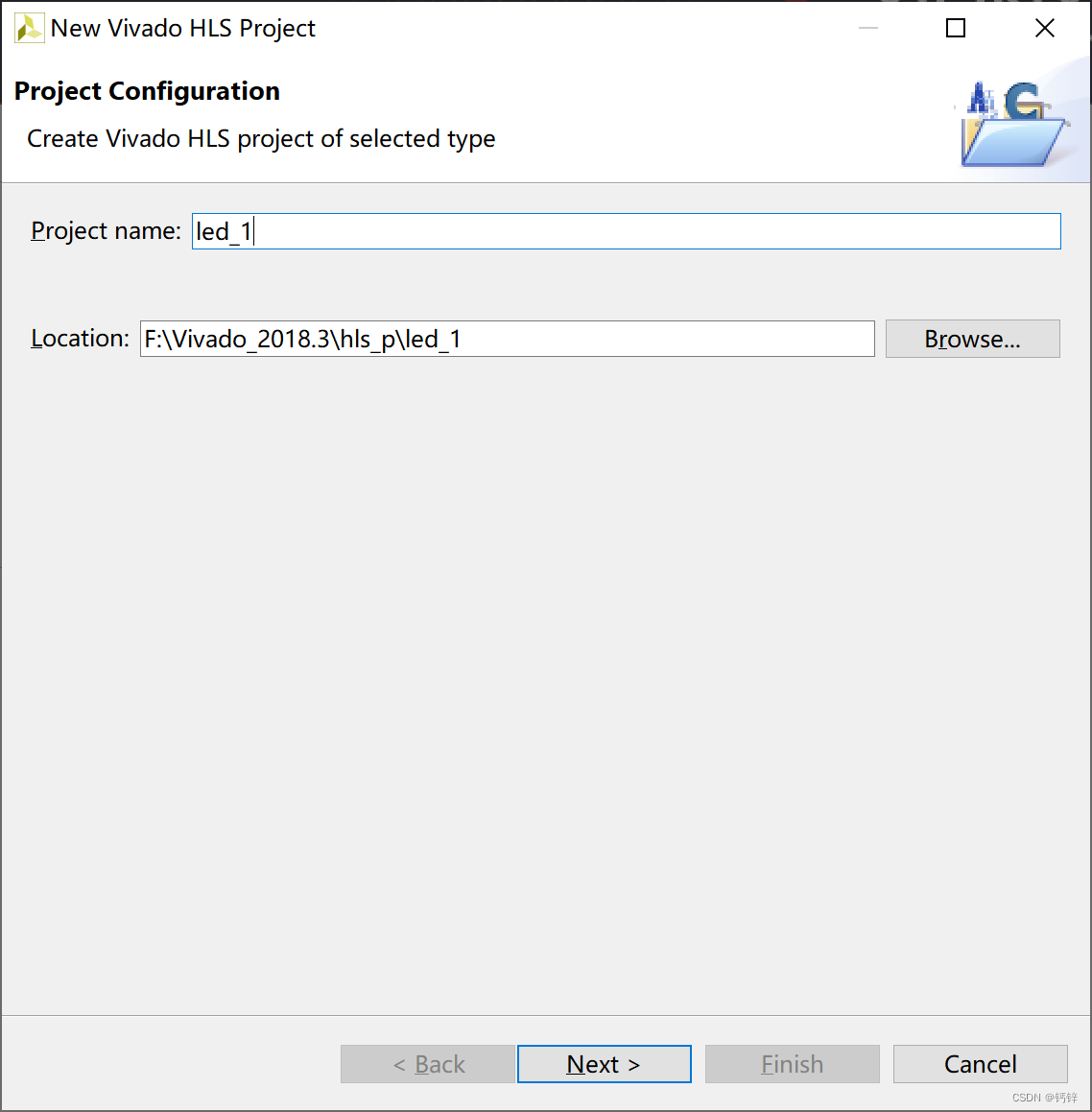

2.设置项目名

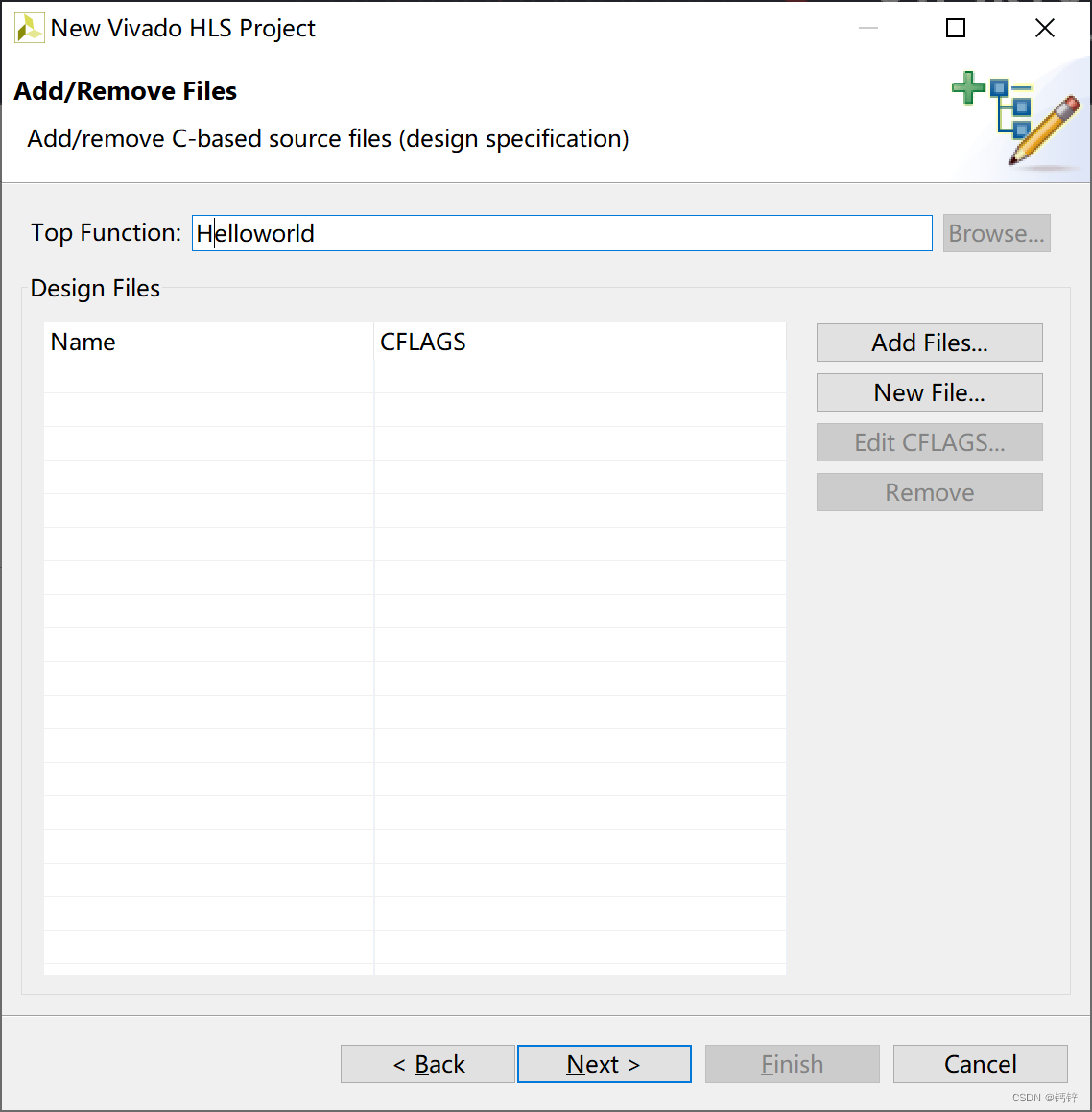

3.加入文件

2、C仿真

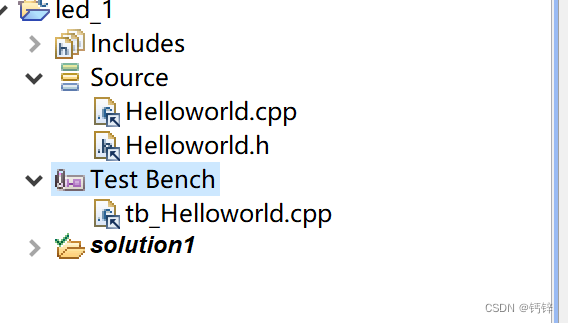

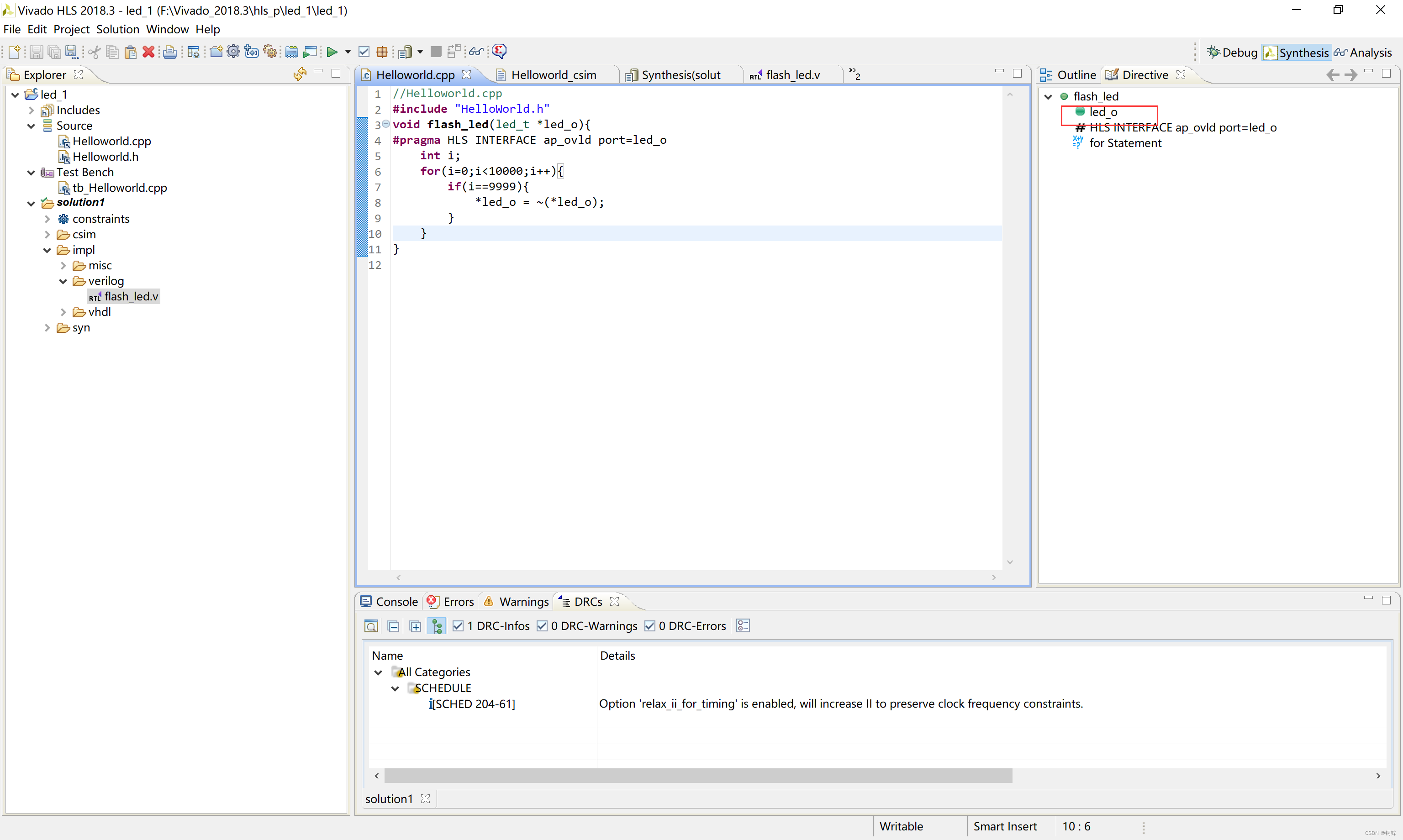

1.编写代码

Helloworld.h

//Helloworld.h

#ifndef _HELLOWORLD_H_

#define _HELLOWORLD_H_

#include "ap_int.h"

typedef ap_int<1> led_t;

void flash_led(led_t *led_o);

#endif

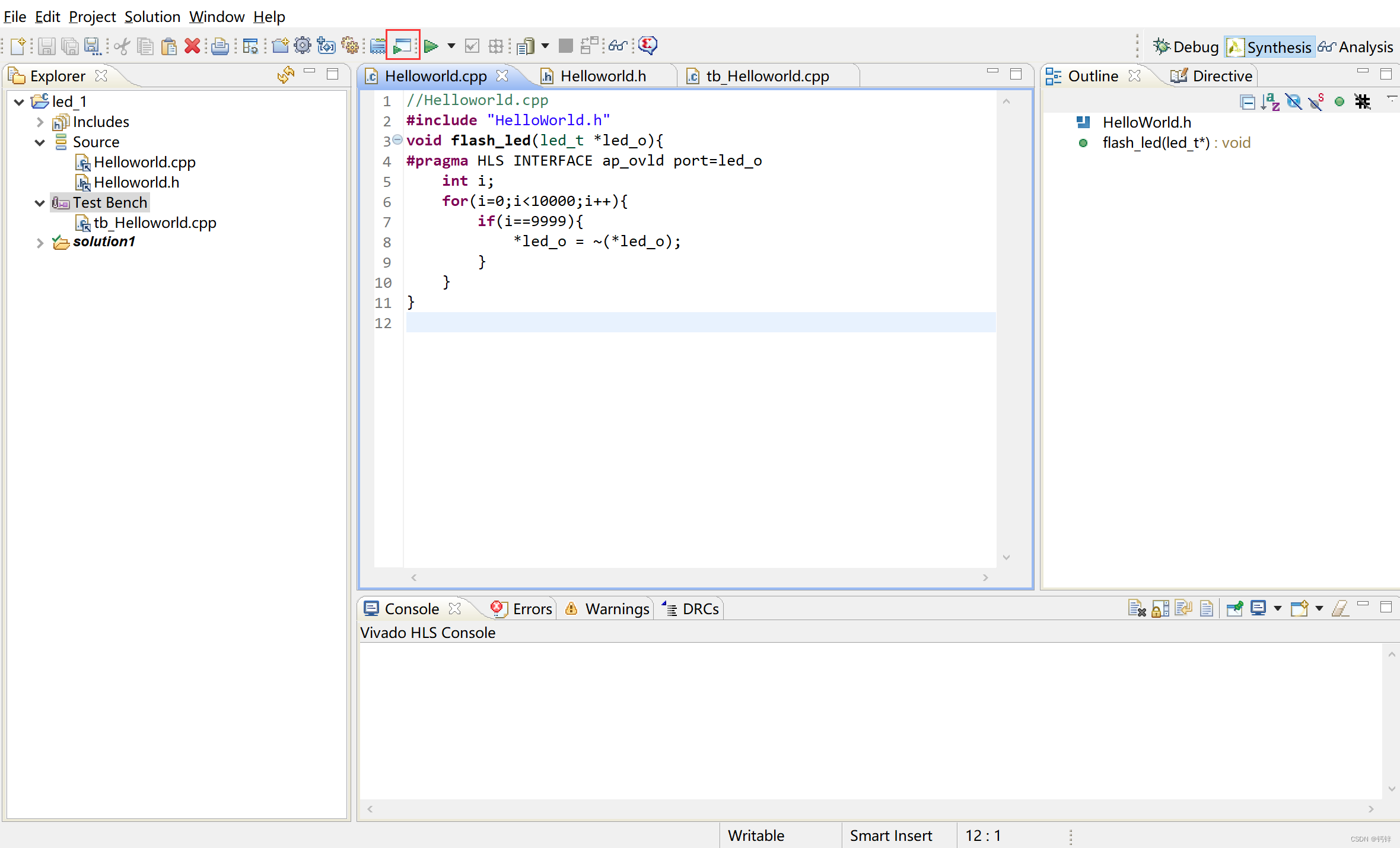

Helloworld.cpp

//Helloworld.cpp

#include "HelloWorld.h"

void flash_led(led_t *led_o){

#pragma HLS INTERFACE ap_ovld port=led_o

int i;

for(i=0;i<10000;i++){

if(i==9999){

*led_o = ~(*led_o);

}

}

}

tb_Helloworld.cpp

#include "HelloWorld.h"

#include <stdio.h>

int main(){

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o);

printf("result : %d \n",(int)(led_o&0x01));

}

}

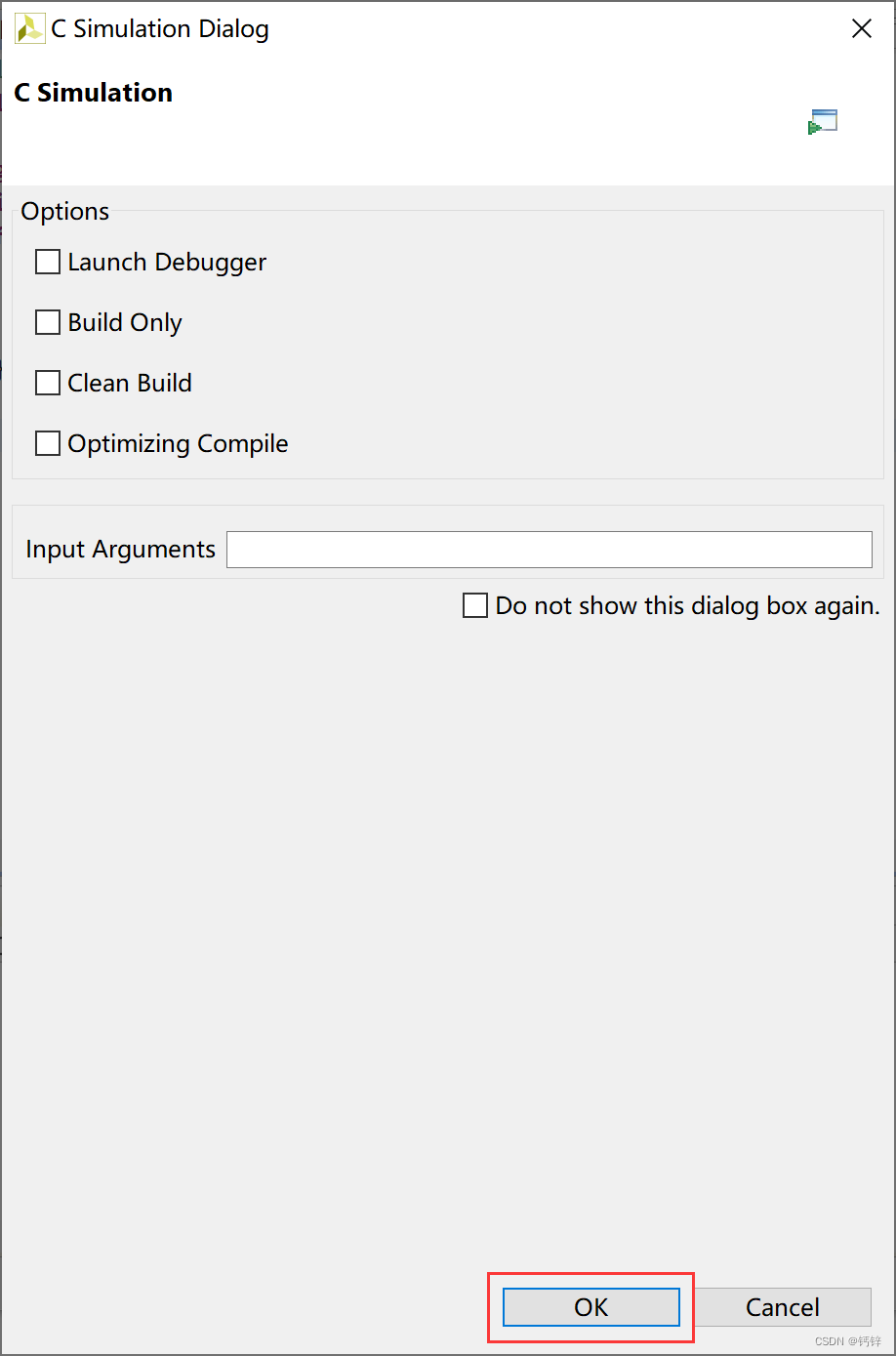

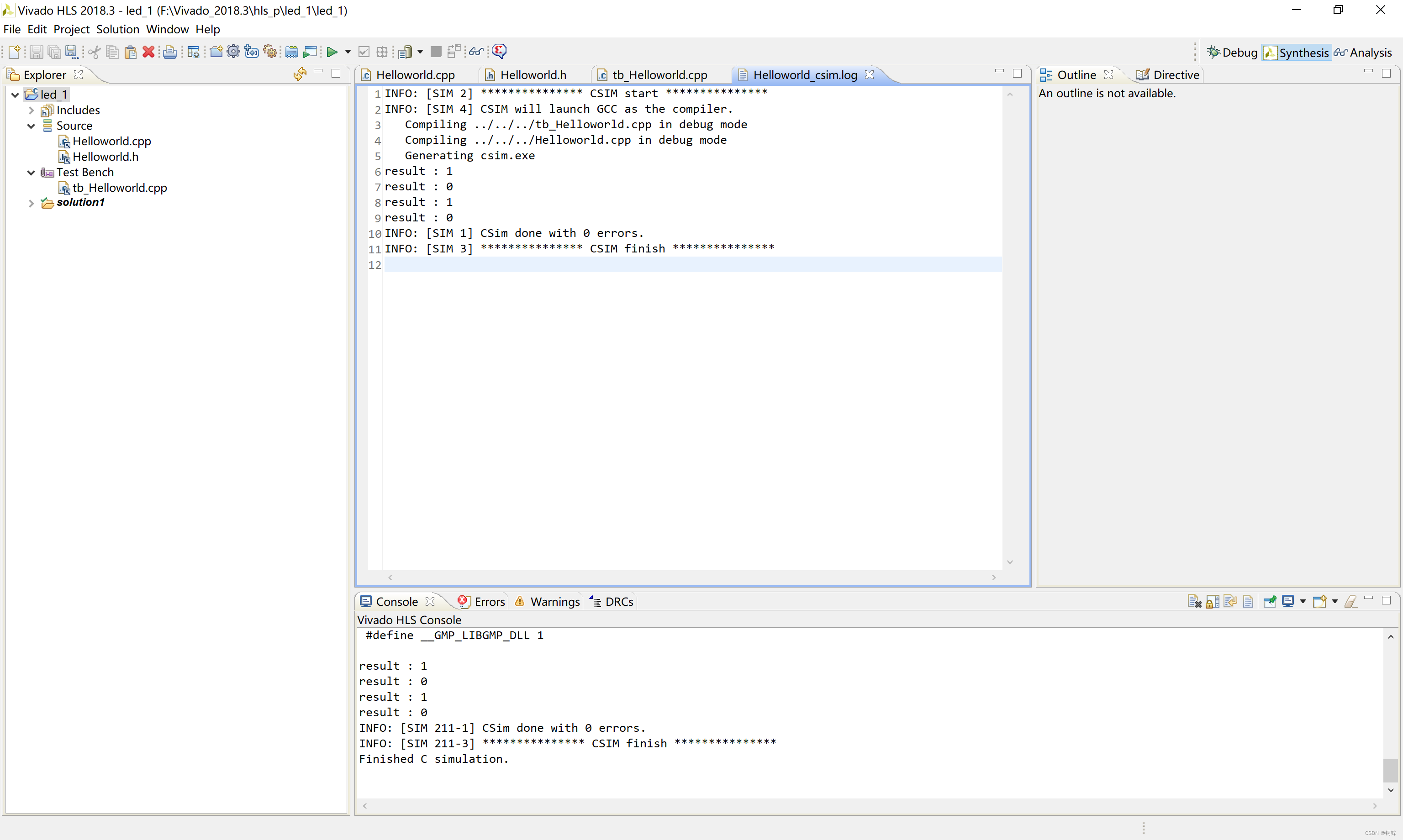

2.仿真

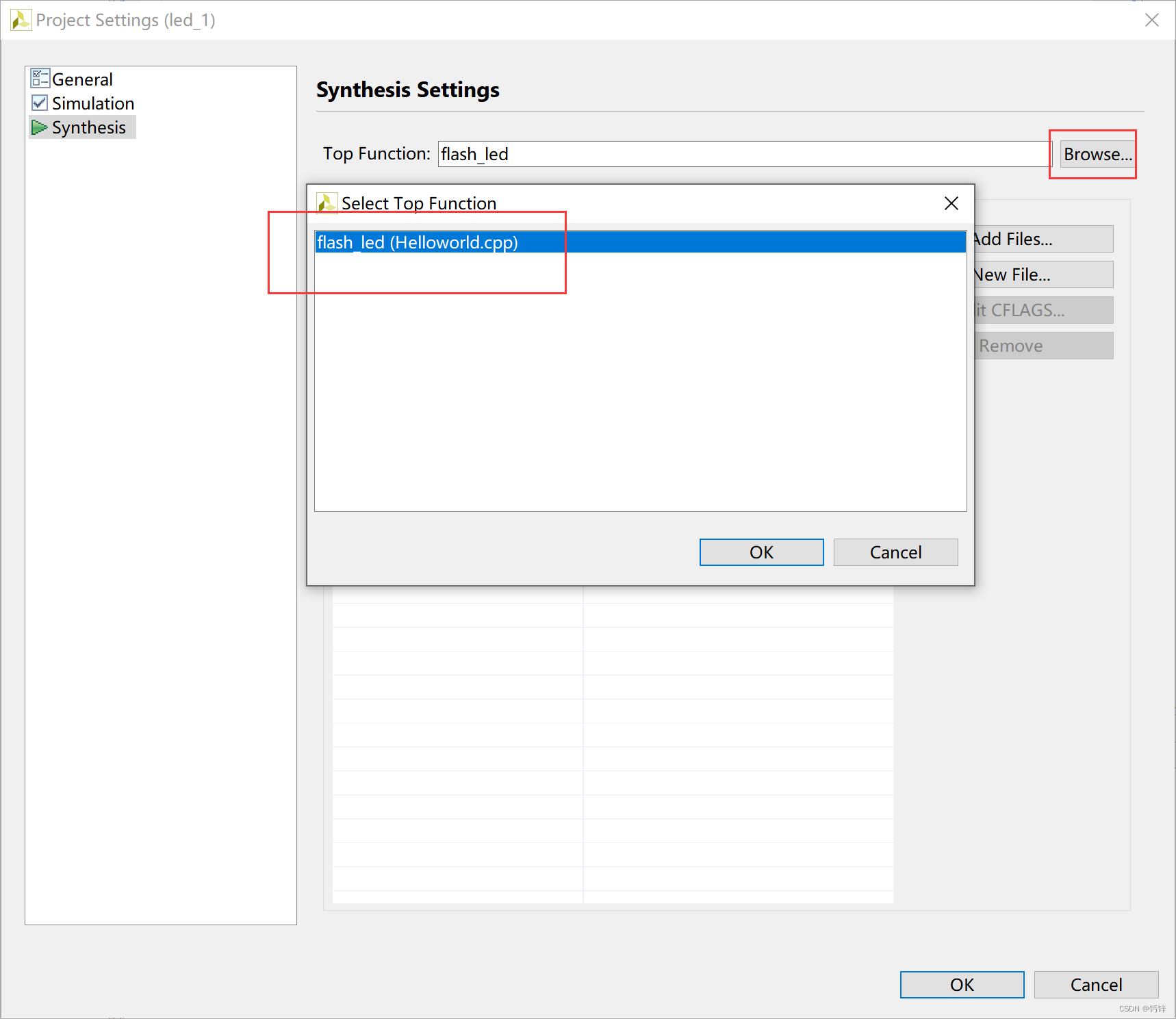

3.综合

Project -> Project Setting -> Synthesis,选择flash_led

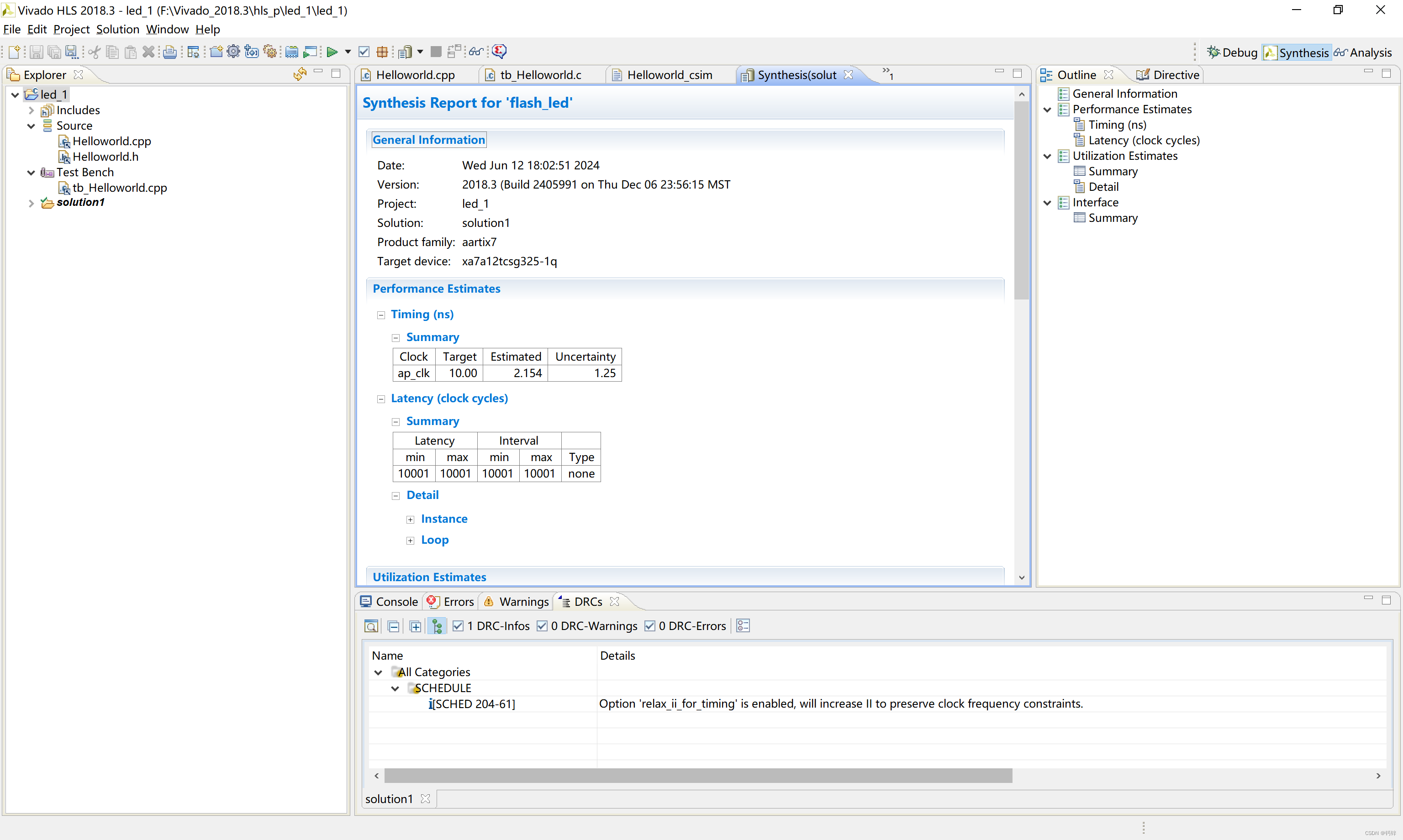

运行

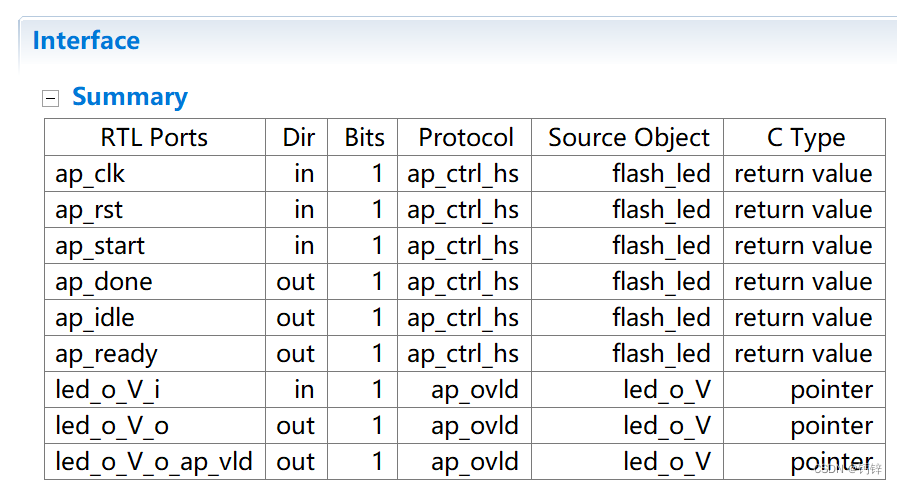

有关端口的表格

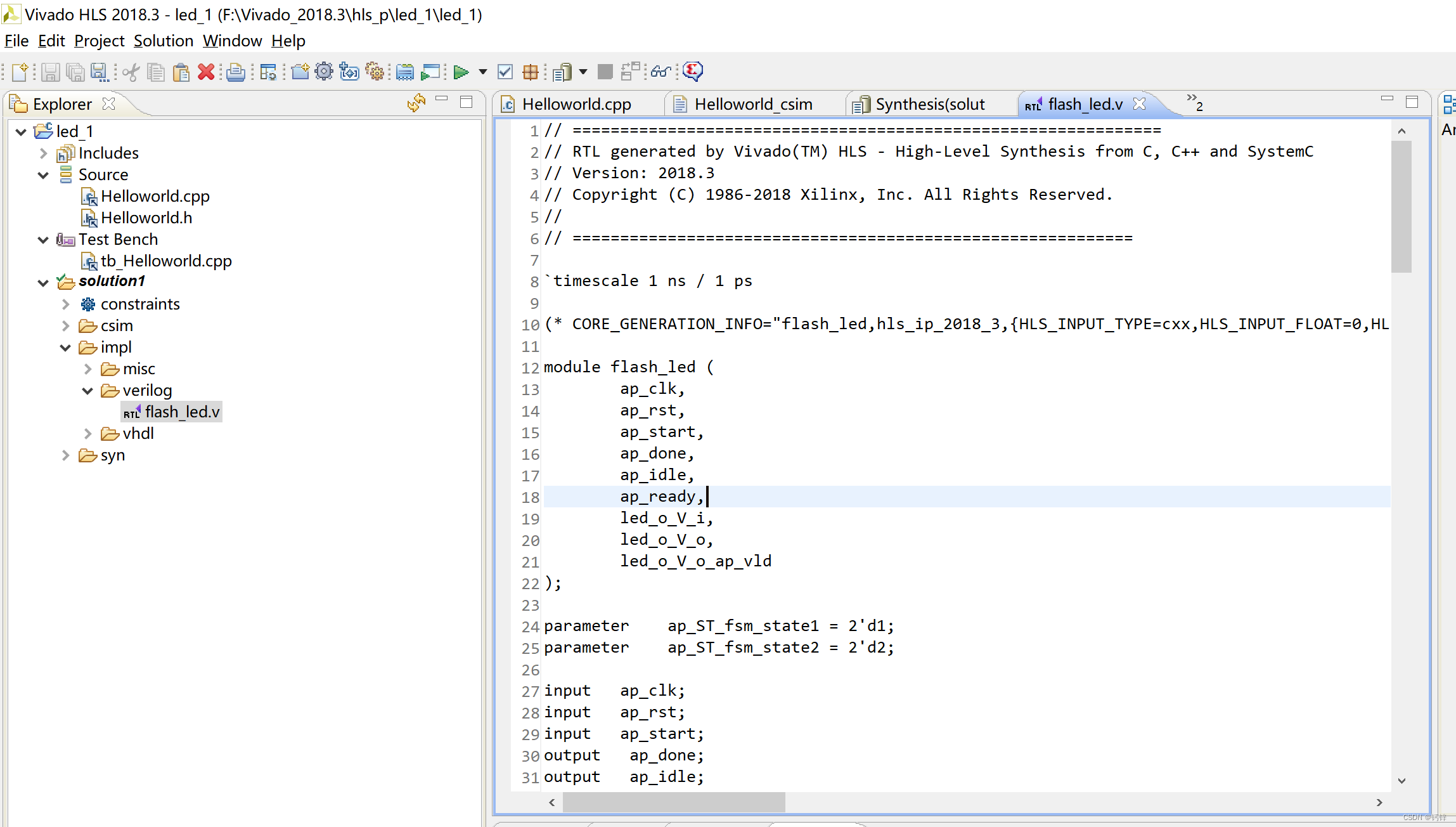

在solution1\impl\verilog中,有已经生成好的.v文件:

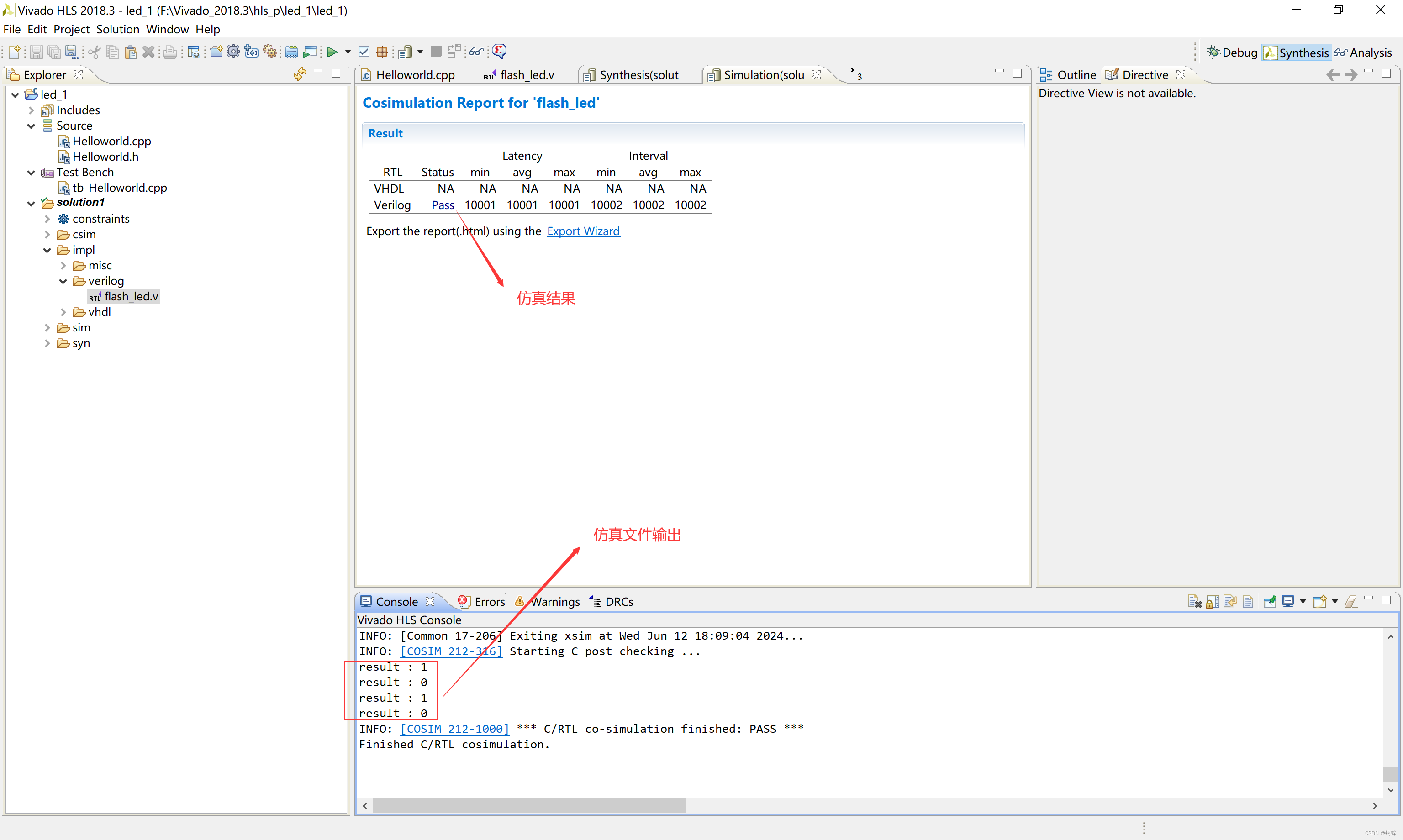

4.联合仿真

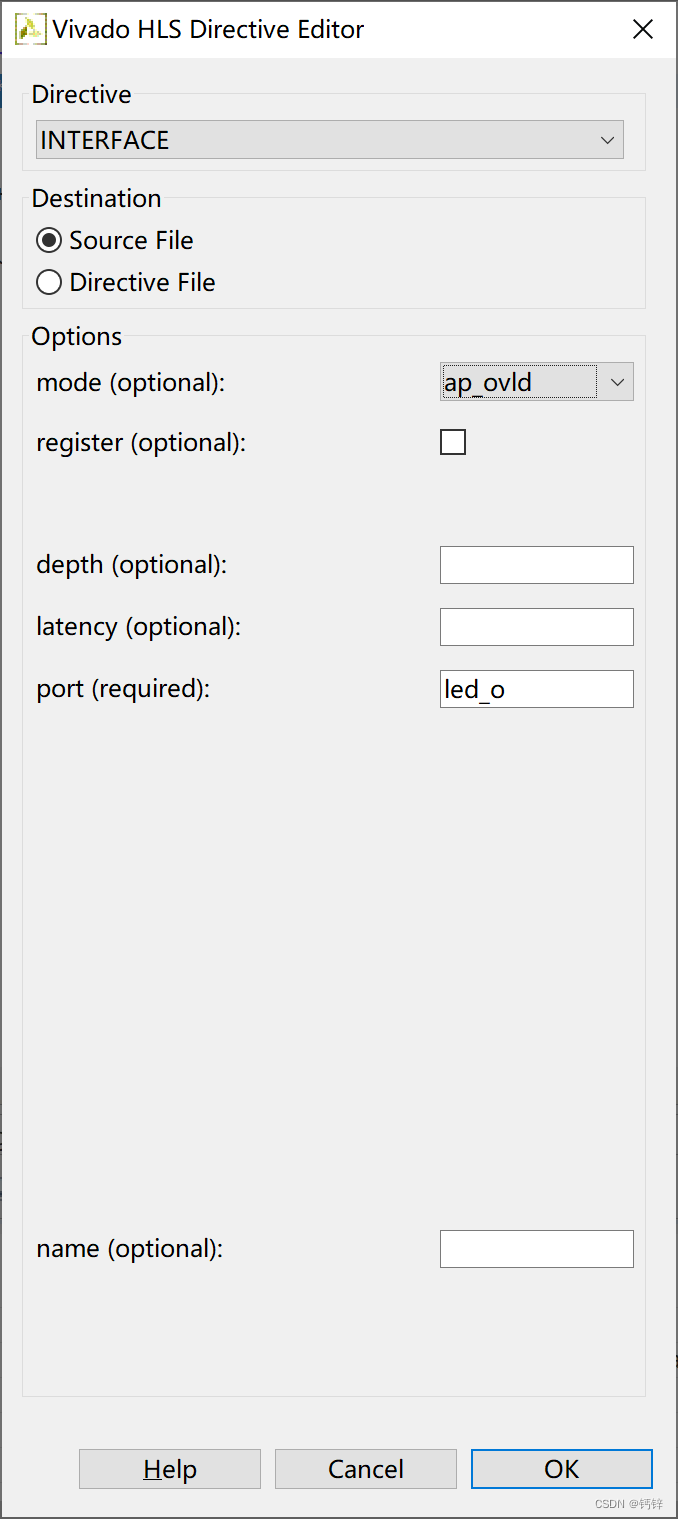

进入led_o

配置如下

点击联合仿真

参考资料

- https://blog.youkuaiyun.com/weixin_54435584/article/details/130774070

- https://blog.youkuaiyun.com/eininbebop/article/details/117331457

1090

1090

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?