目录

HLS介绍

1.HLS的概念

HLS是一款高层次综合工具,可以帮助开发者加快开发效率。开发者可以通过HLS将C/C++等高级语言转换为RTL电路。尤其,在对于一些比较复杂的算法的时候,能够提供较大的便利。

2.HLS与VHDL/Verilog

VHDL/Verilog对于一些算法比较简单,开发周期不长的来说是比较适用的,然而,一个开发过程,往往算法会比较复杂,并且可能会经历较长时间的仿真和调试,面对这样的问题,提出了HLS。通过高级语言编程,来实现功能模块,这样就会大大提供开发效率。

3.HLS的关键技术

通过高级语言实现功能,并转换为RTL电路。实际上HLS相对于一个IP生成器。

4.技术局限性

对于人工智能方面来说,HLS在开发上,还是比较困难的,需要有强大的C/C++的编程能力,从而,来实现功能。

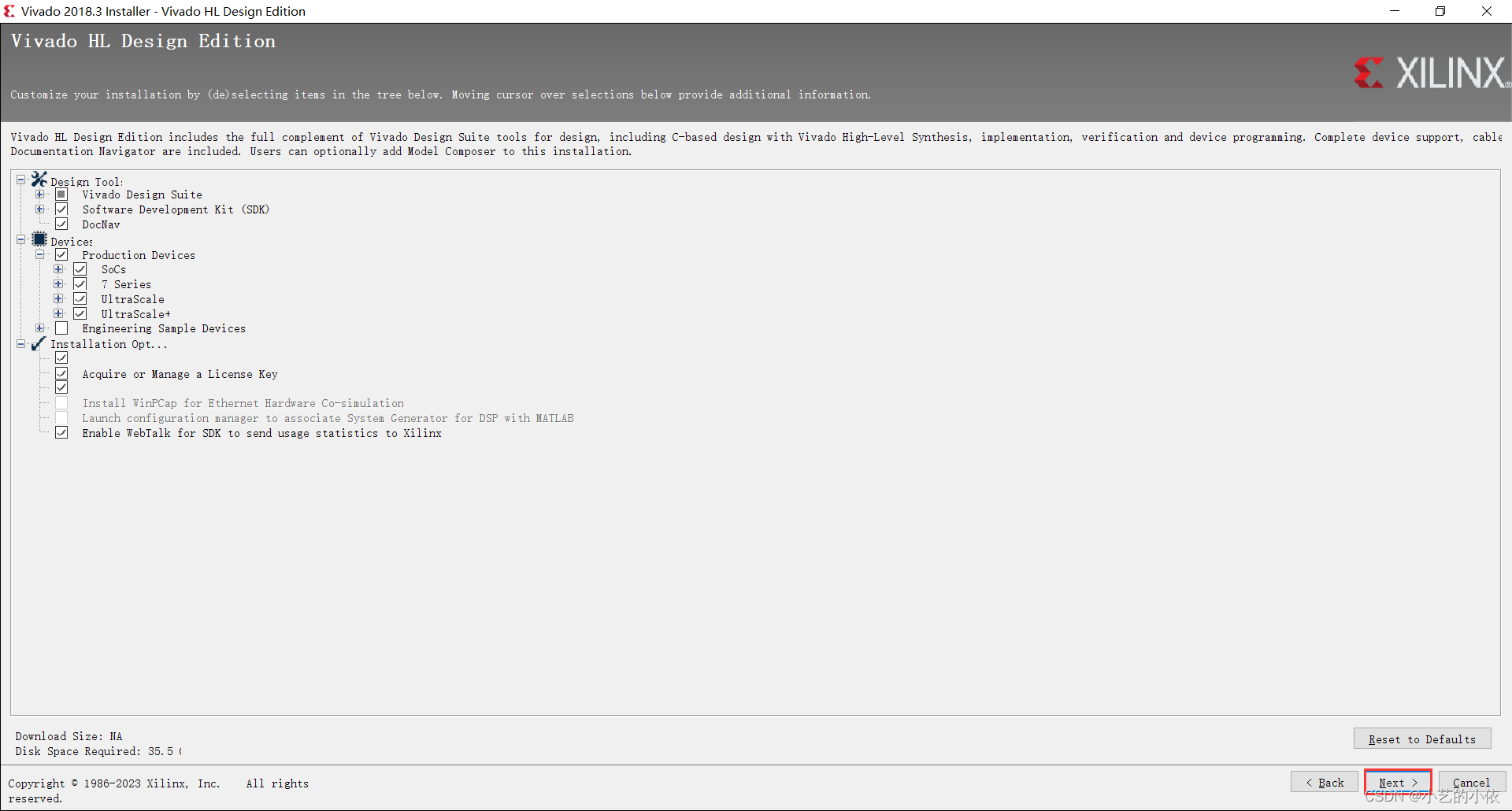

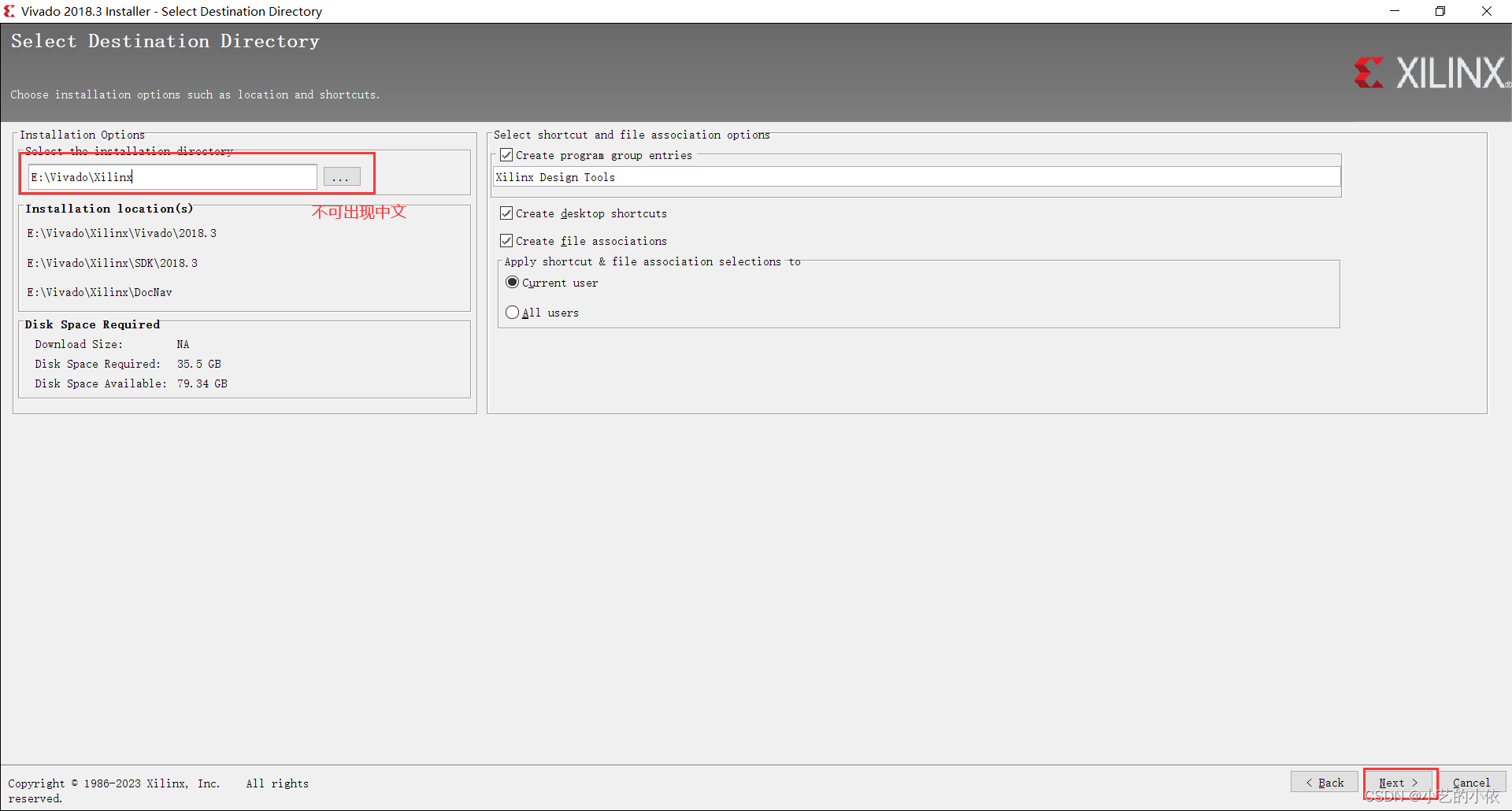

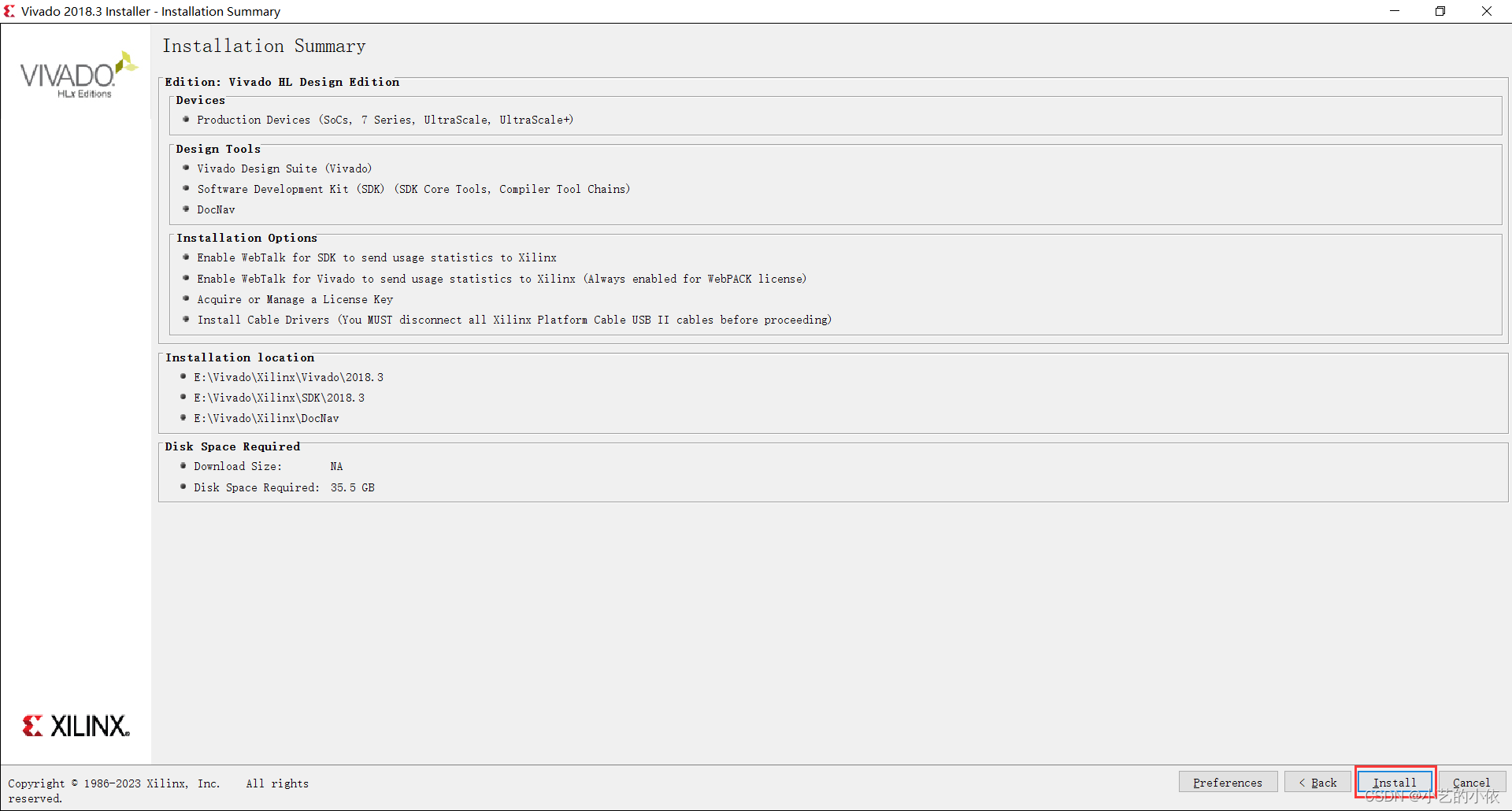

Vivado2018.3的下载和安装

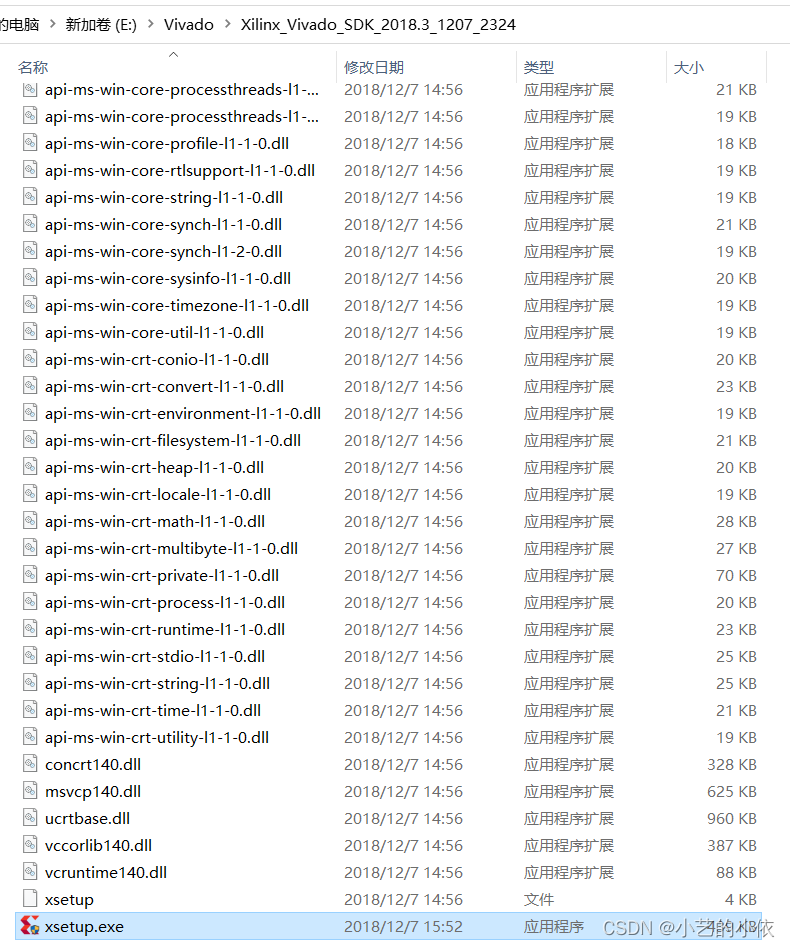

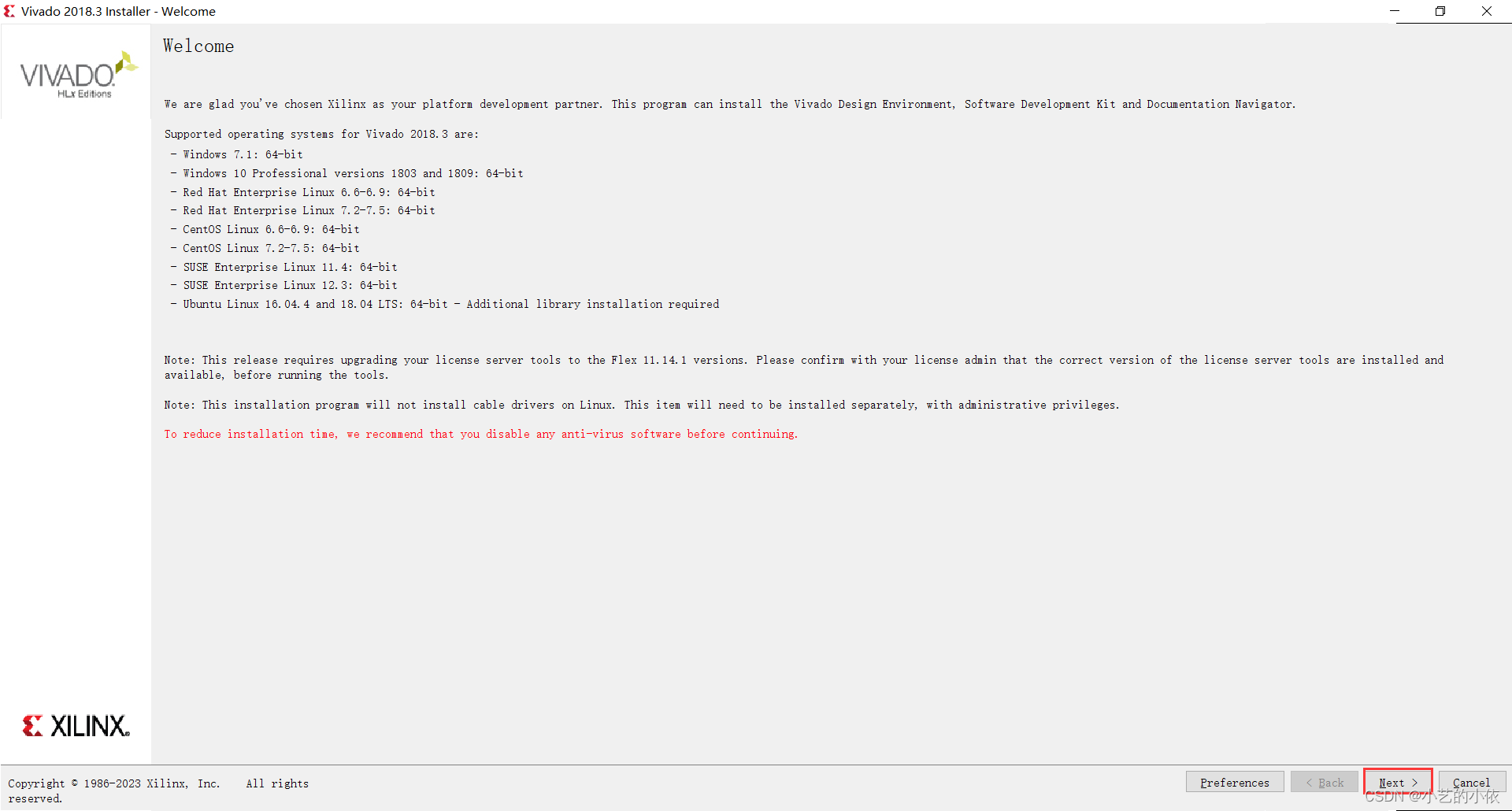

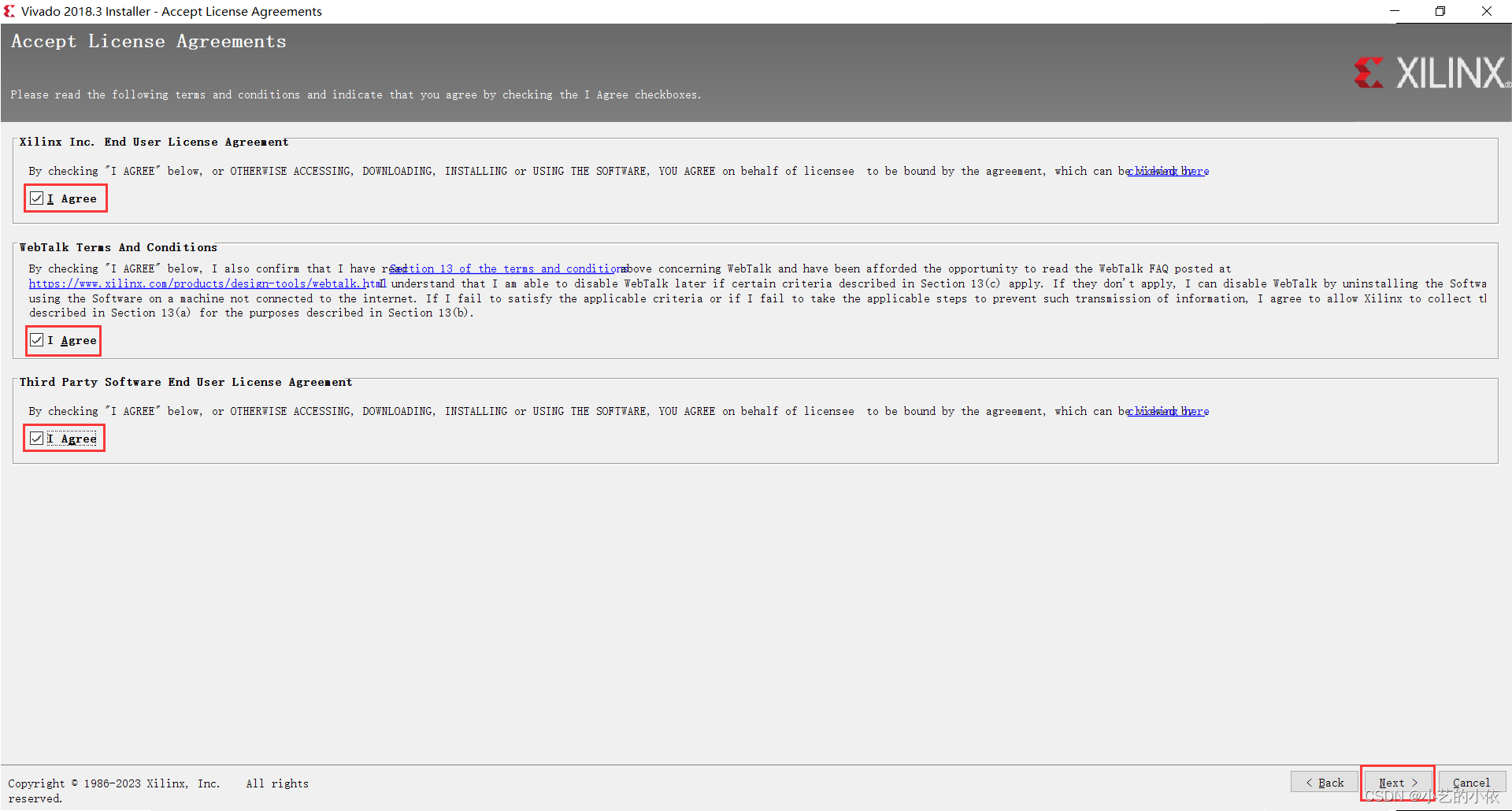

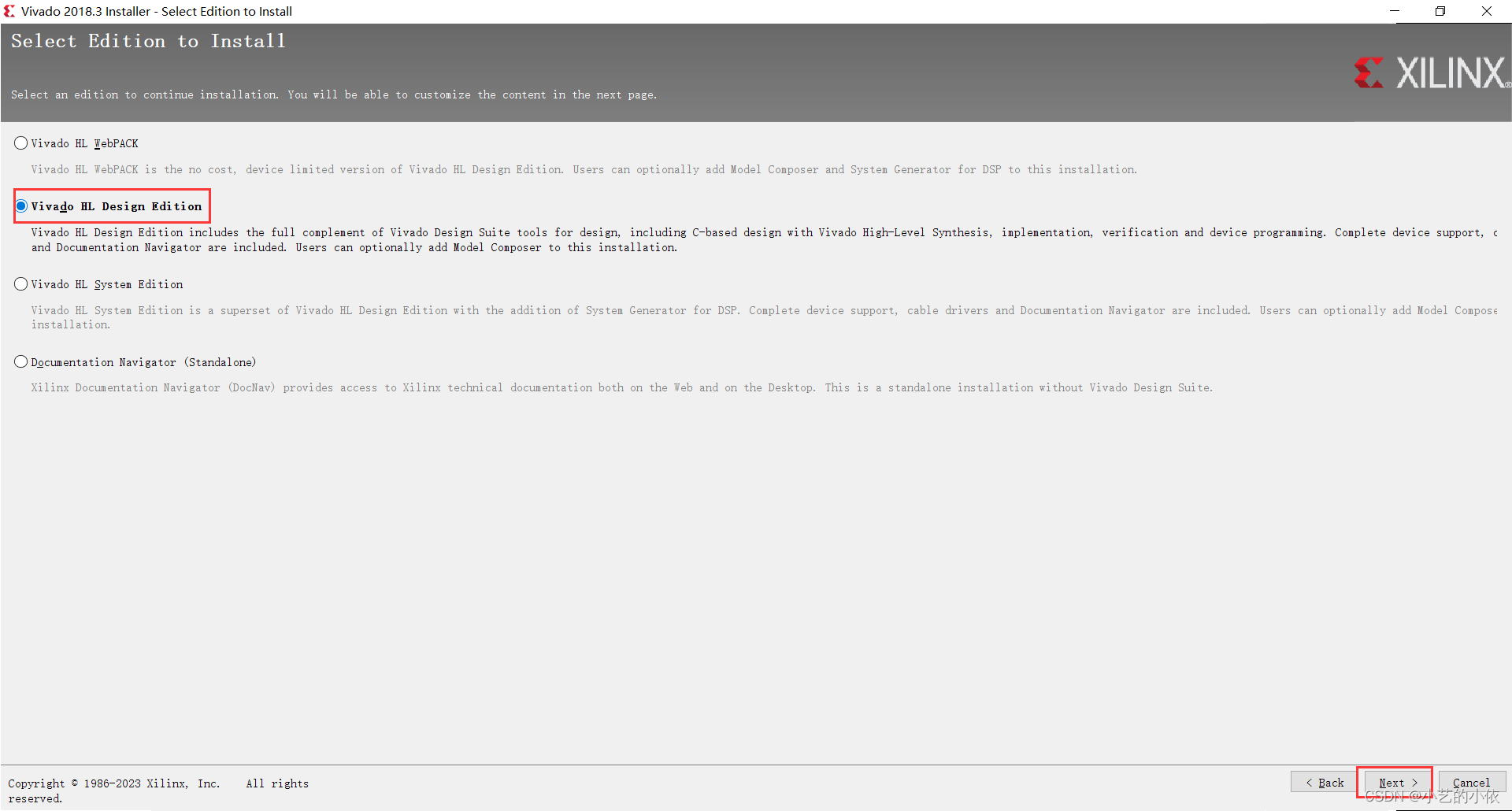

网盘地址https://pan.baidu.com/s/1jkurhTLgnxavgRnmi-JLDA提取码:sygh,这一步之前建议提前准备80G左右的内存。解压后双击xsetup.exe文件。

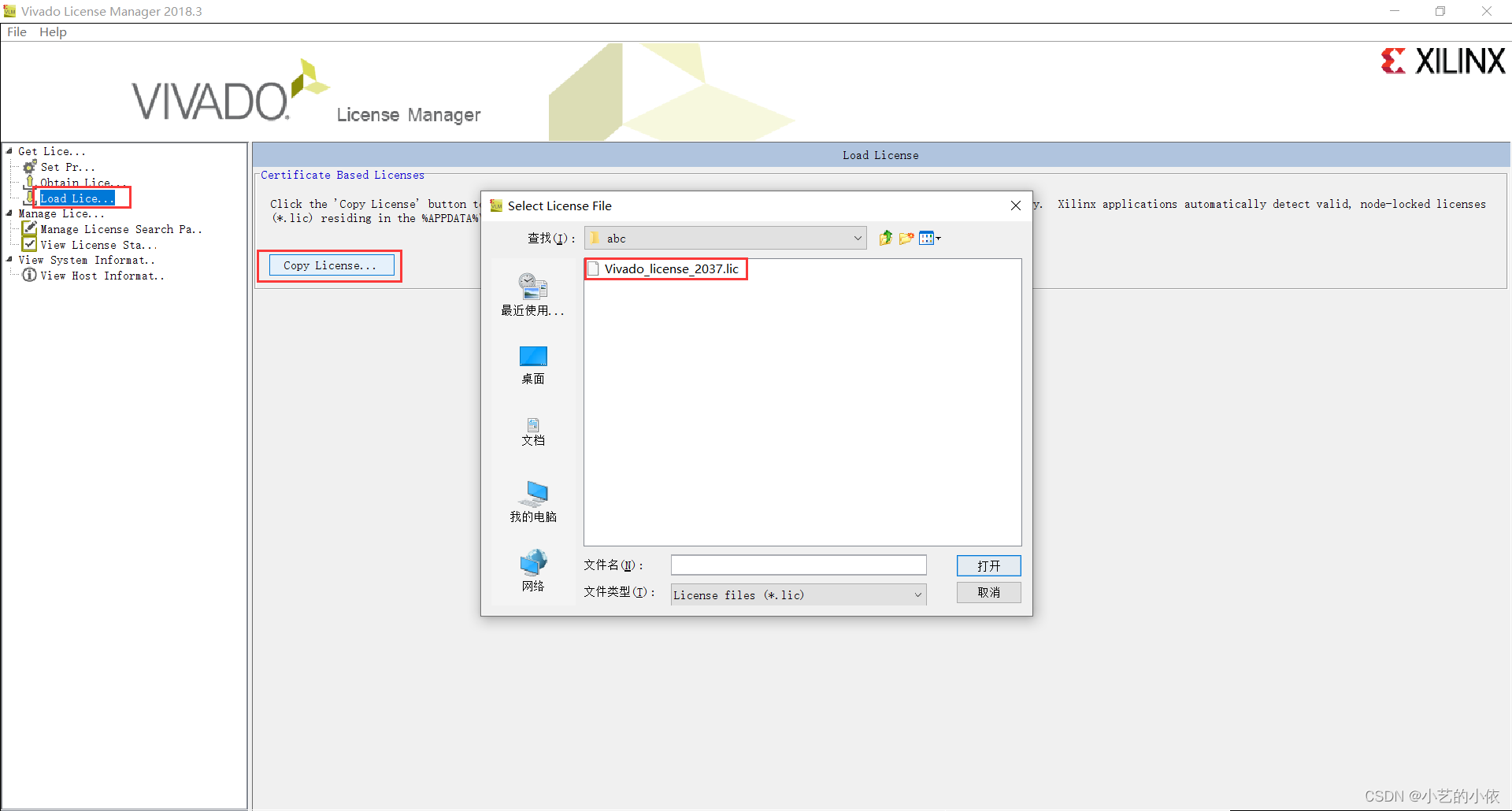

license链接https://pan.baidu.com/s/1-2QL3MCYhUh-qANEuxVHIQ提取码:vh3h

弹出有c盘什么玩意的就是成功了,直接关掉就ok

HLS实现led灯的点亮

创建HLS工程

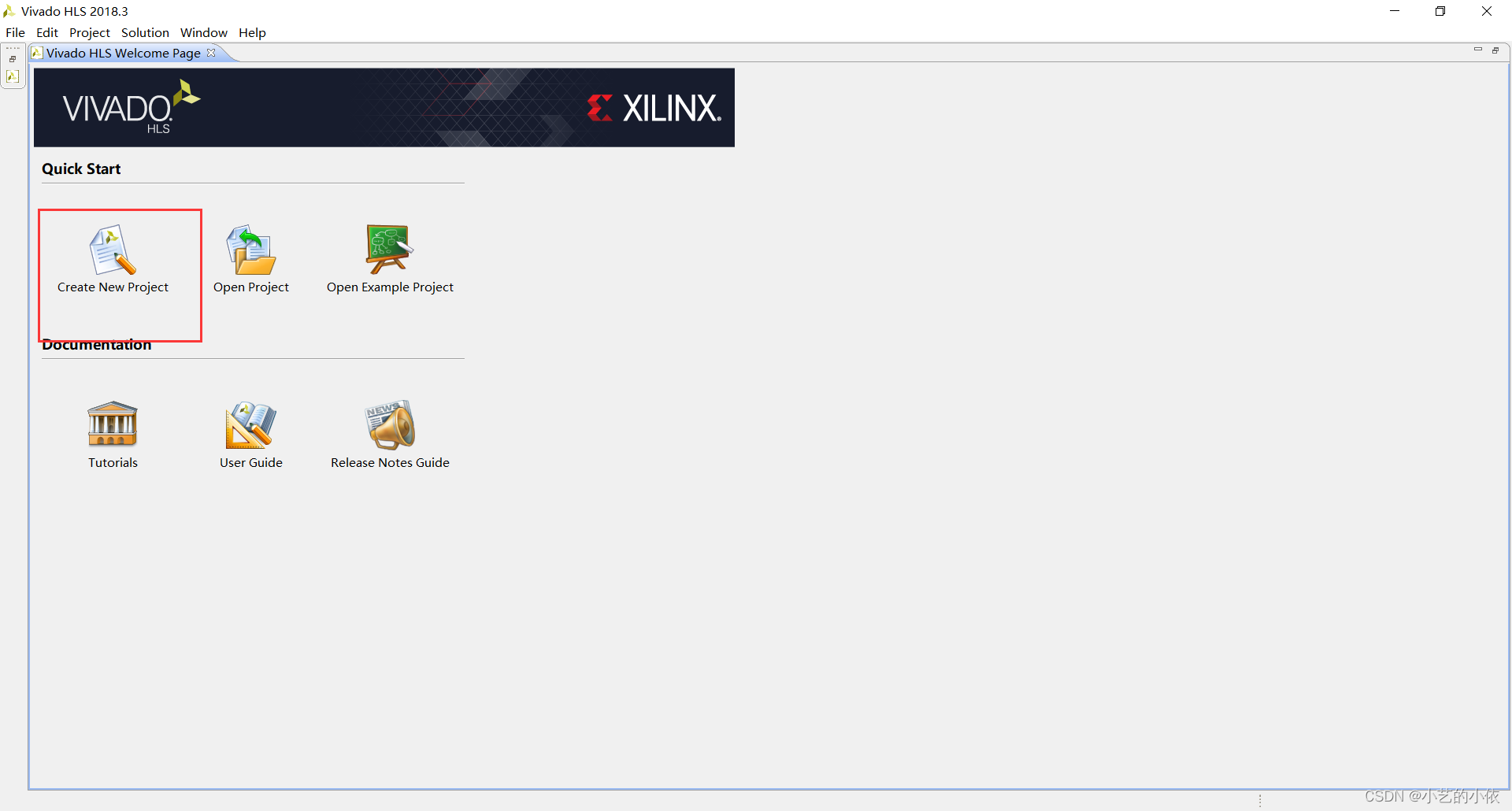

打开Vivado HLS,点击Create New Project

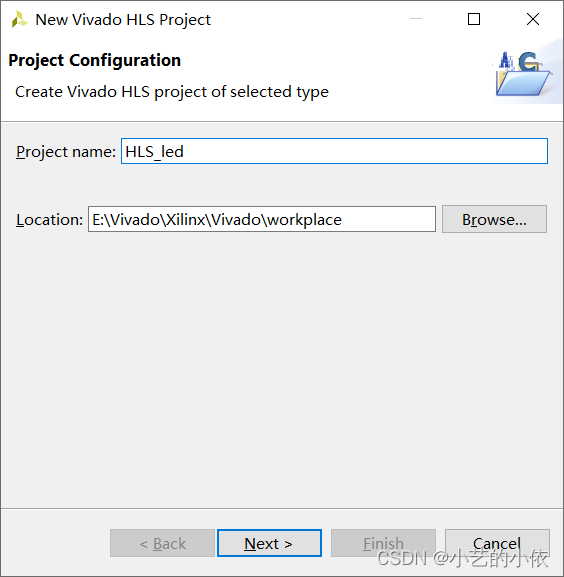

编辑文件路径和文件名

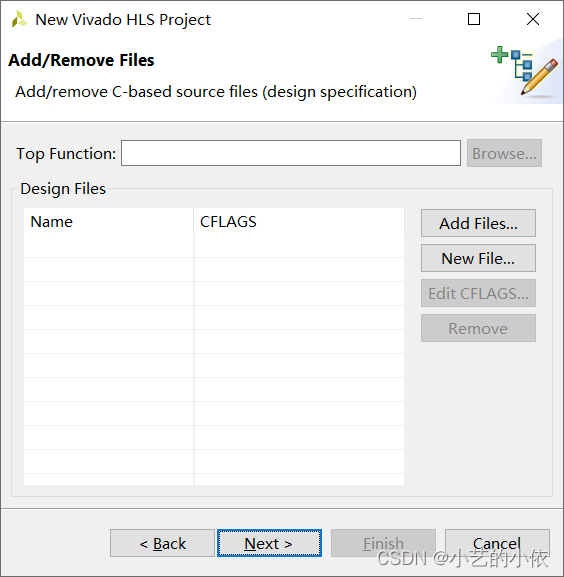

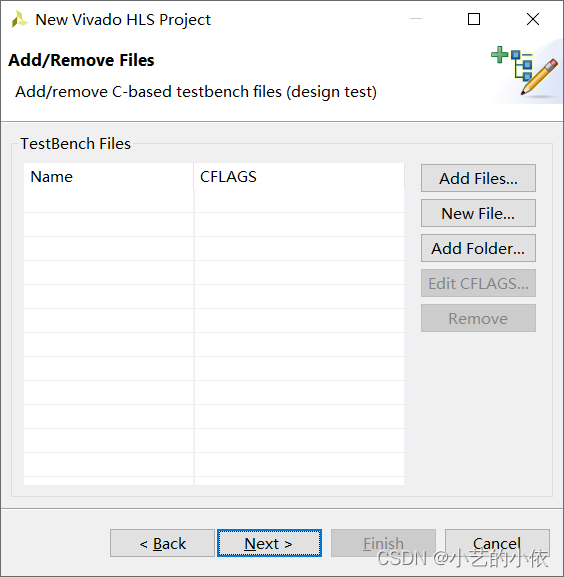

顶层文件和C仿真文件,这里都直接默认

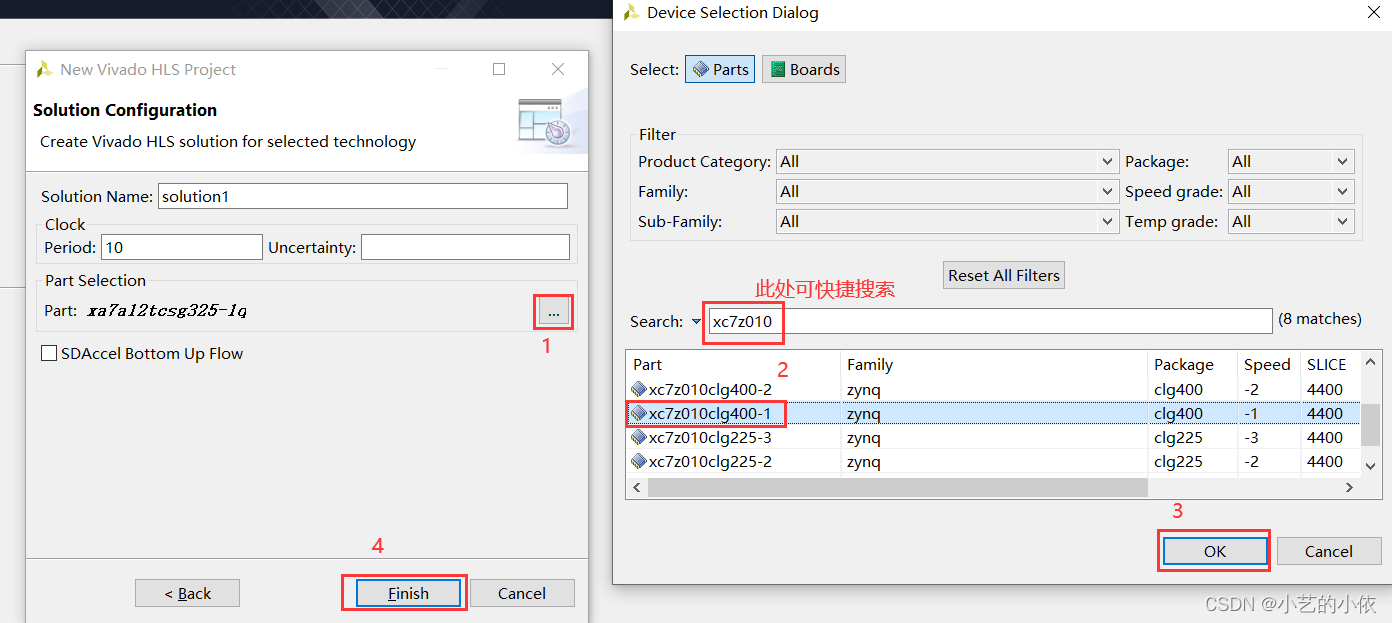

选择器件,xc7z010clg400-1

添加文件

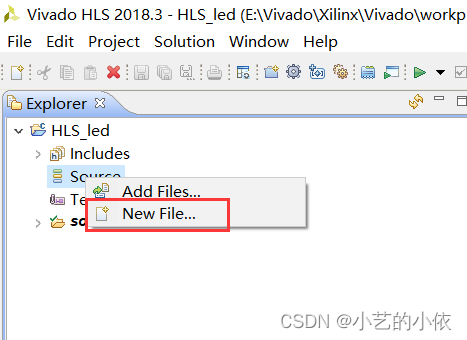

右击,new file

直接加入文件并编辑就可以了

led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

led.cpp

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

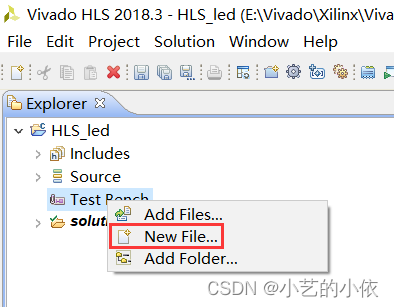

接下来是test bench,还是右击,new file

这里保存一下,进入下一步

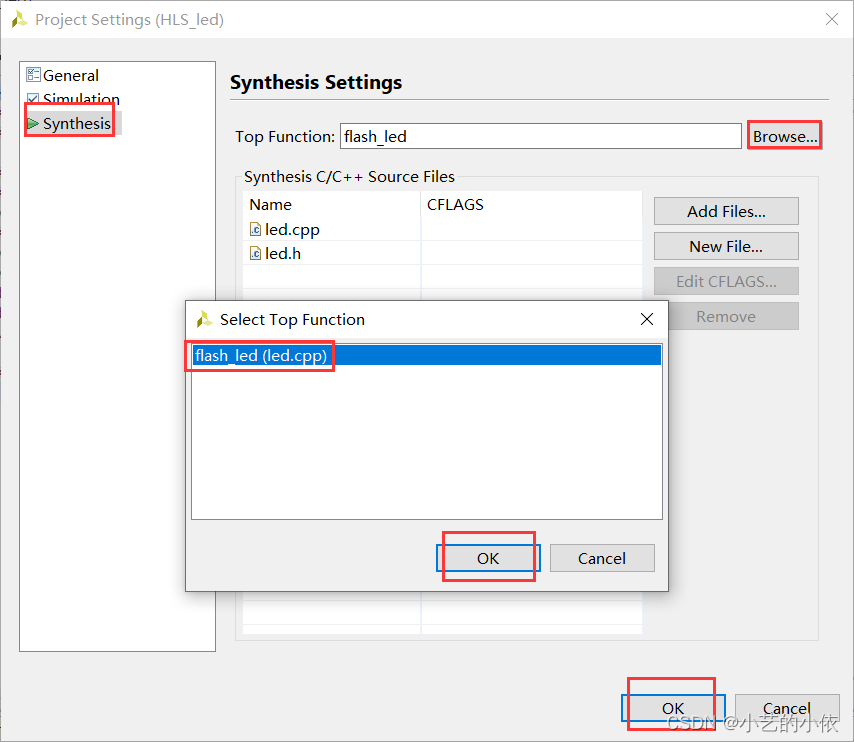

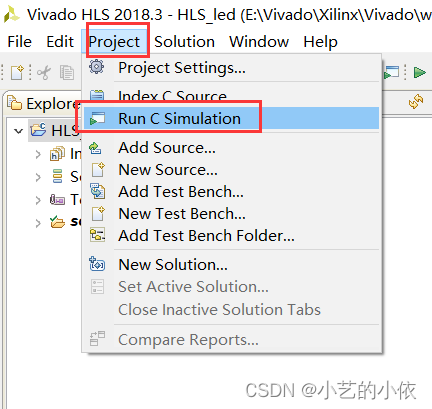

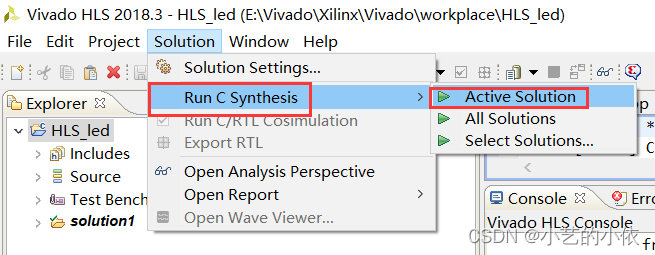

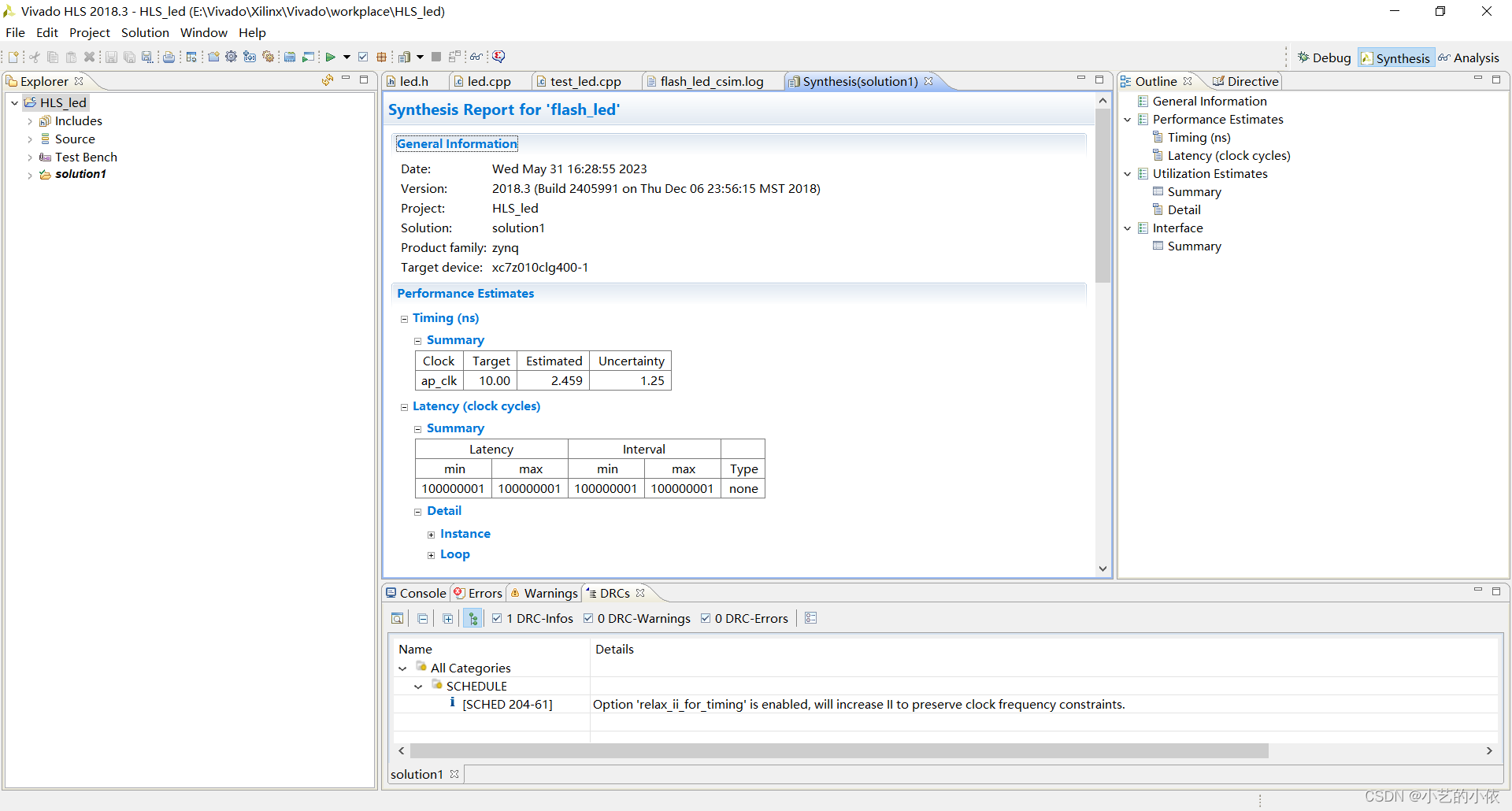

C仿真与C综合

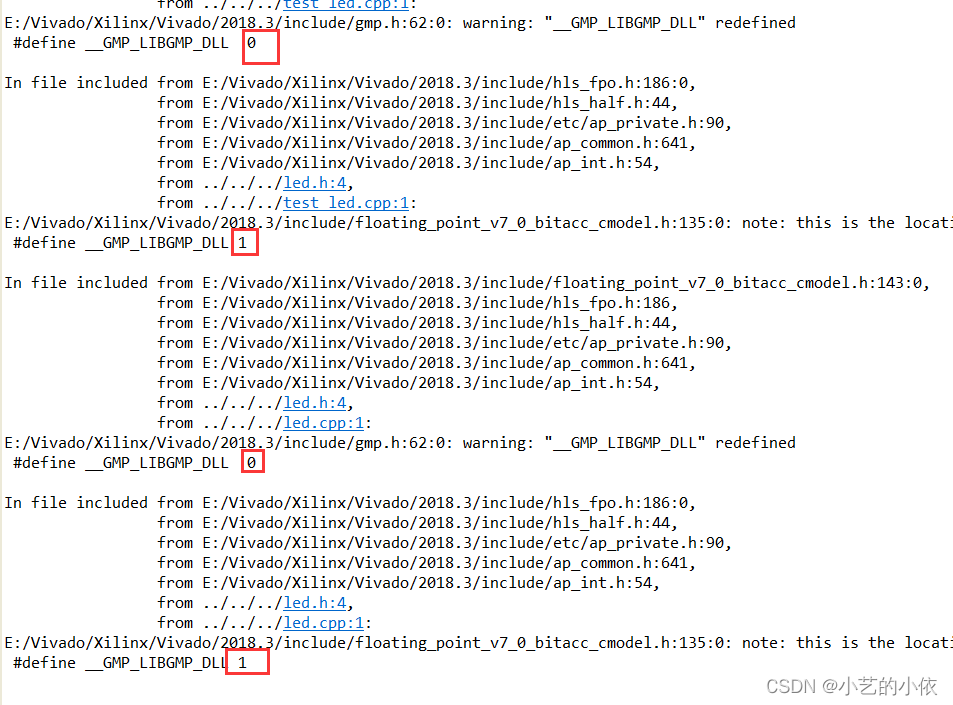

有了这种01交替就是C仿真成功

应该是类似于这种界面就ok了

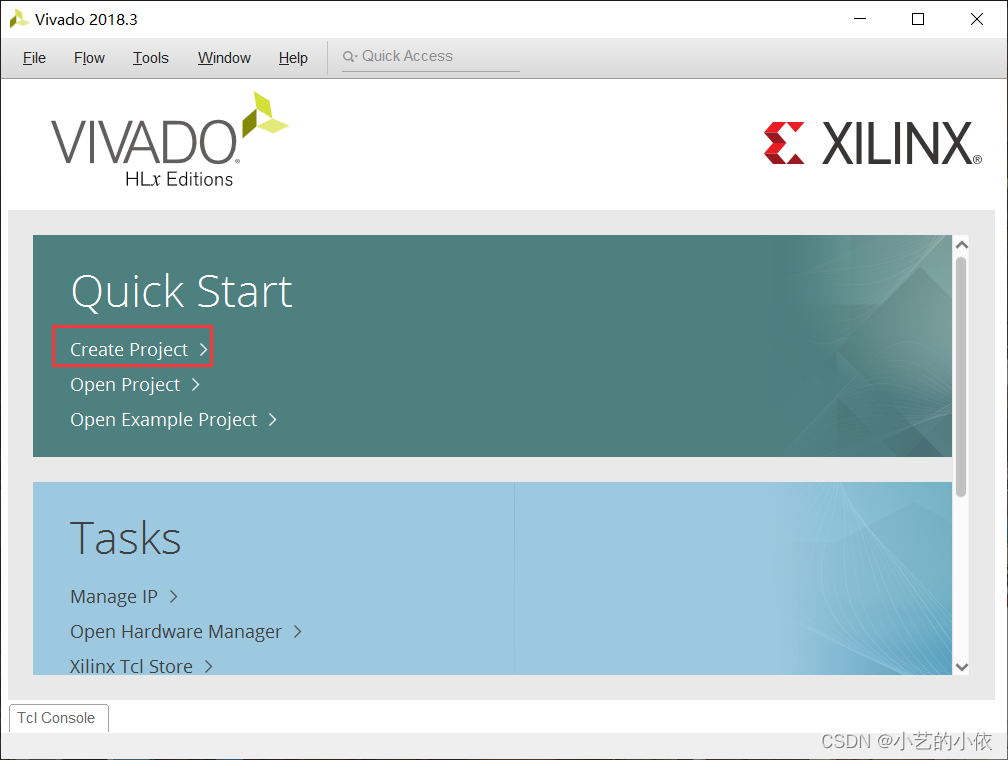

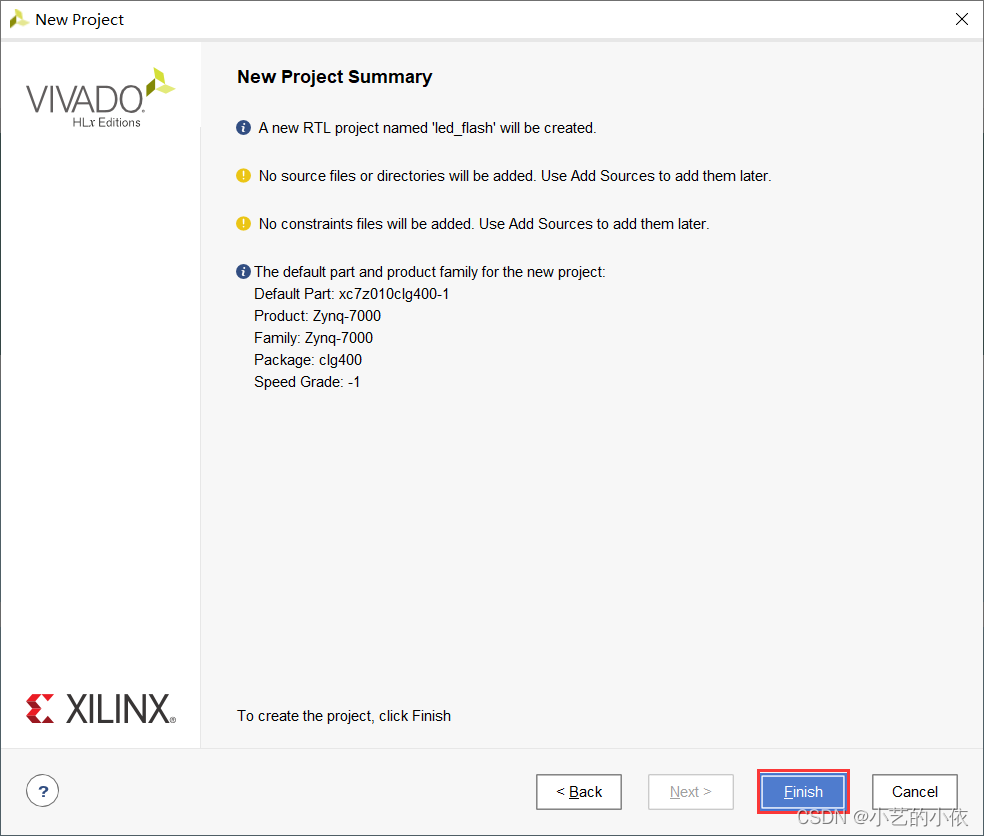

创建vivado工程

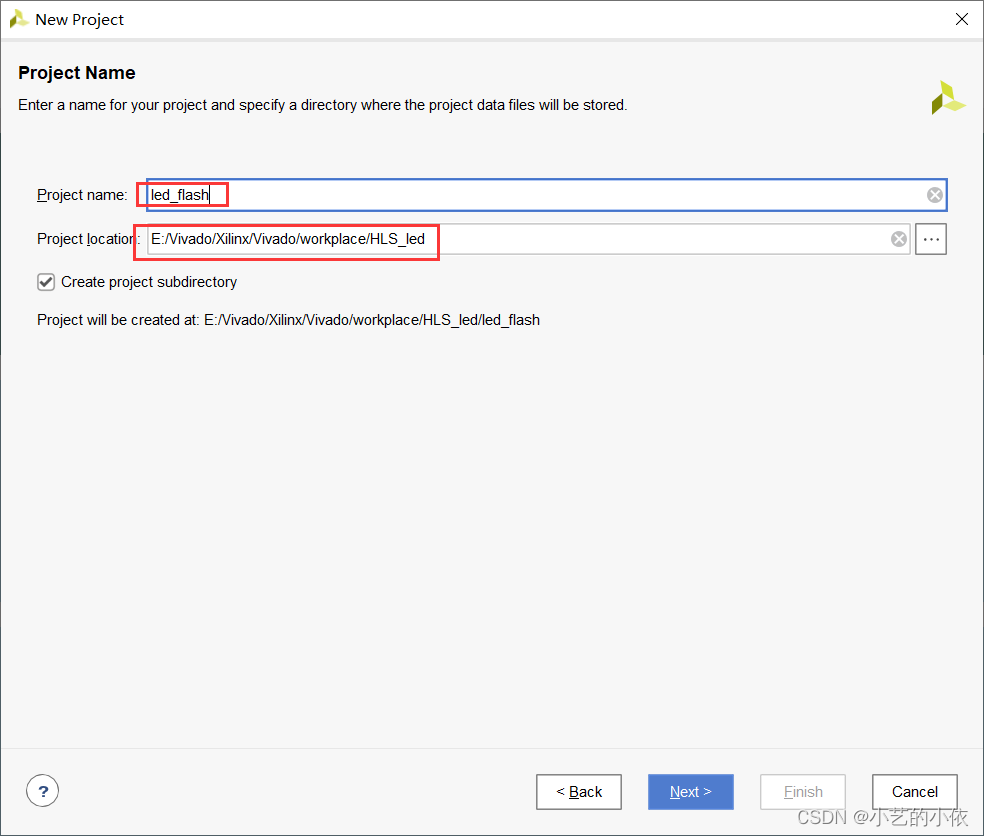

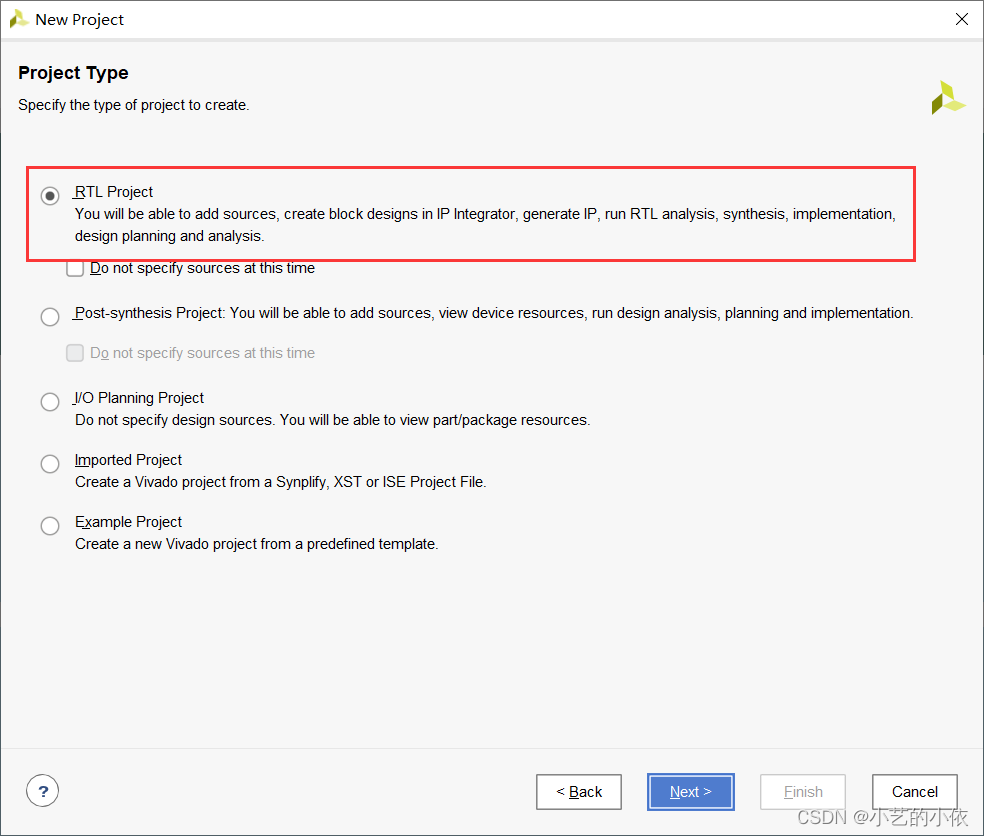

建立工程名及工程位置

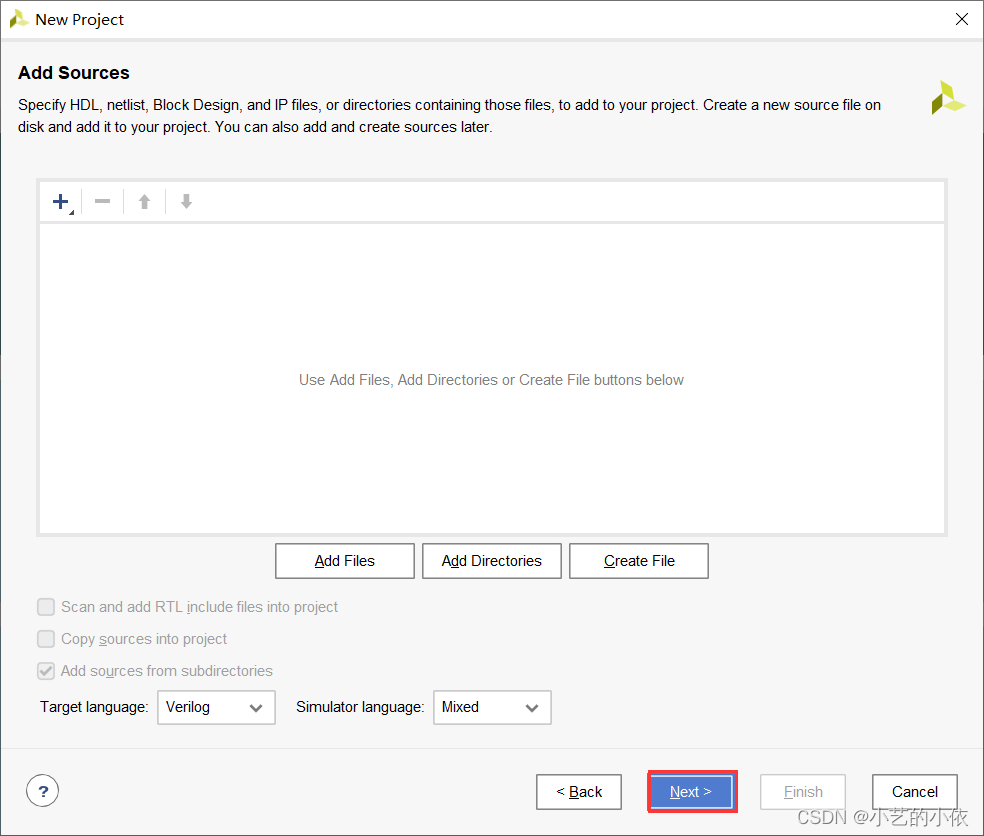

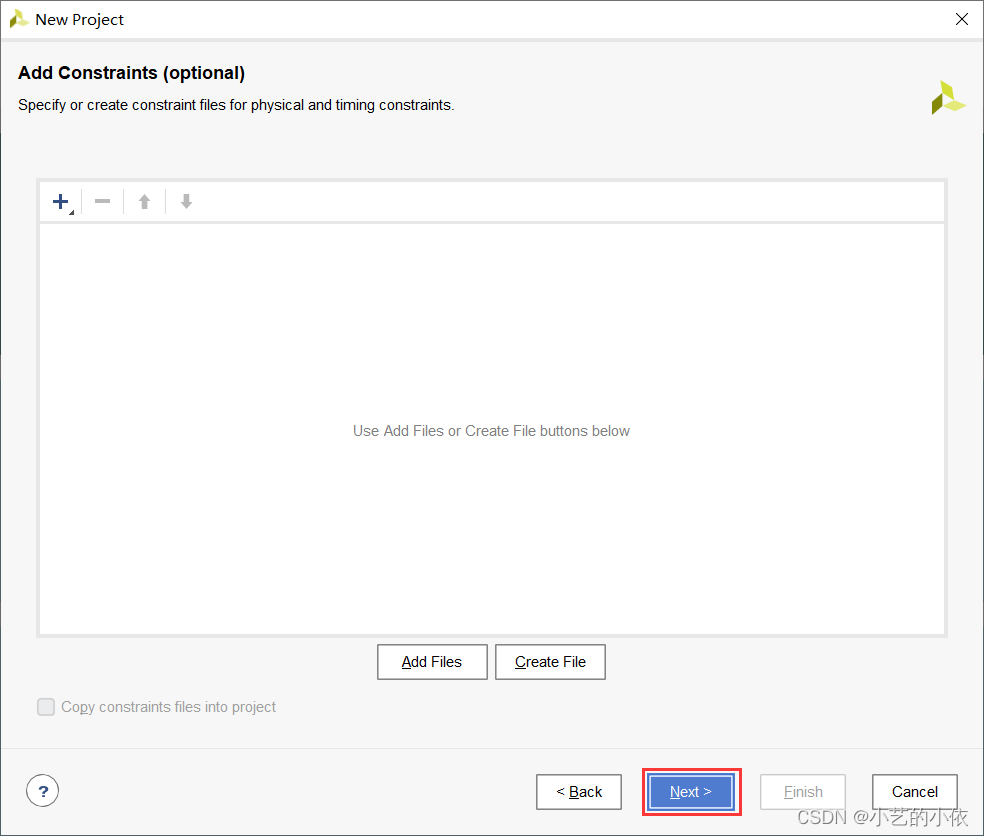

source和约束文件保持默认

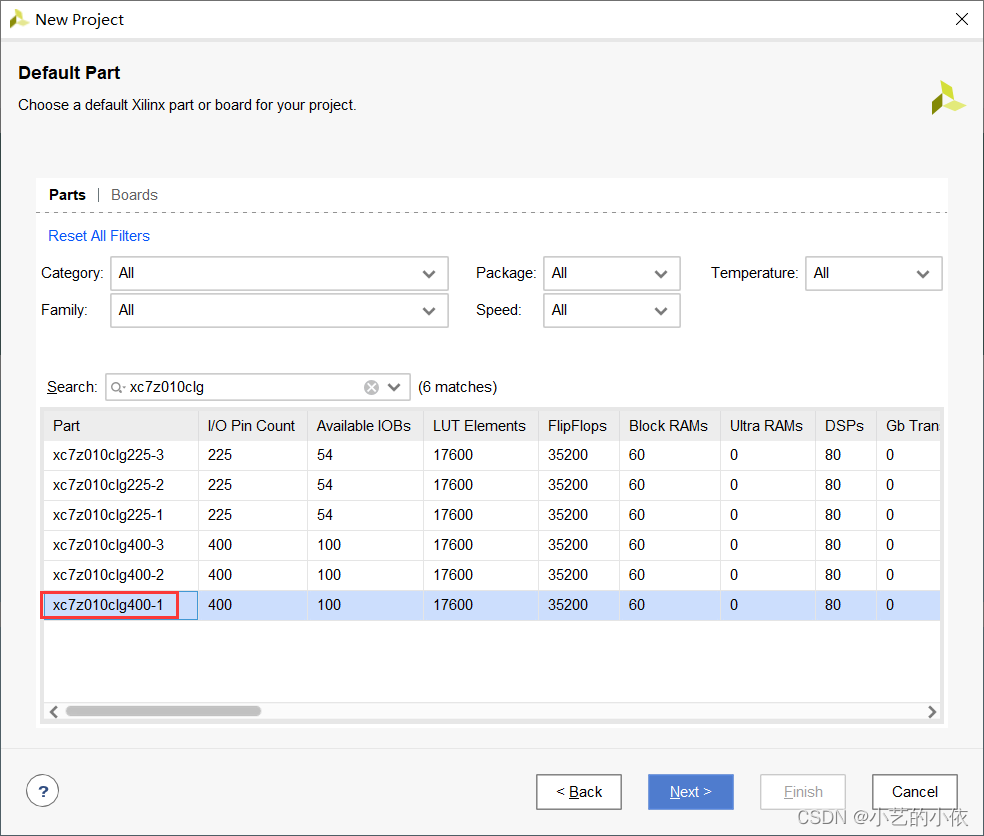

选择器件,同HLS工程的器件相同

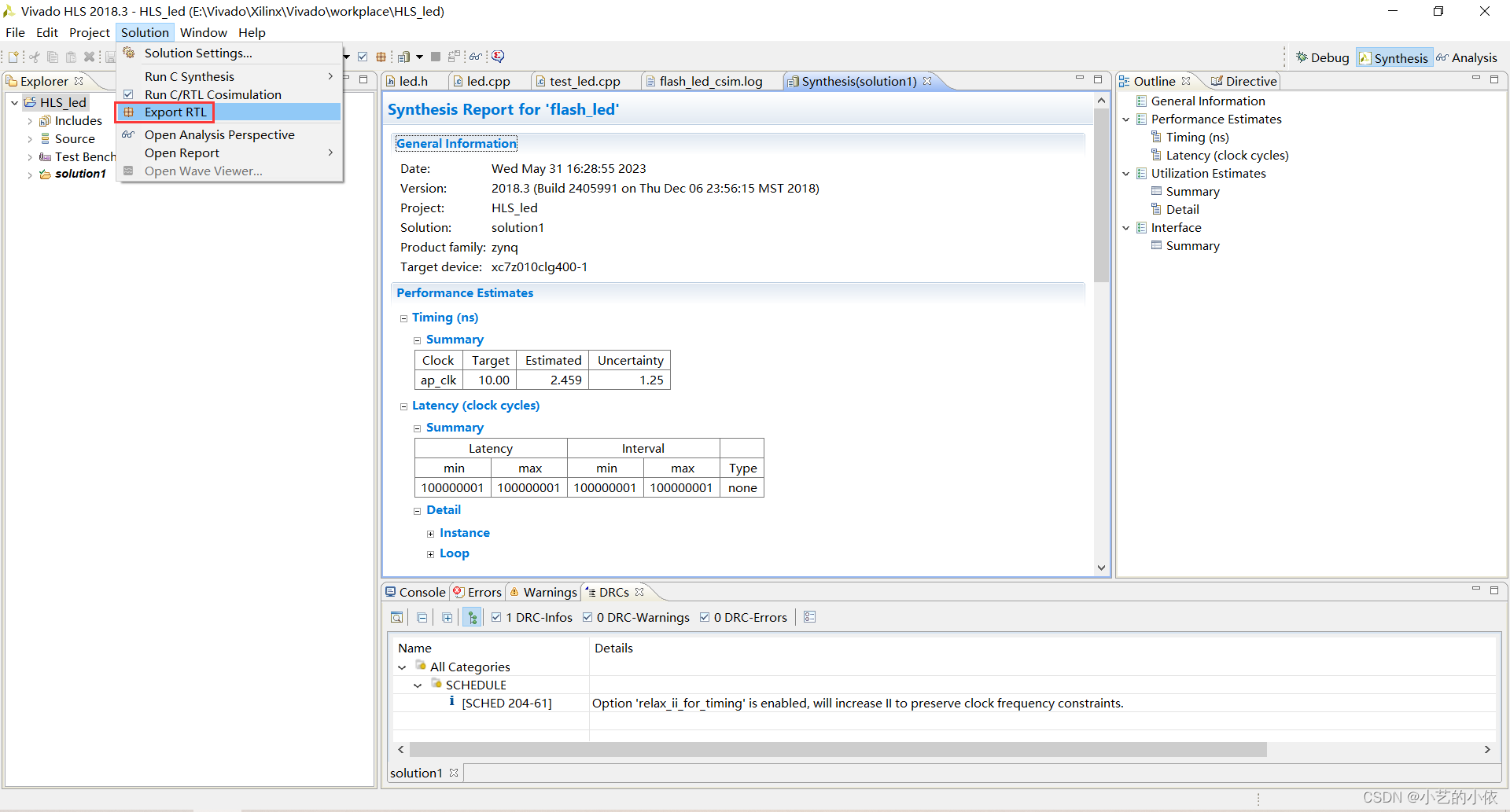

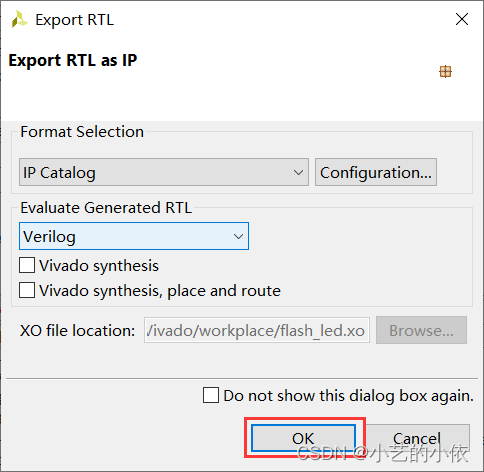

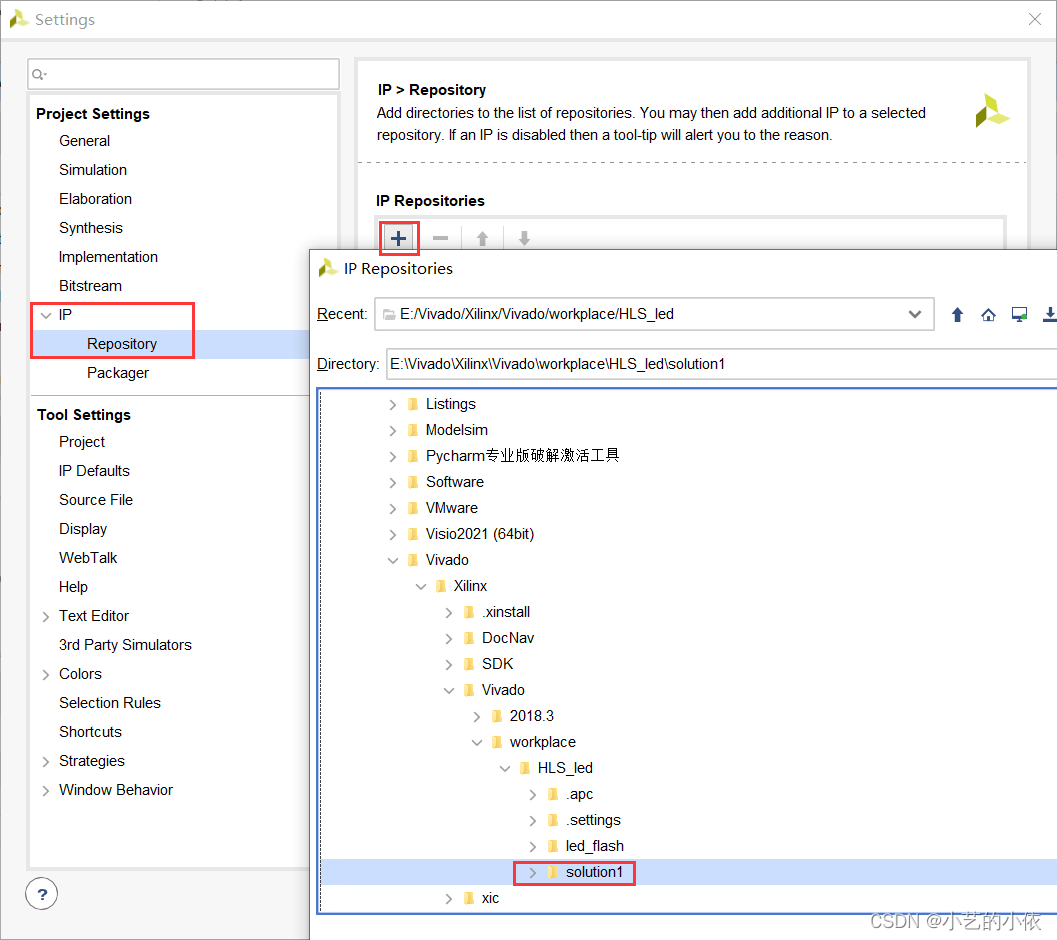

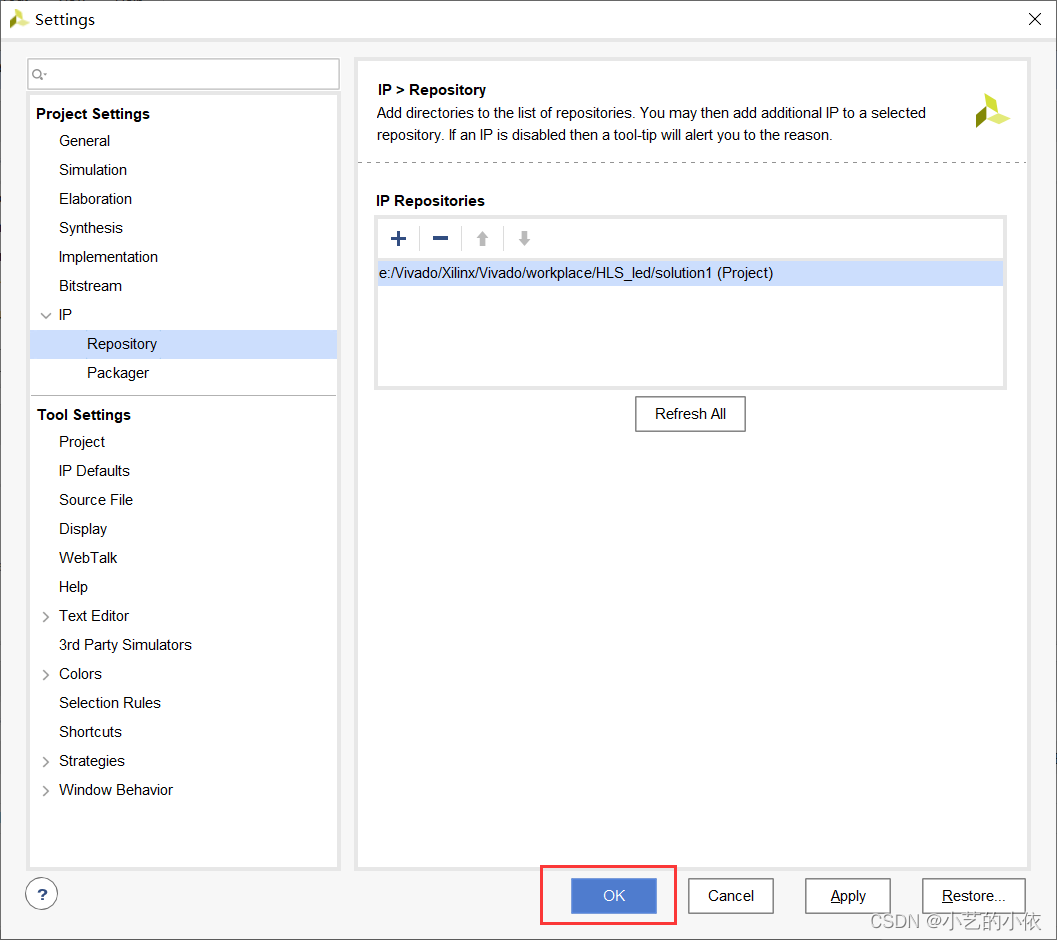

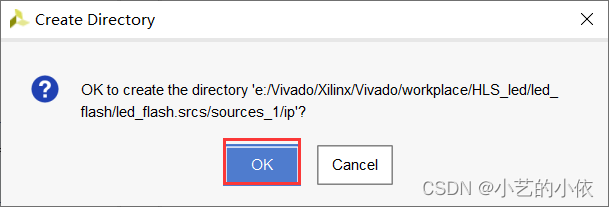

导入HLS生成的IP核

引入IP核

首先是之前那个应用

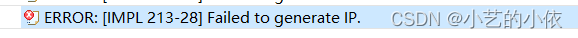

PS:若此处出现了如下错误

这里给出比较快捷的方式,若要查看原理或细节,这里推荐一篇博客

Vivado HLS生成IP核报错的解决方案

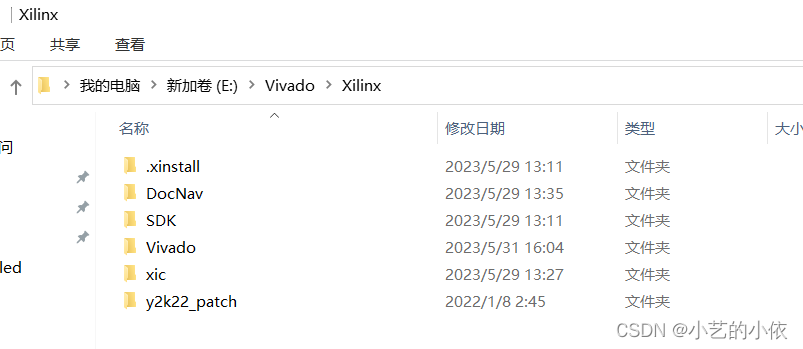

首先进入网站https://support.xilinx.com/s/article/76960?language=en_US,找到这个压缩包,点击下载,然后解压到Xilinx的下载位置,然后删除压缩包节约空位

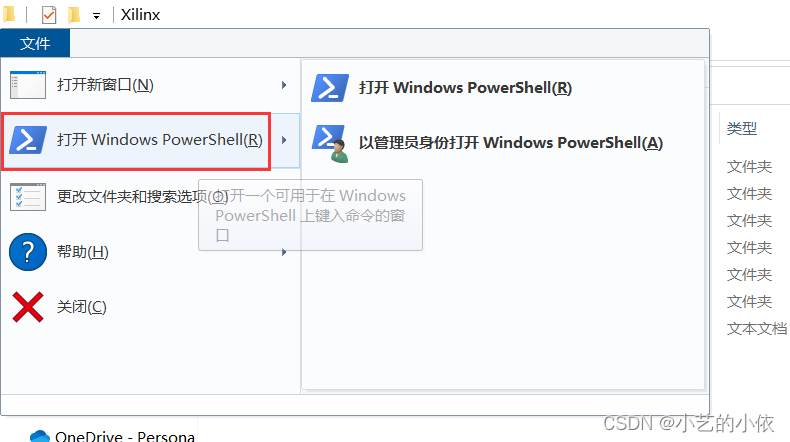

点击这个文件夹左上角的文件按钮,进入PowerShell,

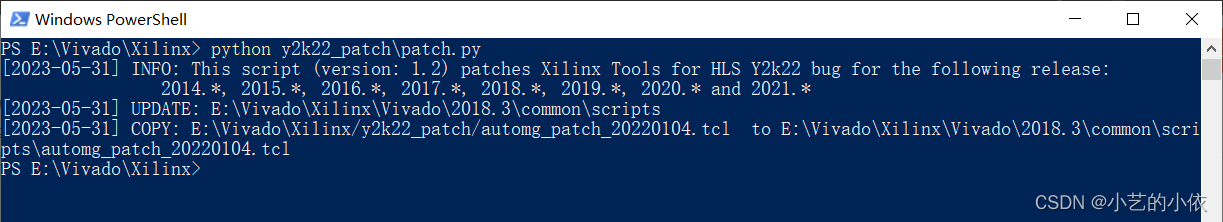

输入命令

python y2k22_patch\patch.py

打印如下内容就是可以了

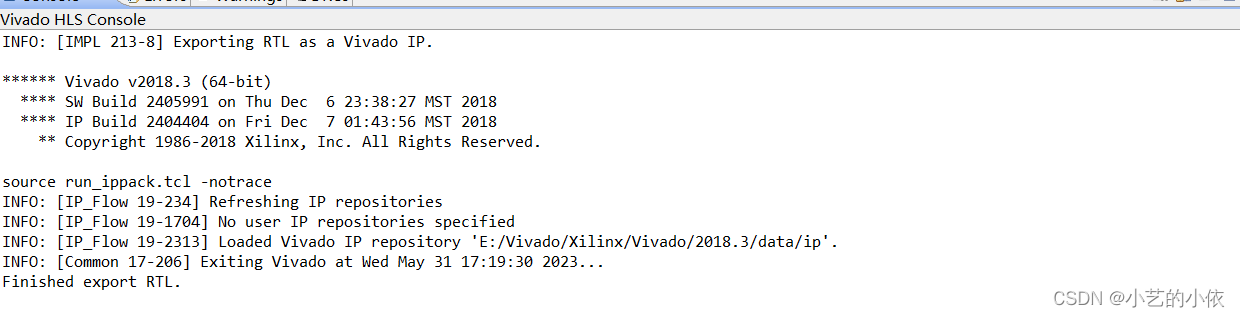

此时重启Vivado HLS,再次重复引入IP核的部分

回到正题

此时出现了如下输出

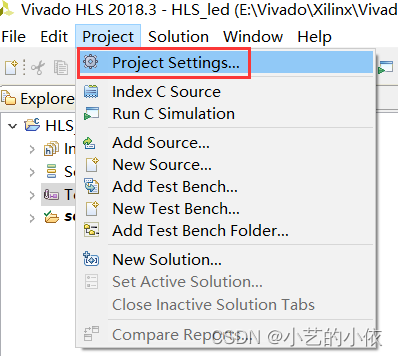

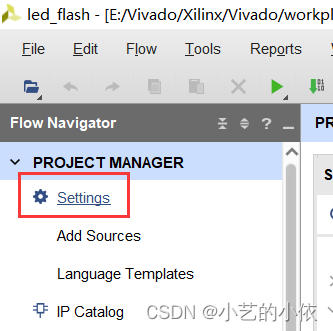

进入Vivado,点击setting

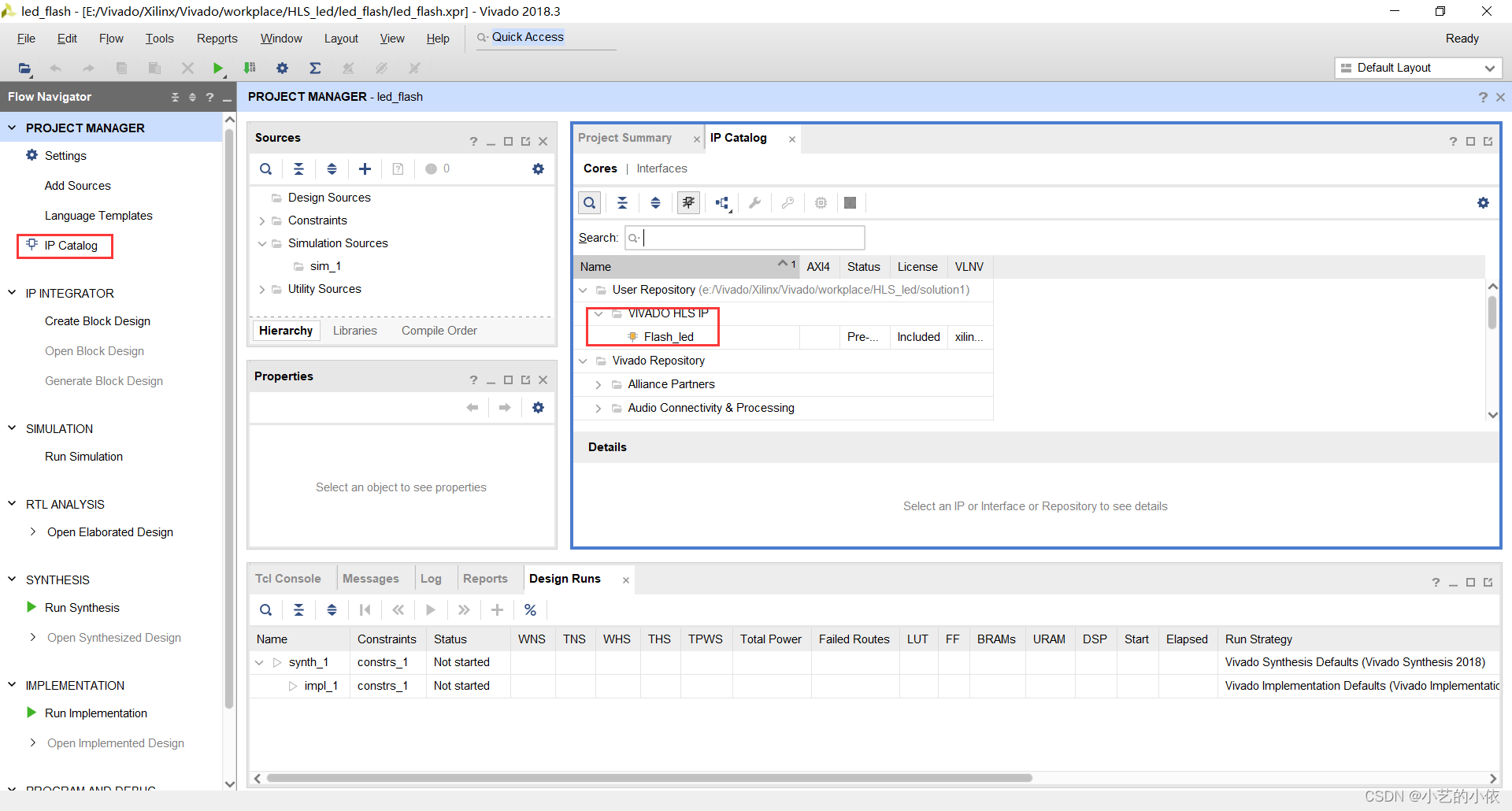

这里可以看看IP核是否成功,如下图就是成功了

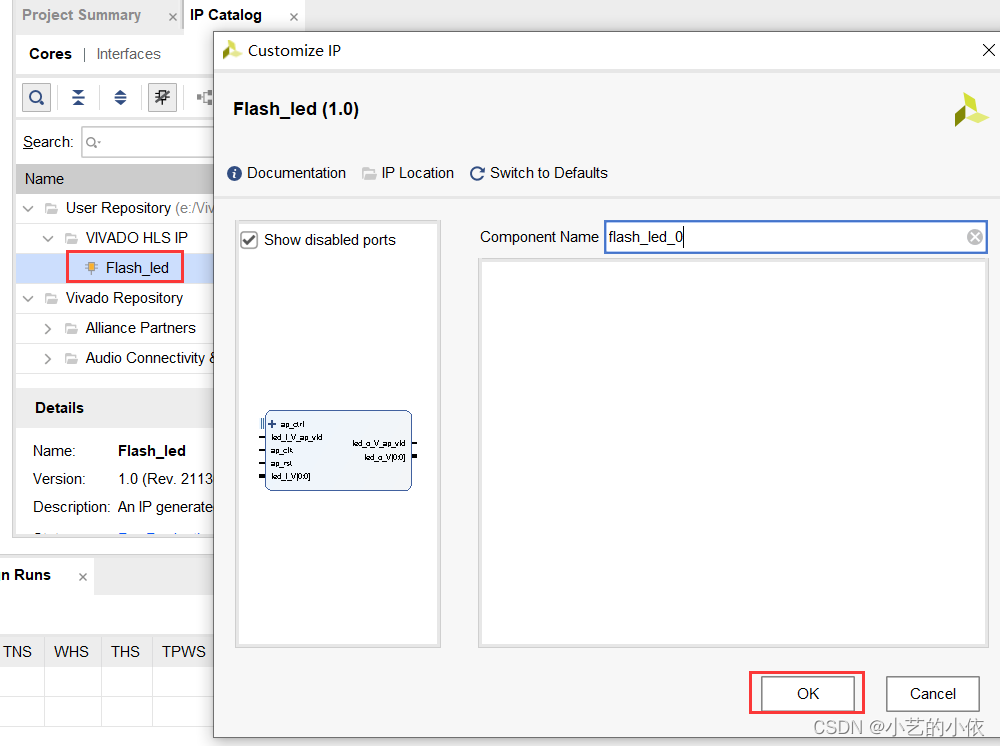

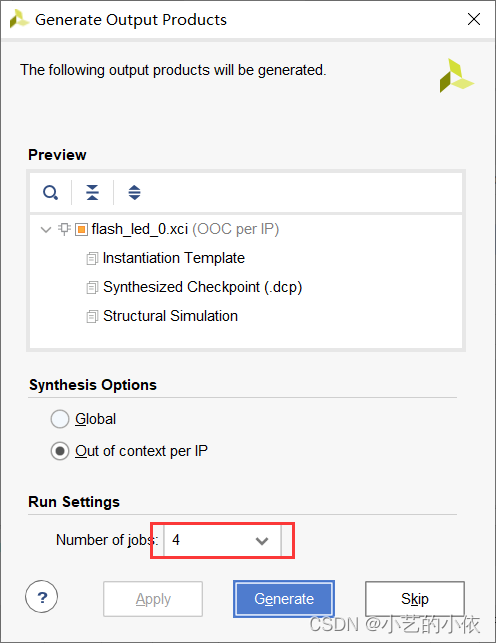

生成IP

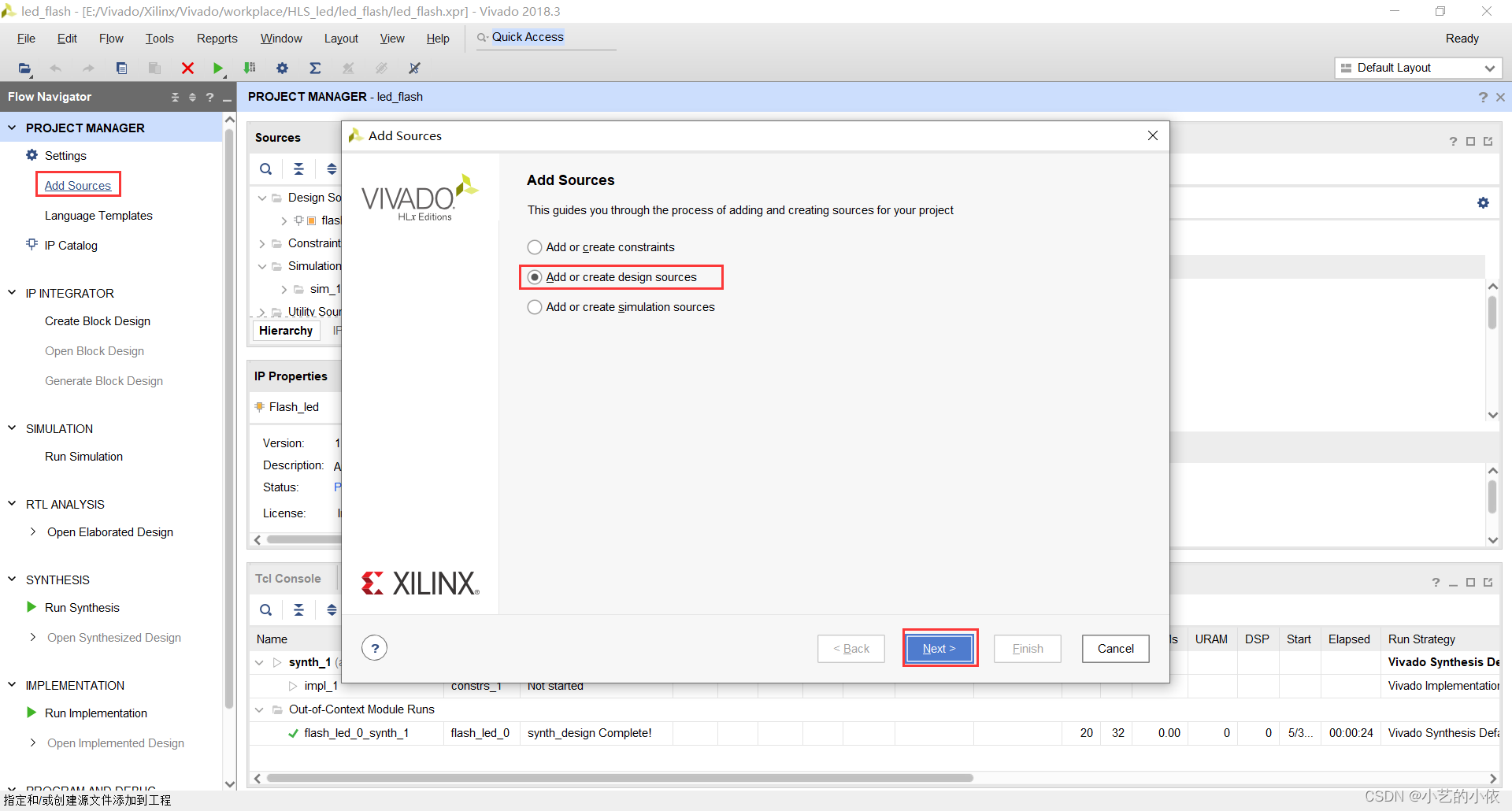

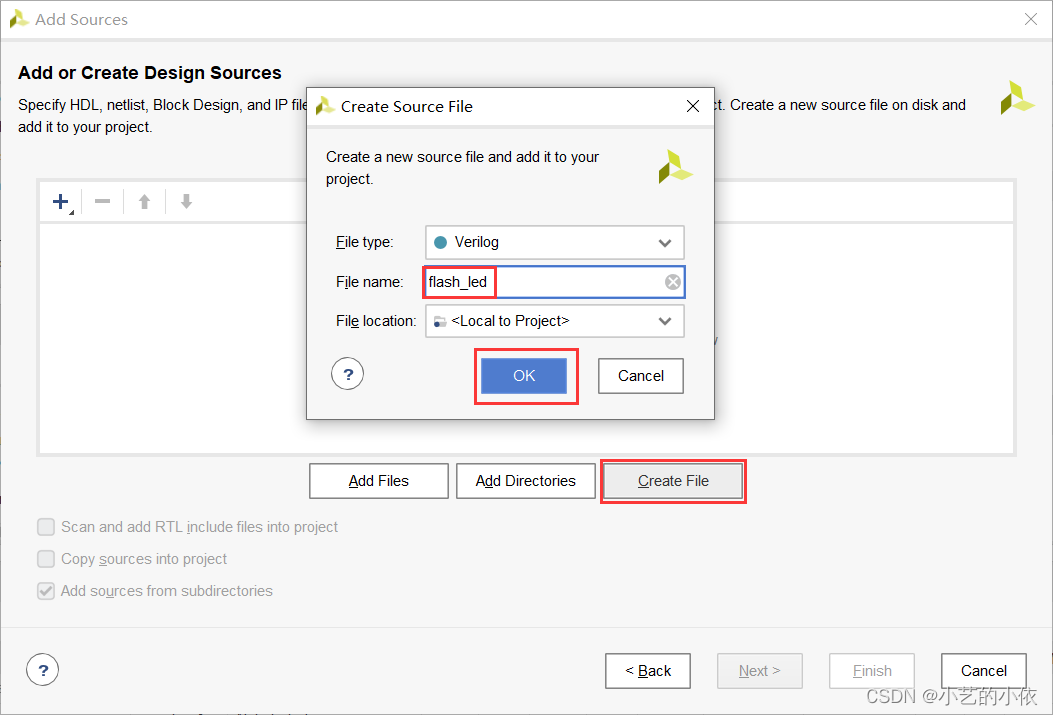

添加实验代码

代码内容

`timescale 1ns / 1ps

module flash_led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;//同步复位

wire ap_ready ;//当前可以接收下一次数据

reg ap_start ;//IP 开始工作

reg led_i_vld ;//输入数据有效

wire led_o_vld ;

reg led_i ;//输入的 led 信号

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign rst = ~rst_n ;

assign led_o = led_o_r ;

//----------------delay_cnt------------------

always @(posedge clk) begin

if (rst==1'b1) begin

delay_cnt <= 'd0;

end

else if(delay_cnt[1]==1'b0) begin

delay_cnt <= delay_cnt + 1'b1;

end

end

//----------------ap_start------------------

always @(posedge clk) begin

if (rst==1'b1) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

//----------------led_i_vld------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

//----------------ap_i------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_V_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.led_i_V_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o_V(led_o_r), // output wire [0 : 0] led_o_V

.led_i_V(led_i) // input wire [0 : 0] led_i_V

);

endmodule

约束文件编写

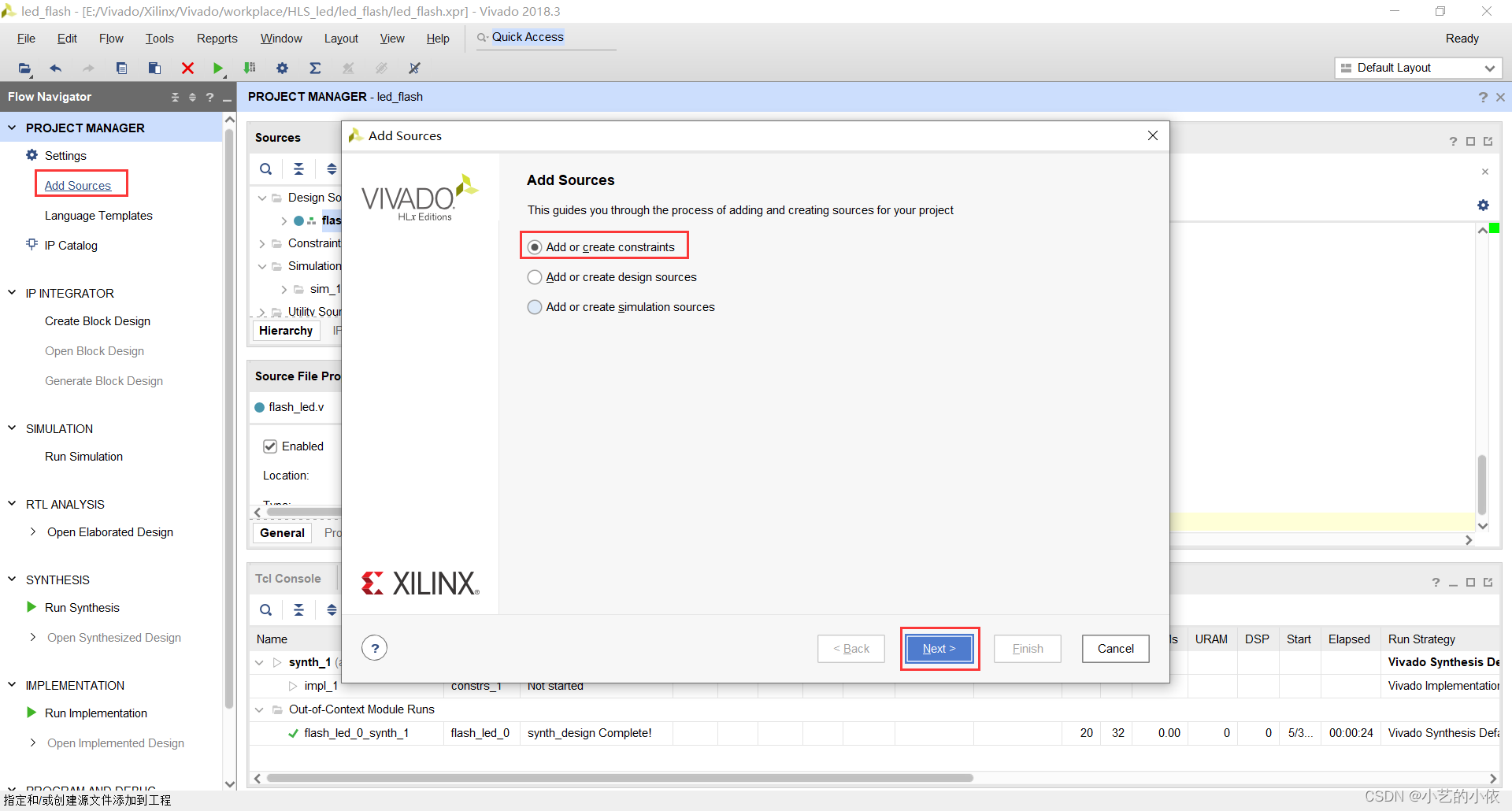

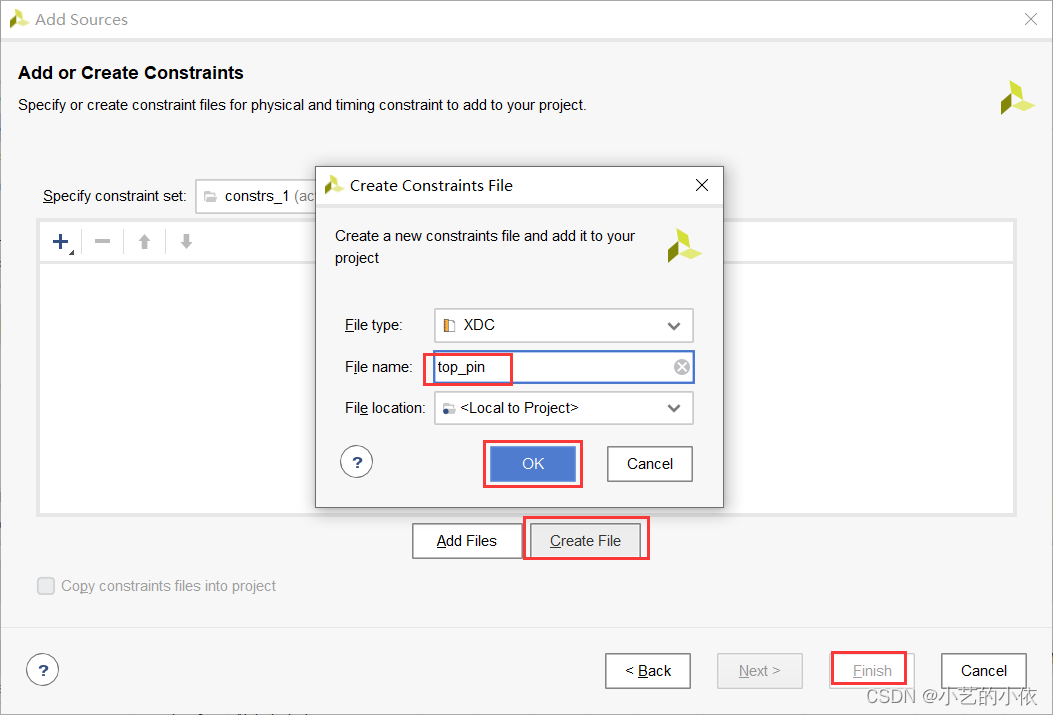

创建约束文件

代码内容如下

##############LED define##################

set_property PACKAGE_PIN P15 [get_ports {led_o}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_o}]

##############Reset define##################

set_property PACKAGE_PIN P16 [get_ports {rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

##############50M CLK define##################

create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

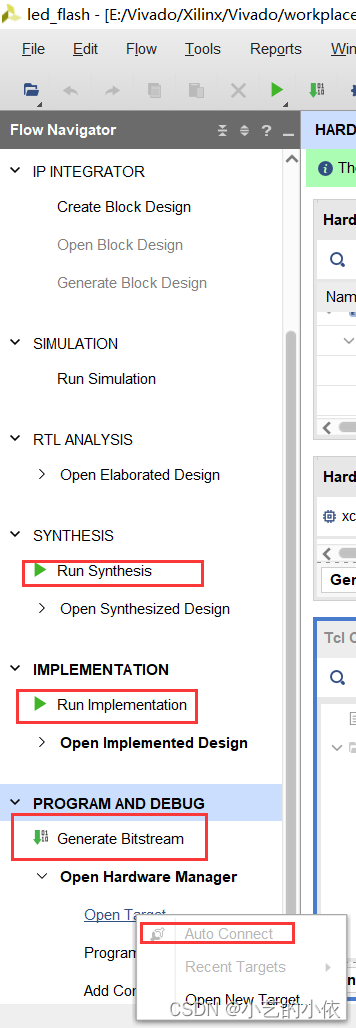

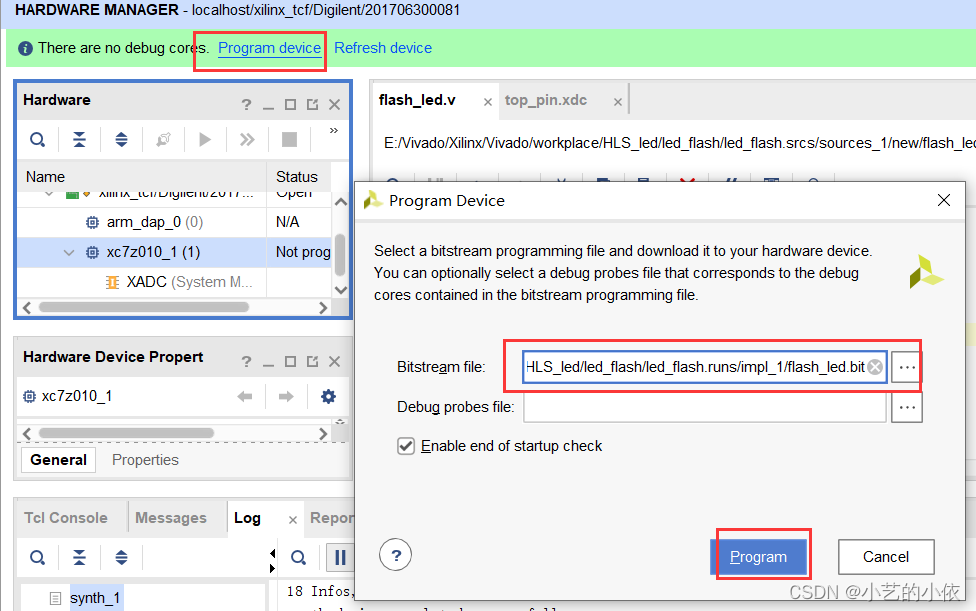

编译生成结果

注:这里开始要接线实验了

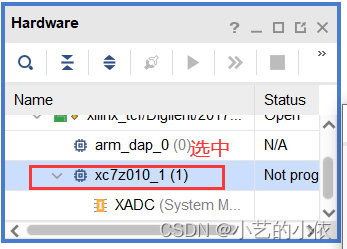

这里照着红框从上往下点

结果展示

总结

这次实验还是很有意思的,就是有点麻烦,步骤太多了。感觉还是不熟练,等熟练了可能会好一点吧

参考

HLS实践

基于FPGA实现LED的闪烁——HLS

Vivado2018.3的下载安装

【嵌入式系统应用开发】FPGA——HLS入门实践之led灯闪烁

Vivado HLS生成IP核报错的解决方案

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?