本文暂只针对于8086的存储器的奇偶分区进行讨论,篇幅不大。

相关总线的概念

总线,通俗的说,就是CPU与其他部件传输信息的线路。

英文叫做BUS,可能会想到公交车,姑且这么认为的话,我们对比一下:

不同公交车有规定的线路,作用的运输people,组成了一个大的交通线路。

引脚与引脚之间也会有固定的路线,传输的是信息,这些线路形成了总线结构。

总线根据传送的信息,可以进行分类。

- 地址总线:AB, address bus

- 数据总线:DB, data bus

- 控制总线:CB, control bus

下面先对它们做一个,不算很详细的介绍。

地址线

寻址用。

设条数为n,一般可存储

2

n

B

2^nB

2nB 的存储空间。

地址,电脑中存储的信息,都存放在了不同的位置,将这些位置用数字命名,也就是进行编号,形成了不同地址,编号就是地址码。

CPU与寄存器、存储器,外设的连接,怎么判断我连的是谁?如果我要拿电(传送个电信号之类的)刺激它,刺激哪个部位?…

我的意思是,读取数据,或者写入数据总得知道是哪个区域,再对其进行操作,也就是要寻找到正确的单元。

因而,会有一类线路,代表CPU到达各单元的走向,最终定位到要操作的信息的位置,这个过程,叫做寻址。

这类线路,从用户角度看,进行着关于地址的操作,像是在传送地址码信息,故叫做地址总线。

数据线

传送信息用。

地址线最终定位到的位置,就是某个存储单元,这个单元存放着0与1组成的信息。如果是一位存储单元,就只能存放0或1两种信息,如果是4位呢?自然就可以形成

2

4

2^4

24 中情况的信息。

既然寻着地址找到了单元,自然是要读取这些信息,或者送过来信息覆盖原来信息,换句话说,就是为了读写数据。有一类线路专门用于传输数据信息,这类线路就是数据线。当然,为了省点材料,可以考虑把数据线和地址线公用,前一时刻传送地址,下一刻再传送数据。

一个存储单元,有多少位,一次就可以传送多少位的信息,这每个位都是并行的。

控制线

有的时候,这块区域不允许读取、写入操作,或者说,寻址的时候,我不在地址范围内,我把信号屏蔽了,被隐藏起来,CPU就会只去寻找那些没被隐藏的线路,从而找到最终的单元。

对于存储的控制信号,主要有:读信号、写信号、片选信号等。

字信息的存放

对于8086,虽然是16位处理器,但是其存储器却是按照字节组织的,即,最小存储单元为1Byte = 8位,因此,编址的时候,一个字节有唯一的一个地址。

8086又有20条地址线,所以可以寻址1MB(

2

20

B

2^{20}B

220B)的存储空间。

字节与字节的存放

一般而言,存放的8位信息,就按照地址递增的顺序存放即可,一个地址一个字节。

而如果是字的存放,就要占据2个地址了,低8位字节放在低地址,高8位放在高地址中。

规则存放与规则字

对于存放的字(16位),低位字节的地址若是偶数,这种存放方式称为规则存放,而这种情况下,被存放的字信息也被叫做规则字。

反之,可得出非规则存放与非规则字的概念。

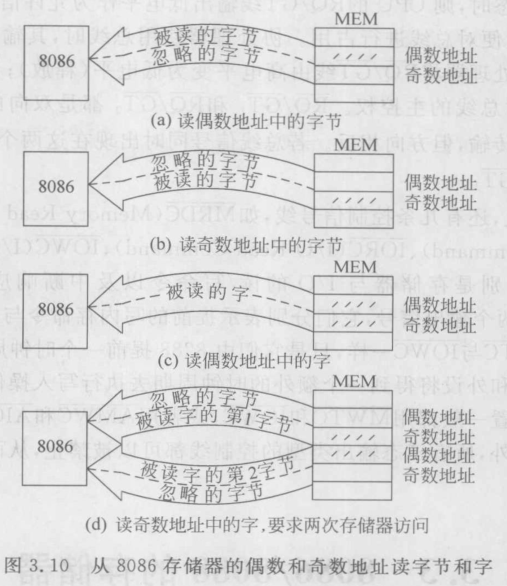

对于,规则字的读取,我们可以一次就取完,非规则字却需要分两次,因为我们一次按字的读写,总是从偶地址开始的。

奇偶存储体

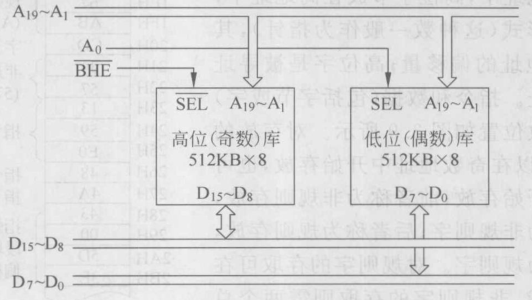

8086是按字节组织的存储器,但是8086本身却是16位的,所以我们只需要,将两个8位的并在一块,就可以形成16位的,这样,既满足按字节组织,又可以实现一次16位的读取。

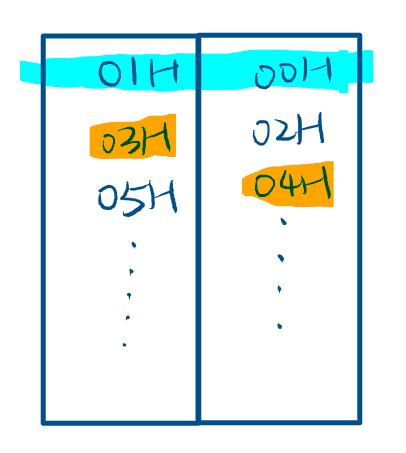

所以8086的1MB的存储空间,实际上被分为了两个512KB的存储体,又称存储库。16位的8086就会低8位对应一个库,高8位对应一个库,如果是一个字(16位),就会对应两个库。

其中,低位库中的每一个地址都是偶数地址,高位库的每个地址是奇数。

这也不难理解,存储器按字节组织,地址的最低值一般为00H,那么下一个地址是01H,而8086是16位的,按道理,一次读写是两个字节,因此会将两个并排地址的字节形成一个字,而这个字的地址自然是以低字节地址为准,为表示出是字读取,地址前面补两个0即可,即0001H。

这样一来,为何规则字的读取只需一次,非规则字(低地址为奇数)却需要两次,也就显而易见了。

奇偶存储体的片选

什么时候读偶存储体,什么是时候读奇存储体,从指令上,我们可以很容易理解。背后的硬件又是什么机制?限于篇幅,不做深入的分析,不过,当我们学完存储器的相关专业知识,自然就会理解了。这里,只简单提及奇偶库的选择。

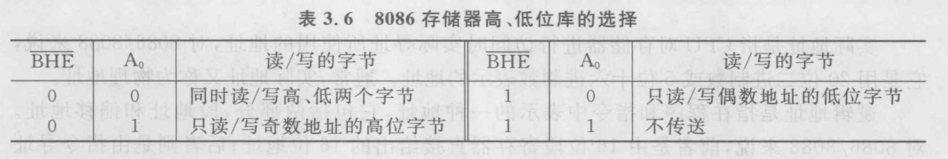

8086CPU是通过两个引脚输出信号,以控制奇偶存储库的选择的,这两个引脚为

B

H

E

‾

与

A

0

\overline{BHE}与A_0

BHE与A0这两个引脚。其中,带上划线的表示低电平有效,低电平触发的意思,所以,

B

H

E

‾

\overline{BHE}

BHE置0有效,

A

0

A_0

A0置1有效。

但是存储器的片选端 C E ‾ \overline{CE} CE通常是低电平使能的,因而,存储器与CPU直连的设计下,CPU的输出信号,通常就以输出0为选择标准,除非不是直连,中间加了一些逻辑。

这样,下表的记忆也会更容易理解。

两者组合会出现4种情形,8086对之进行了约定:

Finally

本文论述并不严谨,出于个人理解,若要深究更为严格的概念,可研读相关书籍,或自行查阅相关资料。

若想内容更好,也欢迎指正~

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?