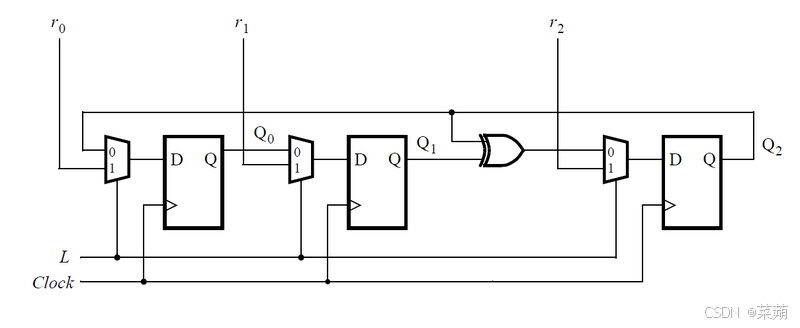

Consider the sequential circuit below:

Assume that you want to implement hierarchical Verilog code for this circuit, using three instantiations of a submodule that has a flip-flop and multiplexer in it. Write a Verilog module (containing one flip-flop and multiplexer) named top_module for this submodule.

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

reg d;

always@(*)begin

case(L)

1'b0:d=q_in;

1'b1:d=r_in;

endcase

end

always@(posedge clk)begin

Q<=d;

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?