前言:

本人系2021级小白,电子信息类学生,学校有芯片设计实验班——龙芯班然后我就加入了成为龙芯班第三届学员。学习完成加法器状态机等之后就开始跟着《自己动手写CPU》雷思磊著,此后都是跟着这本书在学。学期末的时候到第四章。寒假1月完成所有指令。2月完成中断。本来打算做功能测试的,但是不会做卡住了,一直卡到4月(其实摸鱼了)

# 开始功能测试:

1.看相关文件,学习怎么做:

大量找资料,以下可供参考:

- 大赛包所有文件看一次

- 龙芯班学长录的视频:自己动手写CPU之后快速上手功能测试_哔哩哔哩_bilibili

- 龙芯官方录的视频:NSCSCC2019 第一次线上培训_哔哩哔哩_bilibili (推荐大家看2019年的因为20年讲的没有19年全)

- 历届龙芯杯培训视频_哔哩哔哩_bilibili

在做的过程中也遇到好多问题,然后就疯狂上网找...还有找到一些,我觉得挺有用的。有时候,就算这些文档没有帮到你,但是你看着全网有这么多人和你一起,为它欢喜为它愁,有时候还挺感动的...

- (6条消息) 龙芯比赛vivado调试试错手记_zerolord的博客-优快云博客_vivado断点调试

- 封装SRAM-SOC - 重庆大学硬件综合设计实验文档 (cqu.ai)

- 单周期cpu功能测试 - 计算机设计与实践(2020春季) | 哈工大(深圳) (gitee.io)(这个就浅浅参考一下就可,与龙芯杯的有好几处不太相符,毕竟人家只是自己学校用)

2.改接口

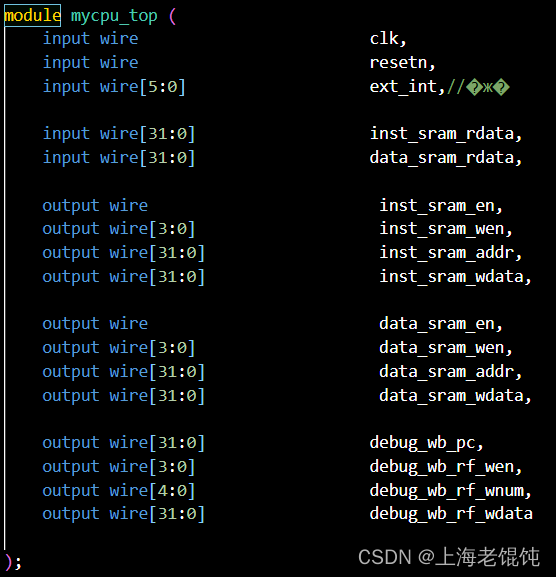

先弄sram接口吧,从里面可以看到它的顶层模块有这样的接口,我们要不就改以前的openmips,要不就重写...

openmips.v作为cpu的顶层模块,按照龙芯杯的命名结构应该叫mycpu_top.v(是错的!应该是openmips_min_sopc.v)

由于我太菜了不会写,所以我还是改吧

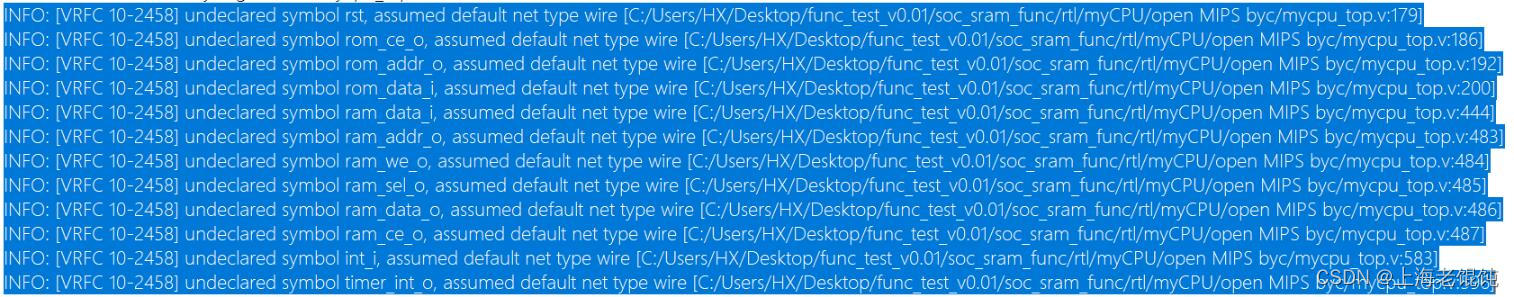

通过观察和浅浅联想一下,我们不难发现 inst_sram和rom有关,然后data_sram和ram有关,然后具体每个接口是什么意思我们参考网上大佬的帖子(重大那个)知道了,然后我就拿我的openmips.v一顿猛改(其实是运行的时候报错找到的),下图为不完全统计(∩_∩)

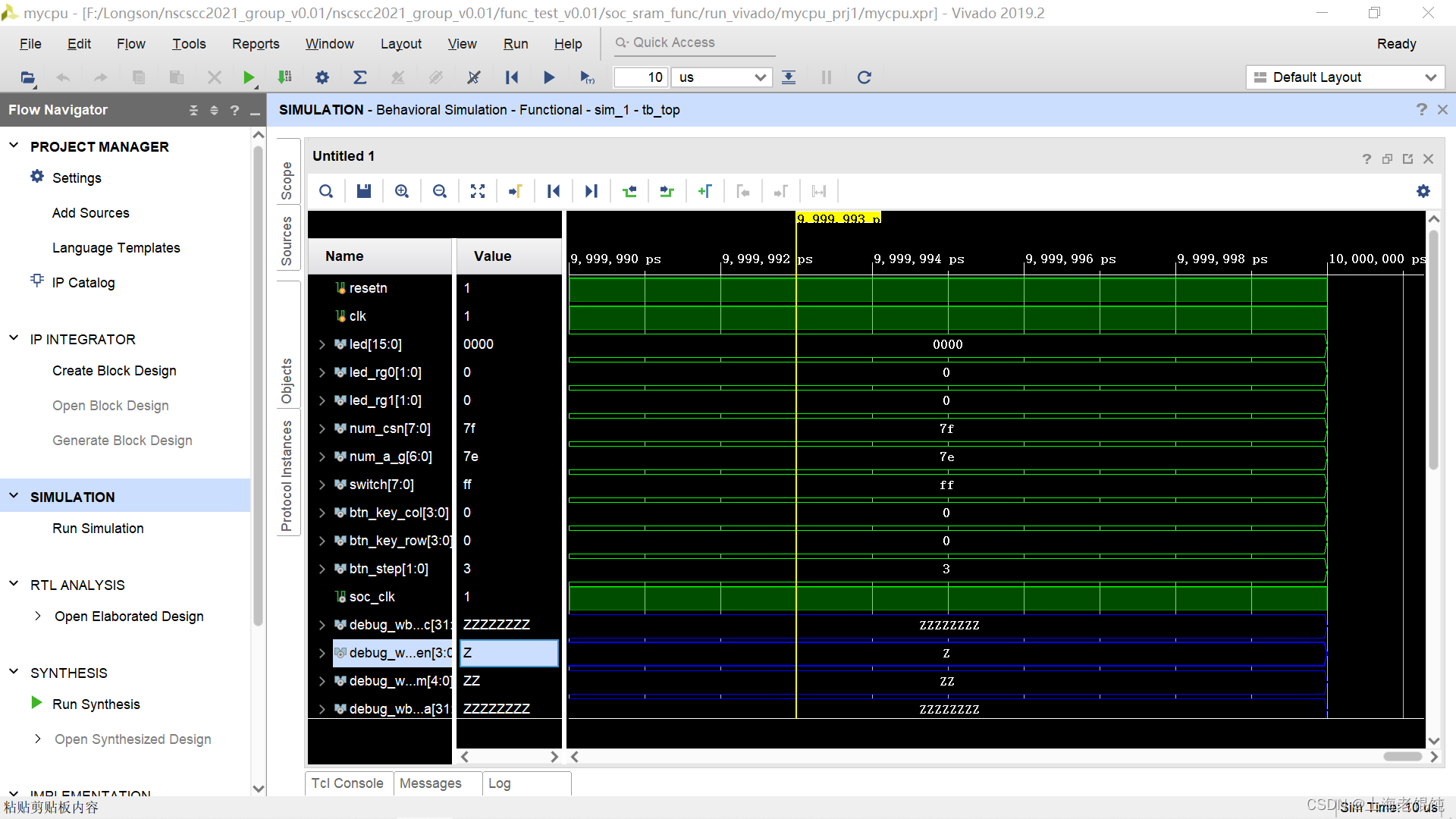

这些改完后,暂时是这 看大佬帖子以后才知道是抽出回写阶段的结果用来trace比对的,那就接吧,但是我不会接.....

看大佬帖子以后才知道是抽出回写阶段的结果用来trace比对的,那就接吧,但是我不会接.....

认真思考,把回写阶段的慢慢引出来,但是我发现!

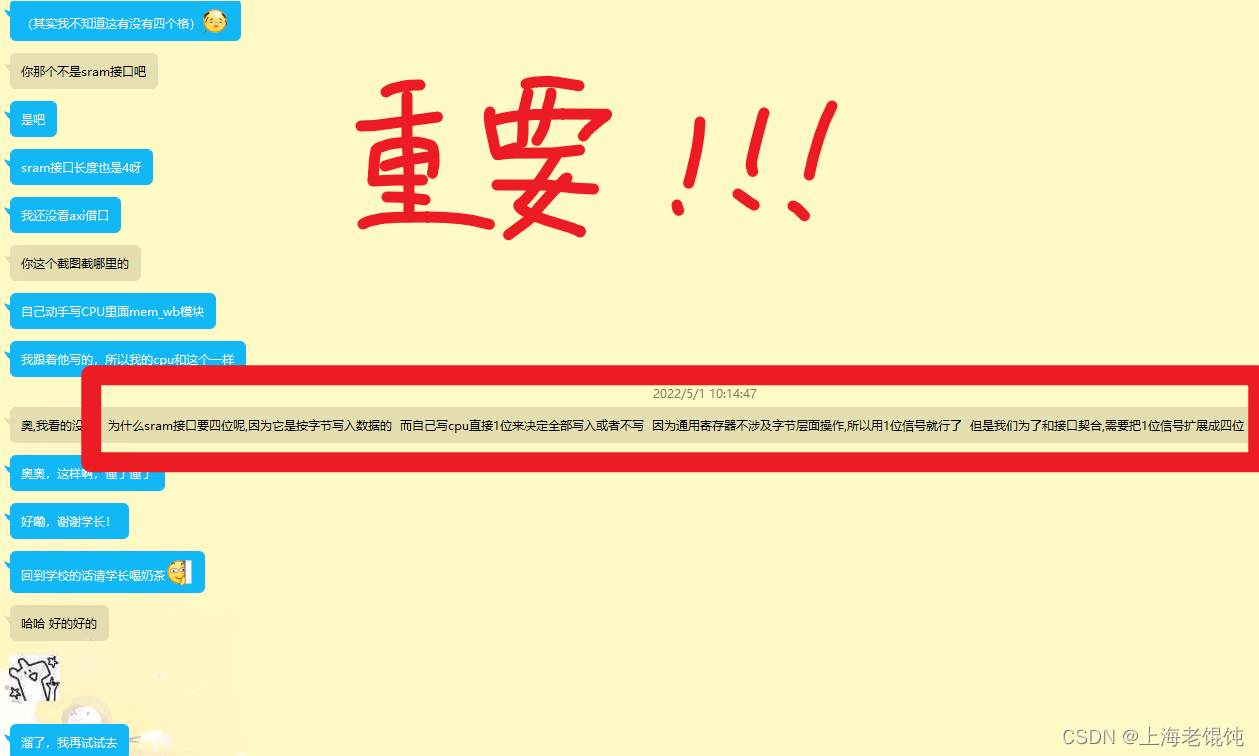

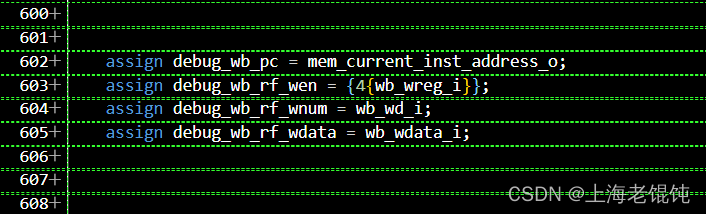

寄存器写使能的接口debug_wb_rf_wen是4位,但是跟着雷思磊的我们的mycpu的接口是1位!

然后我去问了学长(感谢左学长!!!!开学了一定请他吃饭!!!!多次麻烦他了!!!)

在mycpu_top.v模块增加(我后来又改了....见后文)

小tips: 这里再说一下,还是推荐用git对代码实行跟踪,这样你改的话也知道自己改了哪里,还可以回退到上一个版本,毕竟是试错。。。(说实话我以前从来不用,但是做到这一块突然觉得还是用了好啊,真香~)

本文记录了一位电子信息类学生参与龙芯杯系统能力竞赛的CPU赛道,从学习功能测试到解决各种接口问题的过程。通过查阅资料、观看视频,作者逐步解决了CPU设计中的接口适配、回写阶段接口、地址映射等问题,并在调试过程中不断学习和改进,最终成功完成功能测试。

本文记录了一位电子信息类学生参与龙芯杯系统能力竞赛的CPU赛道,从学习功能测试到解决各种接口问题的过程。通过查阅资料、观看视频,作者逐步解决了CPU设计中的接口适配、回写阶段接口、地址映射等问题,并在调试过程中不断学习和改进,最终成功完成功能测试。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1068

1068

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?