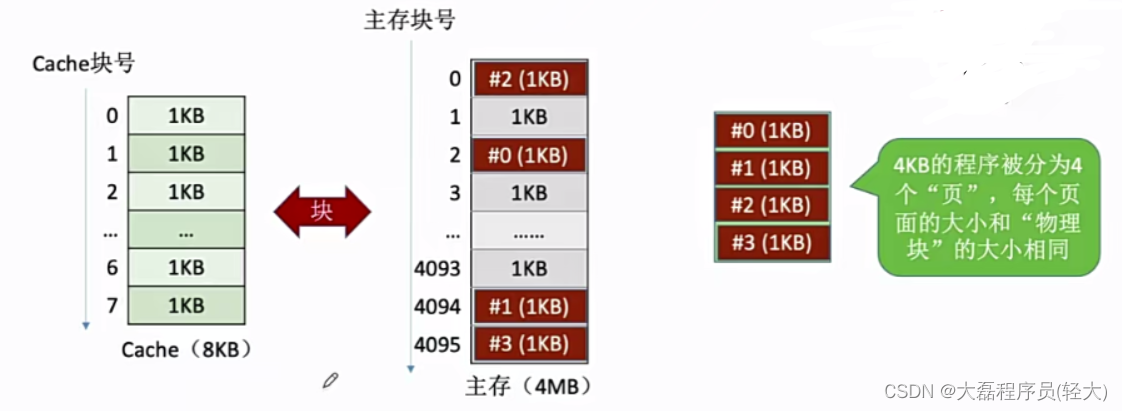

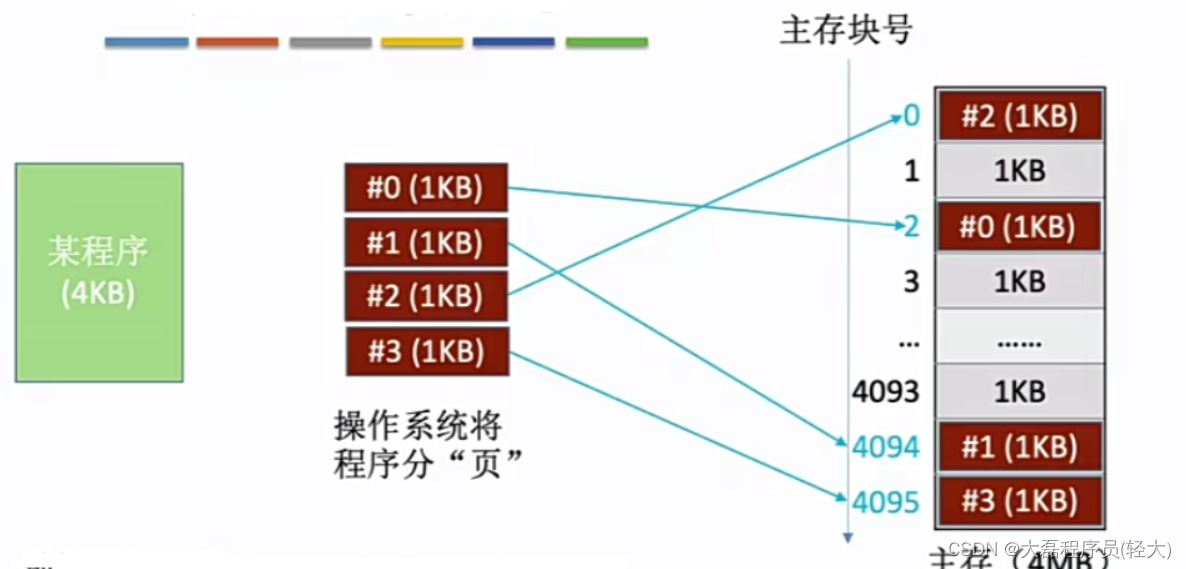

页式存储系统:一个程序(进程)在逻辑上被分为若干个大小相等的“页面”,“页面”大小和“块”的大小相同。每个页面可以离散地放入不同的主存块中。

虚拟地址VS实地址

逻辑地址(虚地址):程序员视角看到的地址。

物理地址(实地址):实际在主存中的地址。

程序员视角:整个程序共4KB=B,地址范围:000000000000~111111111111

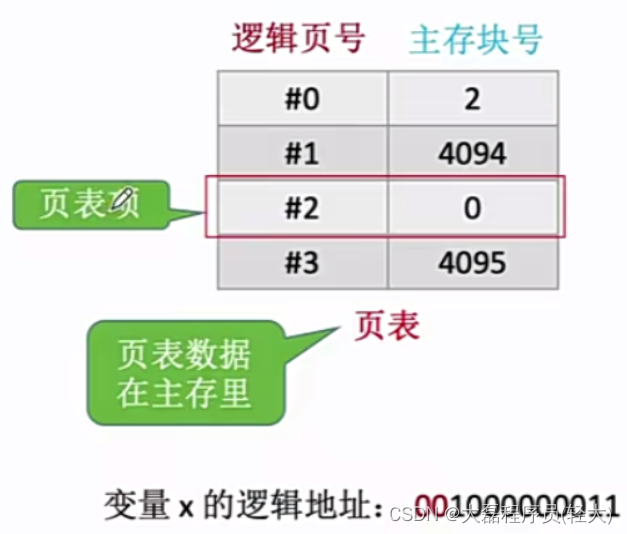

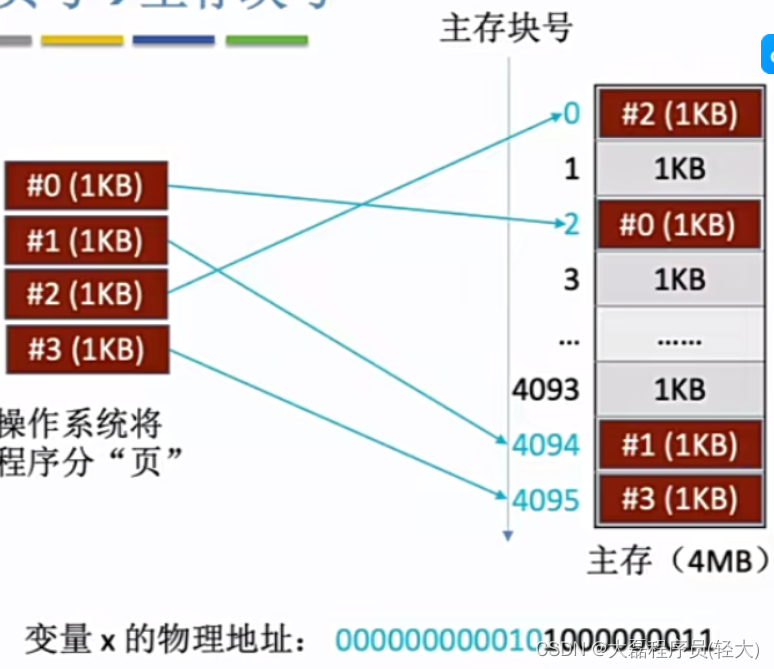

假设变量x的逻辑地址:001000000011

假设变量y的逻辑地址:110000001010

取变量x至ACC寄存器:

机器指令:000001001000000011(操作码+地址码)(使用逻辑地址)

如何判断变量x和y属于哪个分页:

可以将逻辑地址分为两部分(一部分是逻辑页号,一部分是页内地址)

在这个例子中,由于分为4个页,所以只需要取前两位作为逻辑页号,剩余10位作为页内地址

主存的物理地址共22位分为(主存块号12位,块内地址10位)

由第一张图的存储情况可知,变量x的物理地址:0000000000101000000011

变量y的物理地址: 11111111111110000001010

页表:逻辑页号-主存块号

操作系统会创建一个页面(一个数据结构)在主存中。页表的作用:记录了每个逻辑页面存放在哪个主存块中

页表中的每一项记录着一对逻辑页号和主存块号的相对位置

CPU执行的机器指令中,使用的是“逻辑地址”,因此需要通过“页表”将逻辑地址转为物理地址

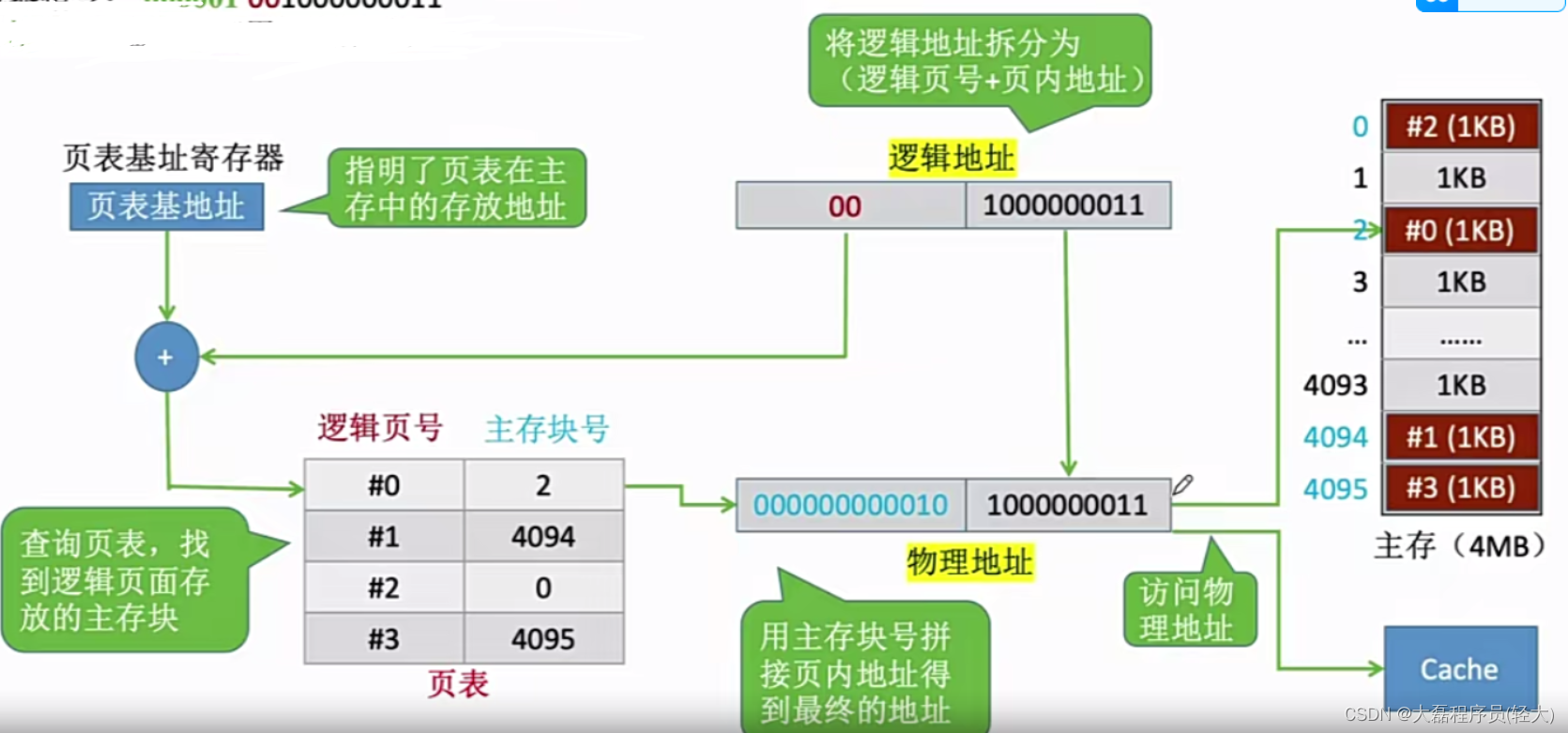

地址变换过程

第一步:先将逻辑地址拆分为逻辑页号和页内地址,页内地址

第二步:CPU中的页表基址寄存器会指明了页表在主存中的存放地址,比如该页表是从主存号1058开始存储的,如果每一行的页表项占4B,那么就意味着从1058号开始往后取4B数据就是第一个页表项,依次。

第三步:查询页表,根据页表基地址和逻辑页号找到逻辑页面存放的主存块号。

第四步:用主存块号凭借页内地址得到最终的物理地址

第五步:根据物理地址访存主存和Cache

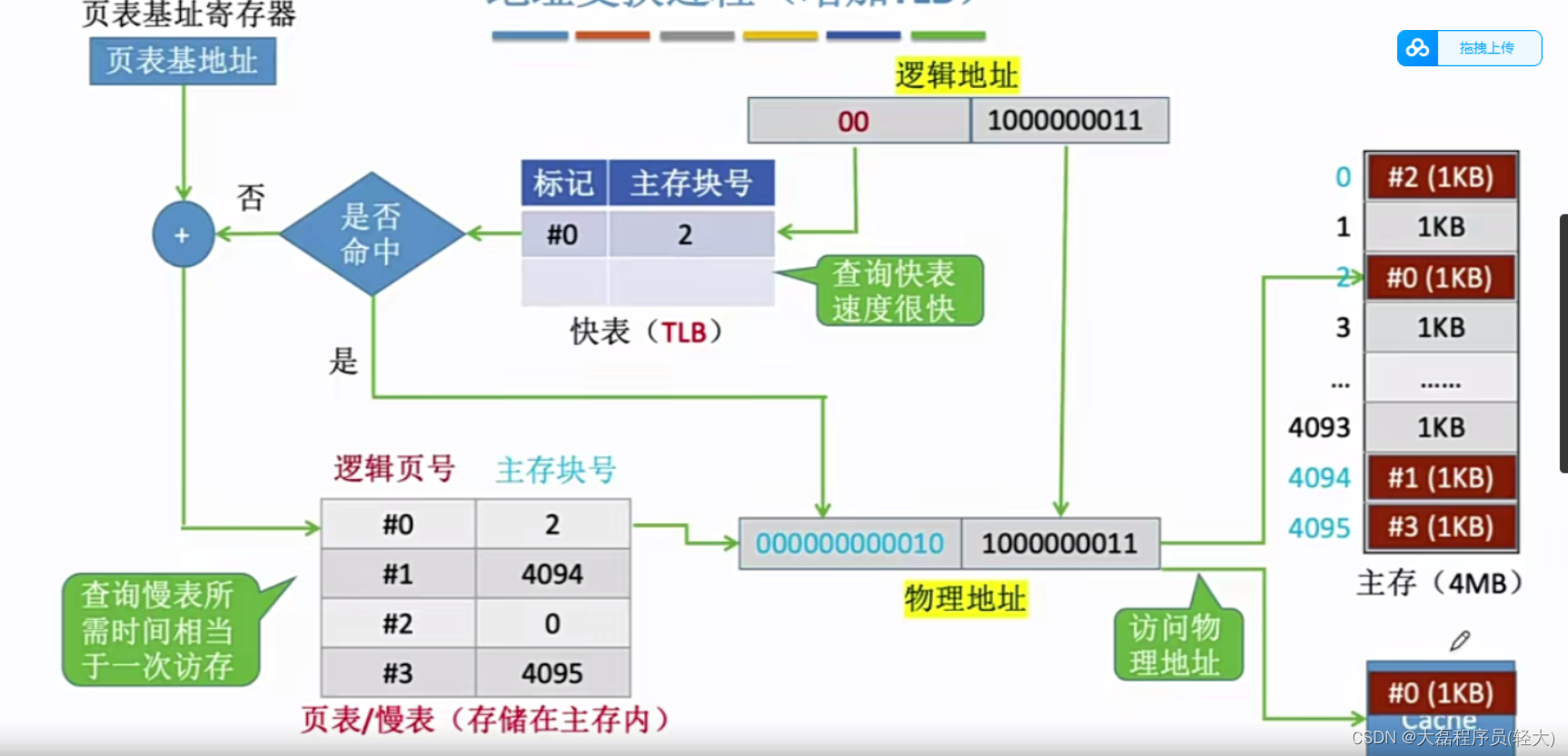

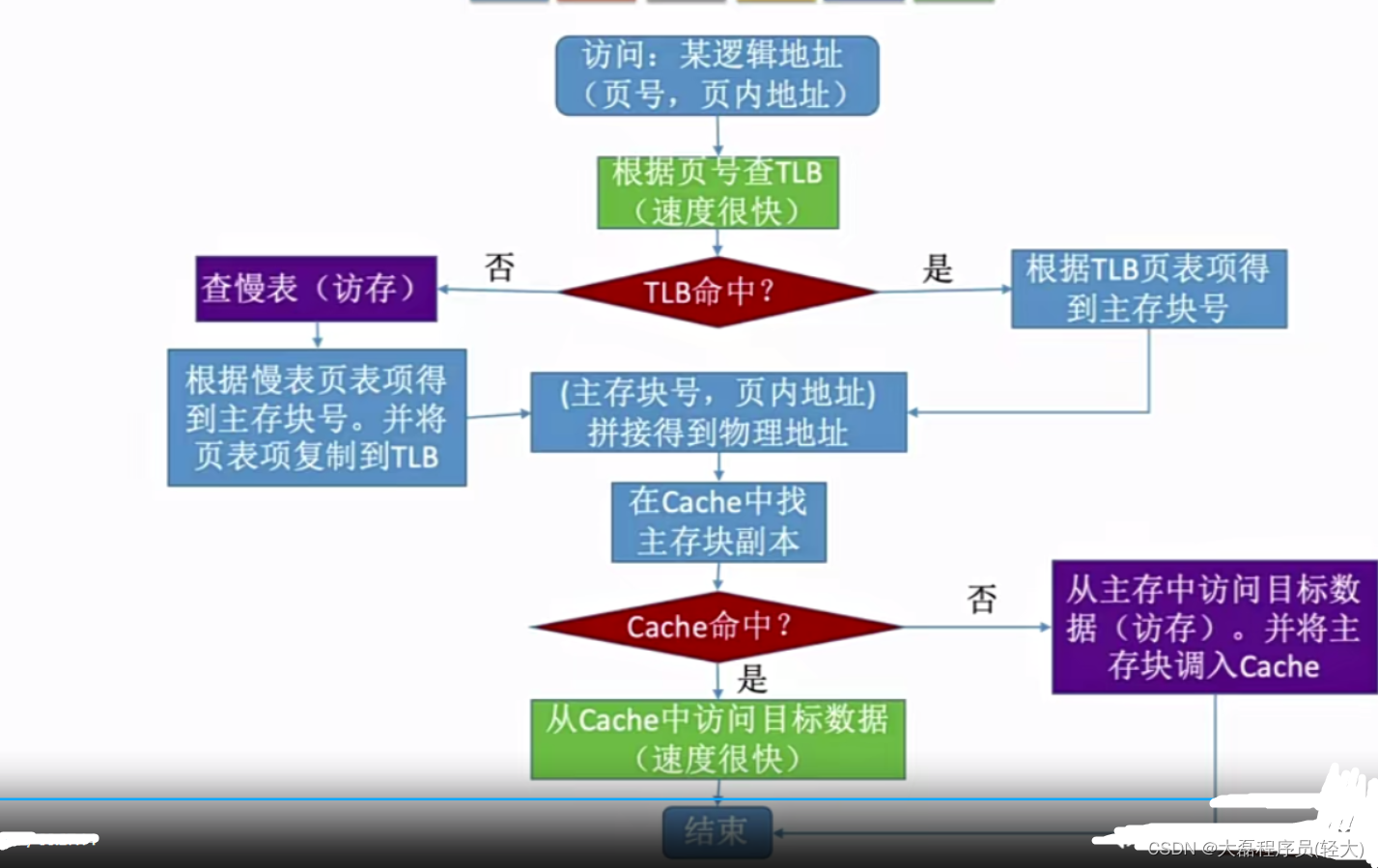

由于程序具有局部性,近期访问过的页表项可能会被再次访问,那么就可以将近期访问过的页表项放入更高速的存储器,可加快地址变换的速度,基于这个思想引入下面的地址变换过程(增加TLB)

地址变换过程(增加TLB)

快表(TLB):类似于Cache的一个硬件结构,查找速度非常快

注意区别:

- 作用不同:快表的作用是为了加快辅存向主存的地址映射速度,Cache作用是用于解决CPU与主存速度不匹配问题。

- 存储的内容不同:快表中存储的是页表项的副本,Cache中存储的是主存块中的副本

- 电路设计不同:快表是一种“相联存储器”,可以按内容寻访,Cache需要按物理地址寻访

逻辑地址=逻辑页号+页内地址(虚地址=虚页号+页内地址)

物理地址=主存块号+页内地址(实地址=实页号+页内地址)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?