目录

一、基本信息

硬件平台: RK3568

系统: Android 11

SDK版本:rk_android11.0_sdk_231020.tgz (官方提供)

参考资料:Rockchip_Developer_Guide_Android11_SDK_V1.1.6_CN.pdf

LCD屏:10.1寸 mipi接口 1200x1920 竖屏

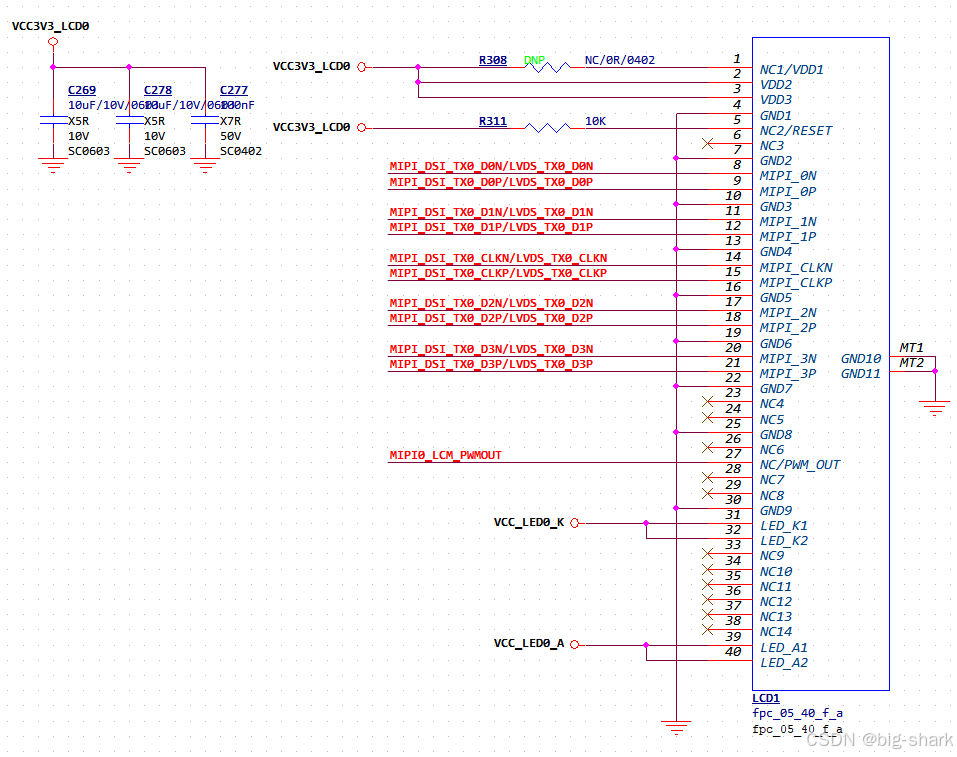

二、硬件电路

三、DTS配置

参考资料:RK3588_MIPI_DSI2_Developer_Guide_CN.pdf

dts 几个关键点: 基本都和LCD屏有关,需要厂家提供资料

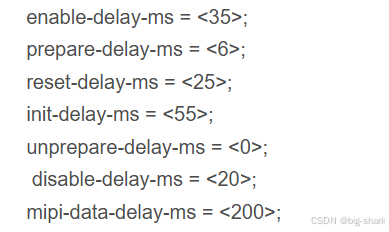

1、配置延时,如下图

2、 panel-init-sequence 初始化时序

厂家很可能提供多种配置格式,最终转换为rk要求的格式

如提供 :

Generic_Long_Write_3P(0xFF,98,81,03);

//GIP_1

Generic_Short_Write_1P(0x01,0x00);

Generic_Short_Write_1P(0x02,0x00);

Generic_Short_Write_1P(0x03,0x73);

Generic_Short_Write_1P(0x04,0x00);

Generic_Short_Write_1P(0x05,0x00);

Generic_Short_Write_1P(0x06,0x08);

Generic_Short_Write_1P(0x07,0x00);

Generic_Short_Write_1P(0x08,0x00);

Generic_Short_Write_1P(0x09,0x00);

需要进行转换,请看另一篇文章《RK3568-MIPI屏幕调试笔记: LCD上电初始化时序》。

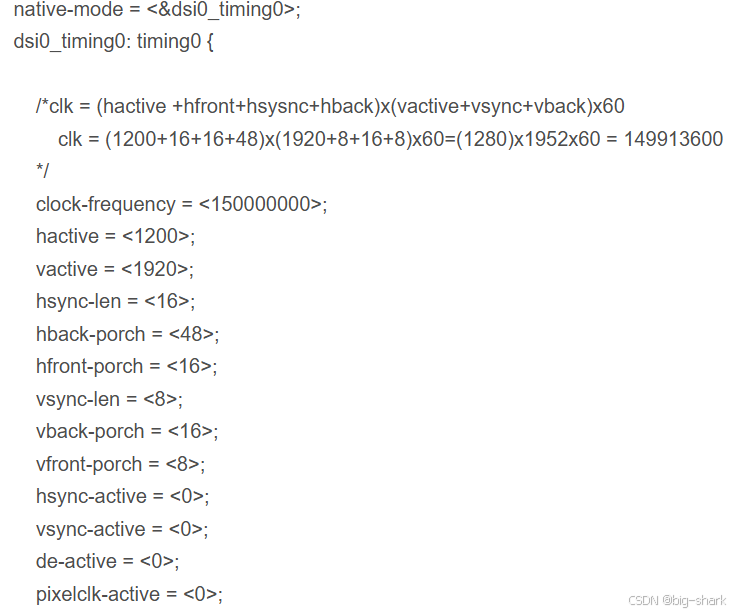

3、时序

其中clock-frequency 通过计算得到,方法如上图。

四、总结

mipi屏的调试,重点几个方面

1、硬件保证联通,mipi线,背光电路,电源控制电路,第一步保证硬件正常

2、dts配置,采用rk的默认配置,重点修改目录三的项目,关键点是初始化系列命令

该命令必须从厂家获取,如果是rk格式的直接使用,如果不是需要转换为rk格式的。

五,dts文件

完整的DTS如下

/ {

/* MIPI DSI0 Backlight*/

backlight: backlight {

status = "okay";

compatible = "pwm-backlight";

enable-gpios = <&gpio0 RK_PC3 GPIO_ACTIVE_HIGH>; //背光使能GPIO

pwms = <&pwm4 0 50000 1>;

brightness-levels = <

60 60 60 61 61 61 62 62

...

248 249 250 251 252 253 254 255

>;

default-brightness-level = <128>;

};

};

/* Config MIPI DSI0 Video Port ,Panel, TP */

&route_dsi0 {

status = "okay";

//logo,rotation = <270>; //support rotation 90,180,270

connect = <&vp1_out_dsi0>;

};

&video_phy0 {

status = "okay";

};

&dsi0_in_vp0 {

status = "disabled";

};

&dsi0_in_vp1 {

status = "okay";

};

/*

* mipi_dphy0 needs to be enabled

* when dsi0 is enabled

*/

&dsi0 {

status = "okay";

//rockchip,lane-rate = <1000>;

dsi0_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

enable-gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>; // 电源使能GPIO

reset-gpios = <&gpio3 RK_PB5 GPIO_ACTIVE_LOW>; //

enable-delay-ms = <35>;

prepare-delay-ms = <6>;

reset-delay-ms = <25>;

init-delay-ms = <55>;

unprepare-delay-ms = <0>;

disable-delay-ms = <20>;

mipi-data-delay-ms = <200>;

size,width = <120>;

size,height = <170>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST | MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = <MIPI_DSI_FMT_RGB888>;

dsi,lanes = <4>;

panel-init-sequence = [

29 00 04 FF 98 81 03

//GIP_1

13 00 02 01 00

13 00 02 02 00

13 00 02 03 73

13 00 02 04 00

13 00 02 05 00

13 00 02 06 08

13 00 02 07 00

13 00 02 08 00

13 00 02 09 00

13 00 02 0A 01

13 00 02 0B 01

13 00 02 0C 00

13 00 02 0D 01

13 00 02 0E 01

13 00 02 0F 00

13 00 02 10 00

13 00 02 11 00

13 00 02 12 00

13 00 02 13 02 //00

13 00 02 14 00

13 00 02 15 00

13 00 02 16 00

13 00 02 17 00

13 00 02 18 00

13 00 02 19 00

13 00 02 1A 00

13 00 02 1B 00

13 00 02 1C 00

13 00 02 1D 00

13 00 02 1E 40

13 00 02 1F C0

13 00 02 20 06

13 00 02 21 01

13 00 02 22 06

13 00 02 23 01

13 00 02 24 88

13 00 02 25 88

13 00 02 26 00

13 00 02 27 00

13 00 02 28 3B

13 00 02 29 03

13 00 02 2A 00

13 00 02 2B 00

13 00 02 2C 00

13 00 02 2D 00

13 00 02 2E 00

13 00 02 2F 00

13 00 02 30 00

13 00 02 31 00

13 00 02 32 00

13 00 02 33 00

13 00 02 34 00 // GPWR1/2 non overlap time 2.62us

13 00 02 35 00

13 00 02 36 00

13 00 02 37 00

13 00 02 38 00

13 00 02 39 00

13 00 02 3A 00

13 00 02 3B 00

13 00 02 3C 00

13 00 02 3D 00

13 00 02 3E 00

13 00 02 3F 00

13 00 02 40 00

13 00 02 41 00

13 00 02 42 00

13 00 02 43 00

13 00 02 44 00

//GIP_2

13 00 02 50 01

13 00 02 51 23

13 00 02 52 45

13 00 02 53 67

13 00 02 54 89

13 00 02 55 AB

13 00 02 56 01

13 00 02 57 23

13 00 02 58 45

13 00 02 59 67

13 00 02 5A 89

13 00 02 5B AB

13 00 02 5C CD

13 00 02 5D EF

//GIP_3

13 00 02 5E 00

13 00 02 5F 01

13 00 02 60 01

13 00 02 61 06

13 00 02 62 06

13 00 02 63 07

13 00 02 64 07

13 00 02 65 00

13 00 02 66 00

13 00 02 67 02

13 00 02 68 02

13 00 02 69 05

13 00 02 6A 05

13 00 02 6B 02

13 00 02 6C 0D

13 00 02 6D 0D

13 00 02 6E 0C

13 00 02 6F 0C

13 00 02 70 0F

13 00 02 71 0F

13 00 02 72 0E

13 00 02 73 0E

13 00 02 74 02

13 00 02 75 01

13 00 02 76 01

13 00 02 77 06

13 00 02 78 06

13 00 02 79 07

13 00 02 7A 07

13 00 02 7B 00

13 00 02 7C 00

13 00 02 7D 02

13 00 02 7E 02

13 00 02 7F 05

13 00 02 80 05

13 00 02 81 02

13 00 02 82 0D

13 00 02 83 0D

13 00 02 84 0C

13 00 02 85 0C

13 00 02 86 0F

13 00 02 87 0F

13 00 02 88 0E

13 00 02 89 0E

13 00 02 8A 02

//Page 4 command;

29 00 04 FF 98 81 04

13 00 02 3B C0 // ILI4003D sel

13 00 02 6C 15 //Set VCORE voltage =1.5V

13 00 02 6E 2A //di_pwr_reg=0 for power mode 2A //VGH clamp 18V

13 00 02 6F 33 //45 //pumping ratio VGH=5x VGL=-3x

13 00 02 8D 1B //VGL clamp -10V

13 00 02 87 BA //ESD

13 00 02 3A 24 //POWER SAVING

13 00 02 26 76

13 00 02 B2 D1

// Page 1 command

29 00 04 FF 98 81 01

13 00 02 22 0A //BGR, SS

13 00 02 31 00 //Zigzag type3 inversion

13 00 02 40 53 // ILI4003D sel

13 00 02 43 66

13 00 02 53 3f

13 00 02 50 87

13 00 02 51 82

13 00 02 60 15

13 00 02 61 01

13 00 02 62 0C

13 00 02 63 00

// Gamma P

13 00 02 A0 00

13 00 02 A1 13 //VP251

13 00 02 A2 23 //VP247

13 00 02 A3 14 //VP243

13 00 02 A4 16 //VP239

13 00 02 A5 29 //VP231

13 00 02 A6 1E //VP219

13 00 02 A7 1D //VP203

13 00 02 A8 86 //VP175

13 00 02 A9 1E //VP144

13 00 02 AA 29 //VP111

13 00 02 AB 74 //VP80

13 00 02 AC 19 //VP52

13 00 02 AD 17 //VP36

13 00 02 AE 4B //VP24

13 00 02 AF 20 //VP16

13 00 02 B0 26 //VP12

13 00 02 B1 4C //VP8

13 00 02 B2 5D //VP4

13 00 02 B3 3F //VP0

// Gamma N

13 00 02 C0 00 //VN255 GAMMA N

13 00 02 C1 13 //VN251

13 00 02 C2 23 //VN247

13 00 02 C3 14 //VN243

13 00 02 C4 16 //VN239

13 00 02 C5 29 //VN231

13 00 02 C6 1E //VN219

13 00 02 C7 1D //VN203

13 00 02 C8 86 //VN175

13 00 02 C9 1E //VN144

13 00 02 CA 29 //VN111

13 00 02 CB 74 //VN80

13 00 02 CC 19 //VN52

13 00 02 CD 17 //VN36

13 00 02 CE 4B //VN24

13 00 02 CF 20 //VN16

13 00 02 D0 26 //VN12

13 00 02 D1 4C //VN8

13 00 02 D2 5D //VN4

13 00 02 D3 3F //VN0

// Page 0 command

29 00 04 FF 98 81 00

05 C8 01 11

05 32 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings0: display-timings {

native-mode = <&dsi0_timing0>;

dsi0_timing0: timing0 {

/*clk = (hactive +hfront+hsysnc+hback)x(vactive+vsync+vback)x60

clk = (1200+16+16+48)x(1920+8+16+8)x60=(1280)x1952x60 = 149913600

*/

clock-frequency = <150000000>;

hactive = <1200>;

vactive = <1920>;

hsync-len = <16>;

hback-porch = <48>;

hfront-porch = <16>;

vsync-len = <8>;

vback-porch = <16>;

vfront-porch = <8>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

4079

4079

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?