最近在工作之余终于腾出一些时间系统的学习dsp,下面以一个初学者的身份记录我的学习内容。希望各位能够指出文中的错误或不准确的地方。

目前主流的DSP处理器厂商主要有TI的C6000系列以及飞腾的FT2000系列,本文将只介绍TI公司的C6678,日后若如用到国产dsp以及芯片会后续更新。

TI的dsp处理器主要分为两大类:

1、定点dsp处理器;

2、浮点dsp处理器。

虽然是听上去定点处理器不能计算浮点数,但事实上二者是都可以的,只不过定点dsp处理器的硬件无法进行浮点运算,需要通过软件层面将浮点数转化为定点数才可以,而多出来这一步将导致定点处理器的运算效率会大大下降。浮点处理器由于在硬件上支持浮点指令,硬件上支持浮点运算。c6678属于c66x架构,可以兼容这两者的运算,同时提升了性能,它被称为定点和浮点处理器。

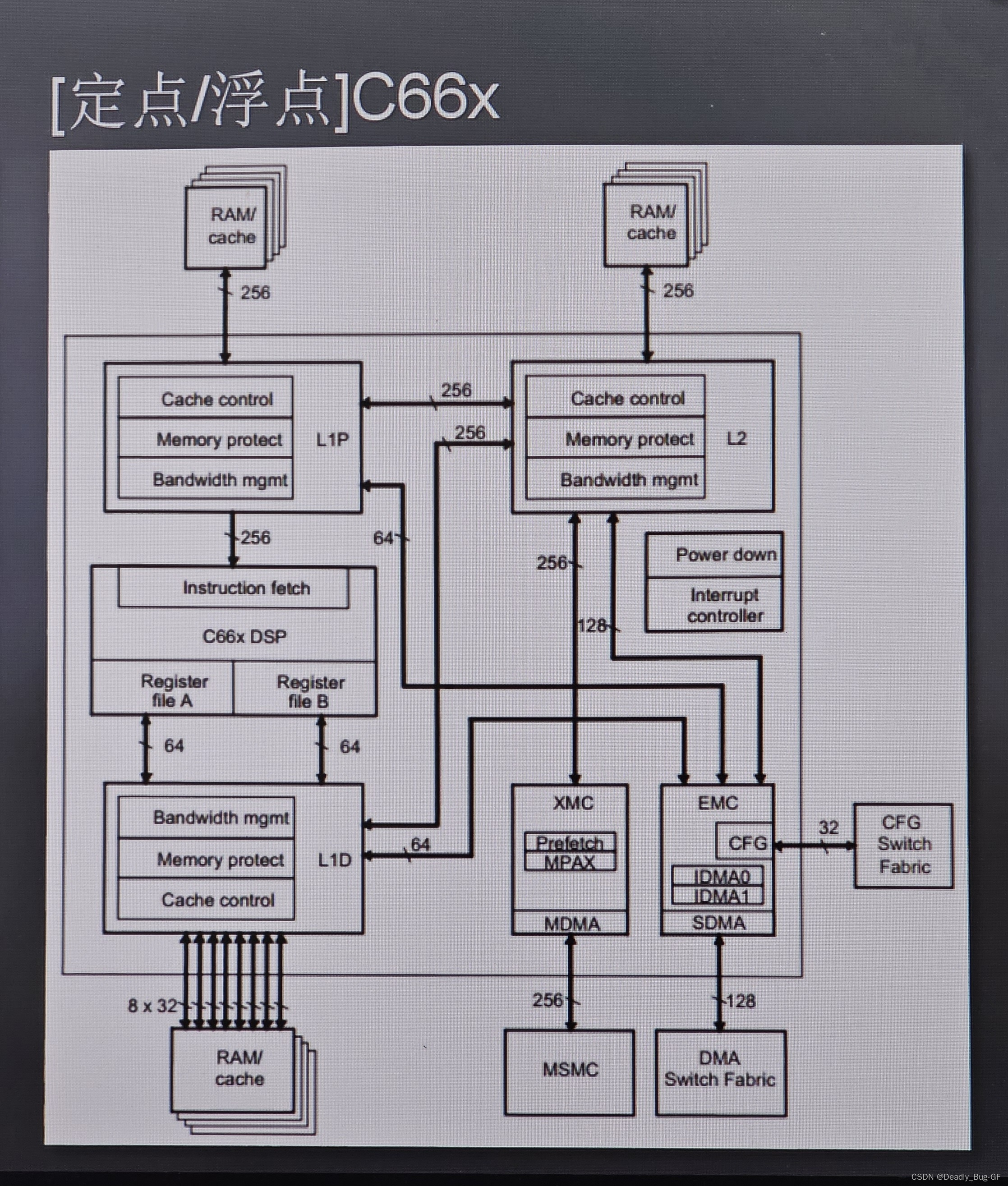

C6678处理器具有8个TMS320C66x内核,每个内核内部都有L1P、L1D和L2 SRAM存储器,多核共享的存储器为MSM和SRAM。

XMC:扩展内存控制器 通过256位总线宽度和L2 RAM直接相连

EMC:外部内存控制器 通过256位总线宽度和MSMC(keystone架构的核心)

可以通过EMC访问L1P L1D L2可以配置想要访问的外设 通过SDMA访问内部子系统的L1 L2

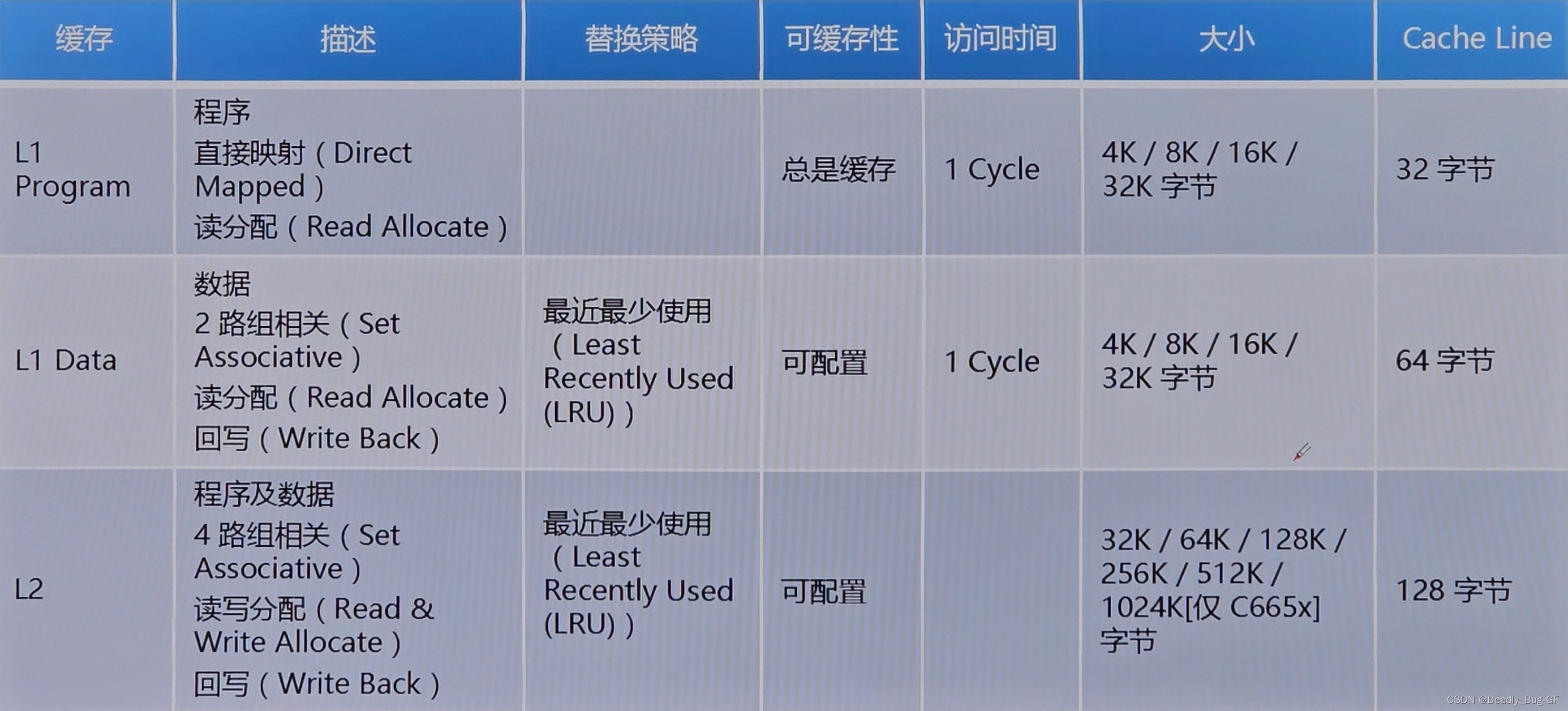

缓存有两级架构L1和L2。

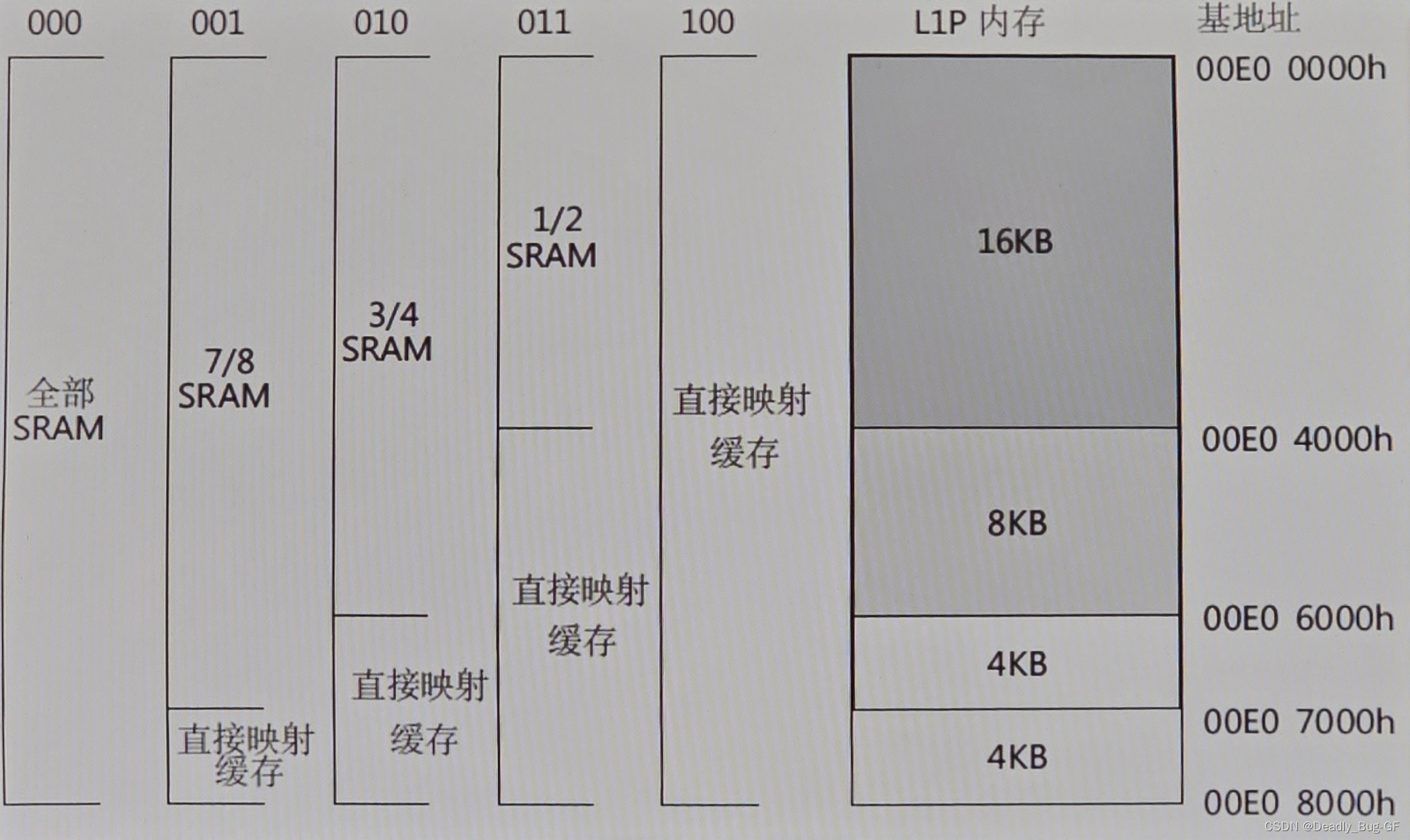

其中L1P(L1Program)只能放程序不能放数据,直接映射(Direct Mapped)读写分配(Read Allocate)可以配置为内存、缓存、内存和缓存的混合模式。大小:4K/8K/16K/32KB 没有用满剩下的将被当作RAM使用,Cache line(缓存一次性操作的数据宽度) 是32B。

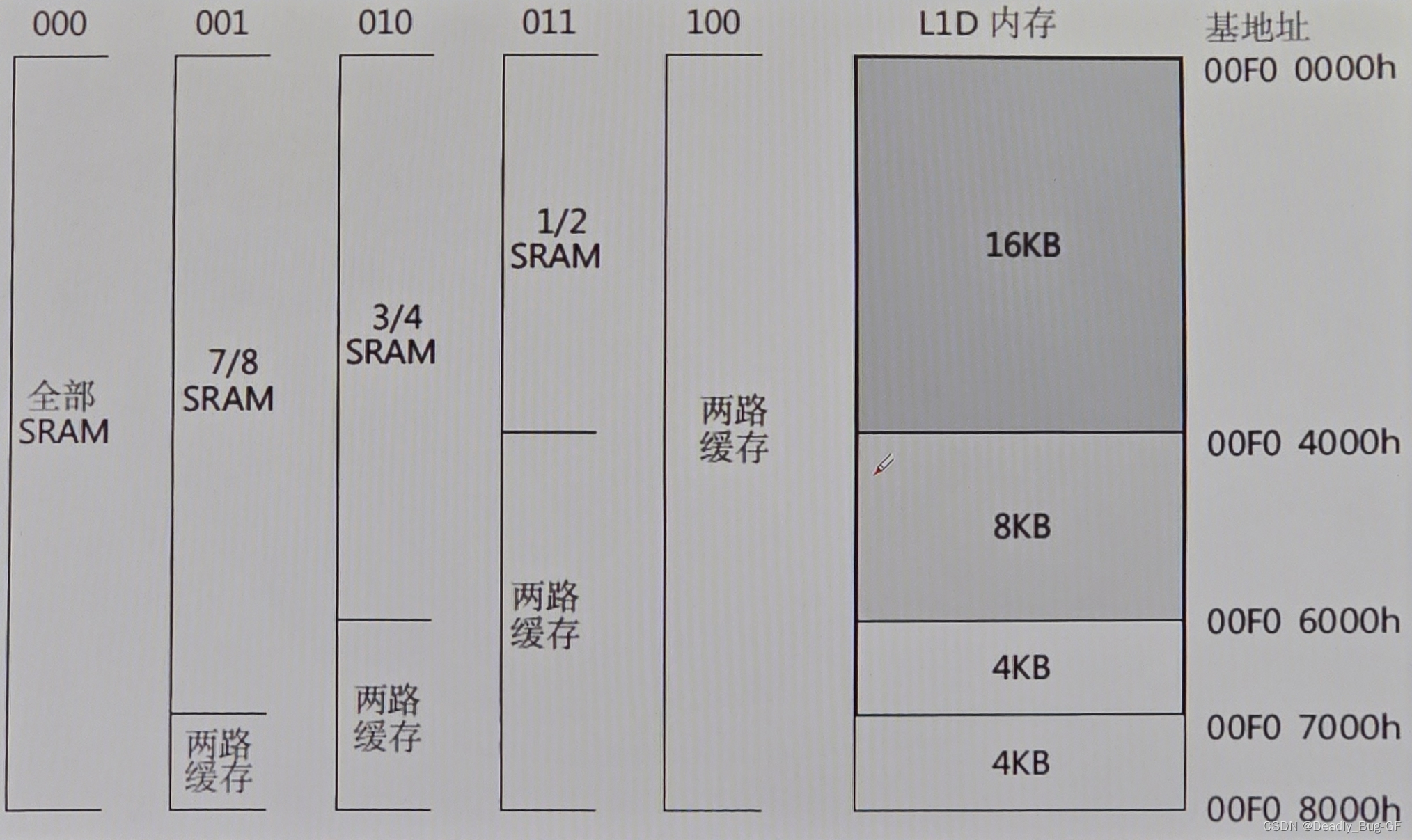

L1D(L1 Data)只能放数据不能放程序,2路组相关(类似于备份),大小与LIP相同,替换策略是最近最少使用,当一路数据被替换,当需要使用时另一路还可以使用,Cache line是64B。

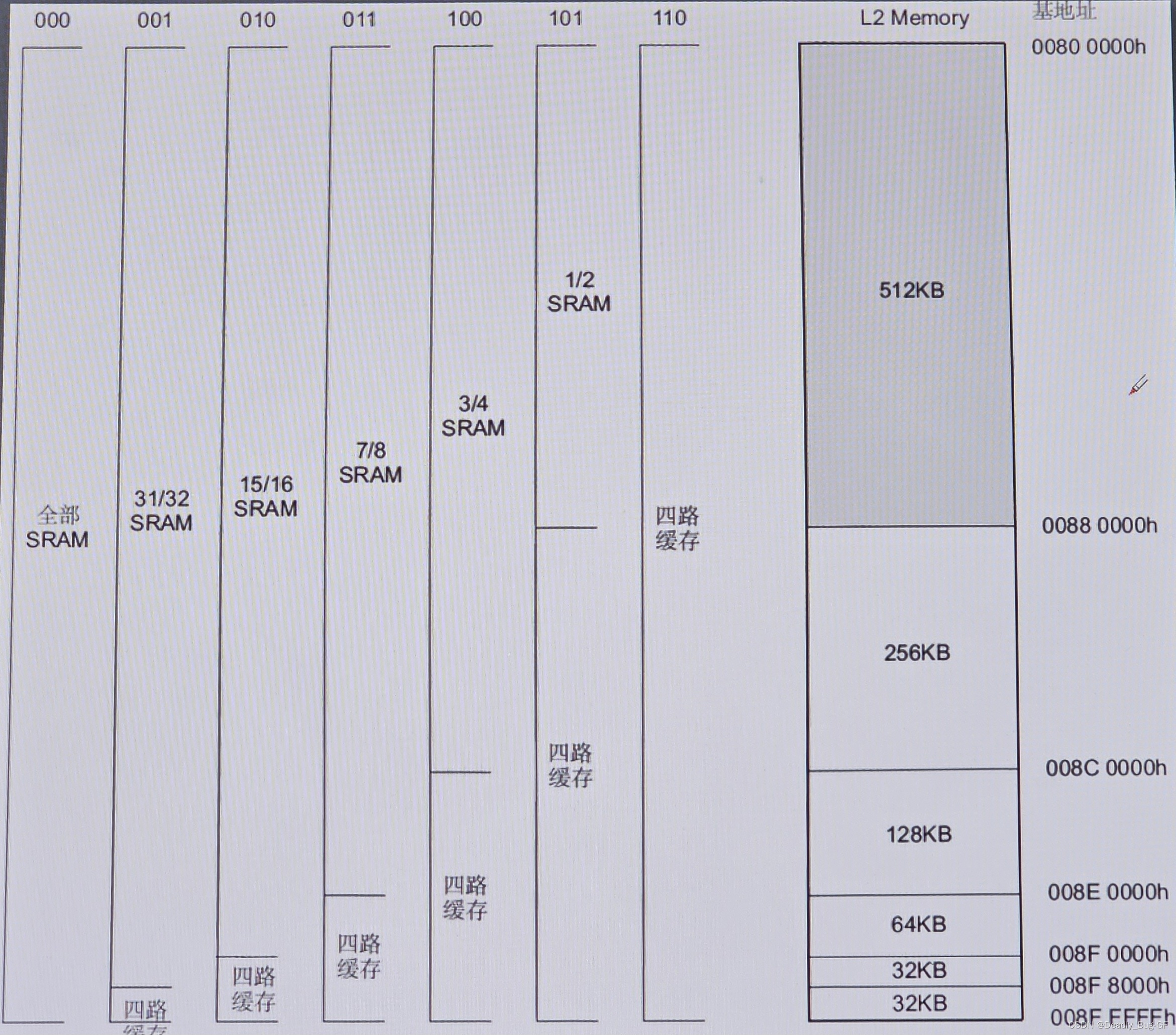

L2 (二级缓存) 可以放数据和程序,4路组相关,读写分配,替换策略与L1D相同,大小为32K/64K/128K/256K/512K,没有都用完剩下的配为SRAM,Cache line是128B。

以上缓存和RAM所有的低地址是SRAM高地址是缓存使用。

内存映射情况:

对于DSP的CPU来说片上的L1、L2一般会被映射到两个地址:1、DSP Local(DSP本地内存映射);2、SoC Global(SoC全局内存映射)

数据若仅需要被CPU访问就放到本地空间,若需要被其他CPU或SoC其他外设访问要放到全局空间。

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?