结论:

对信号(signal)取相反数,如果信号位宽小于32位,直接使用~signal+1进行操作,是不对的。

如果位宽大于等于32位宽,直接使用~signal+1进行操作,是没有问题的。

如:

//伪代码

wire [23:0]signal;

wire a;

wire [23:0]b = 4000;

assign a = (~signal + 1 > b) ? 1 : 0

此时a将会一直为1。

因为信号位宽小于32,~signal + 1将会用1补足32位。

解决办法,加一个24位宽的寄存器存储。

//伪代码

wire [23:0]signal;

wire a;

wire [23:0]b = 4000;

wire [23:0]signal_fan;

assign signal_fan = ~signal + 1;

assign a = (signal_fan> b) ? 1 : 0

always @(*) begin

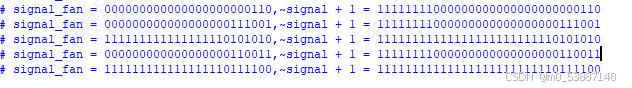

$display("signal_fan = %b,~signal + 1 = %b",signal_fan,~signal + 1);

end

编写相应的tb文件,打印出来的结果如下图所示:

将位宽变为33,结果如

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1816

1816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?