AXI4接口

(刚开始学习的时候做的笔记,有很多不足,有问题的,望批评指正)

导读:

AXI4总线定义(中文名+优势)

片内总线定义

什么时候使用?

分类

AXI4,AXI4_Lite,五个通道

AXI4_stream

- AXI4总线是什么?

AXI4是(Advanced eXtensible Interface,高级可拓展接口,ARM公司开发的)。

eXtensible [ɪk'stensəbəl] 可扩展;可扩展性;可扩展的

支持多主多从。因为地址,数据,响应等通道分开,这也是AXI4高效的原因

- 片内总线体现在哪里?和我们之前学的总线有什么不同?

三大低速总线讲的都是串行的,串口,SPI,IIC

高速接口:千兆以太网,DDR(大概算),更高速的PCIE,SRIO

上述芯片和芯片之间通信的机制。

AXI是片内总线(芯片内部通信接口)

理解:PS和PL端通信,(数据送到PL端处理,PL端处理不了的,送给到PS端处理,处理好了发送给PL端)。

芯片内部通信其实就是:模块间的通信,两个模块间进行数据传输的一种协议。(我感觉也没有什么物理层方面的东西,引脚,接口这种实物),就是用代码实现的两个模块之间的通信,物理层依靠的是FPGA板卡的底部资源来实现。

- 什么时候去使用?

zyqn在开发的时候使用,ps和pl端通信;纯FPGA使用的时候,会有一些IP核有AXI接口。

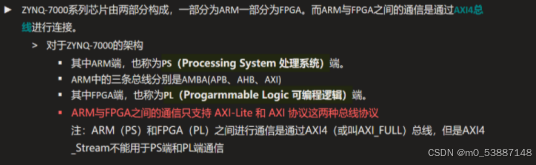

Zyqn系列 ARM(PS)和FPGA(PL)之间进行通信是通过AXI4(或叫作AXI_FULL)总线,也可以用AXI4_Lite,但是AXI4_Stream不能用于PS端和PL端通信。

ARM中的三条总线分别是AMBA(APB、AHB、AXI)

AXI4应用如下:(还有一些其他IP核具有AXI4接口的使用,如FIFO)

|

名称 |

IP核名称 |

|

SR I/O高速接口(协议) |

rapid I/O |

|

PCIE高速接口 |

XDMA |

|

JESD204B高速接口 |

JESD204 |

|

DDR3/4 |

mig |

|

千兆以太网 |

mac |

- AXI4分类

AXI4分为三种:AXI4、AXI4_Lite、AXI4_Stream。

(AXI4和AXI4_lite是兼容的(在调IP核时,只显示AXI4意味着两者都包含),三种都支持突发传输)

AXI4是突发传输,何为突发?

就是读写换了个名字,突发指单次进行连续读写的长度。

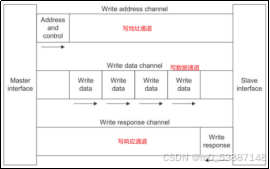

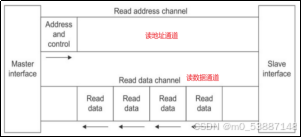

- AXI4和AXI4_lite的五个通道

写地址,写数据,写响应,读地址,读数据,这五个通道里都有一对握手信号,握手信号一般都是指valid和ready信号,还有一个对应的信息。

(怎么记?记下边这张图)

握手信号理解:有主从之分,ready从机告诉主机我准备好了,valid主机告诉从机我发送的这个数据有效。

两者同时为高,数据才有效。比如,ready和valid同时为高,写地址有效。Ready和valid同时为高,写数据有效........,写地址,写数据,返回来的写响应,读地址,读数据都需要握手,是比较稍微复杂的信号。

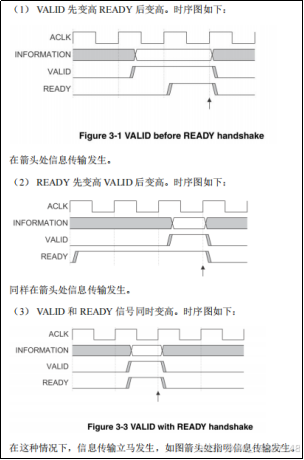

- Vaild和ready同时拉高有三种情况

同时拉高/vaild先拉高/ready先拉高

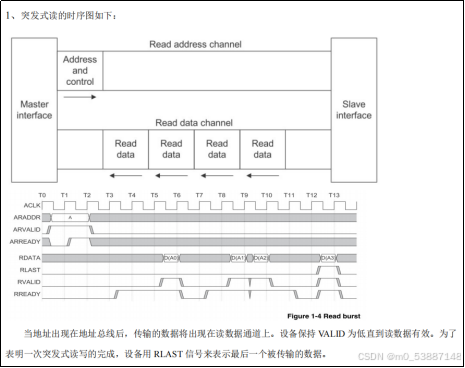

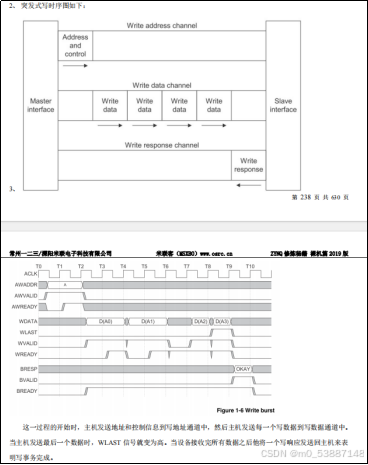

- AXI4的读写时序

突发读

突发写

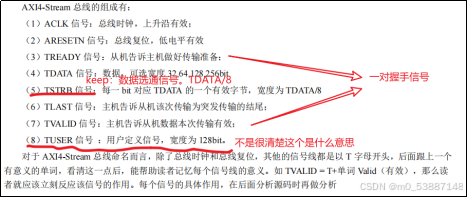

- AXI4_STREAM

包含哪些信号?

因为没有地址,该握手信号对应传输的是数据(TDATA)。

Keep一个比特对应一个DATA的字节。

User信号一般用不到

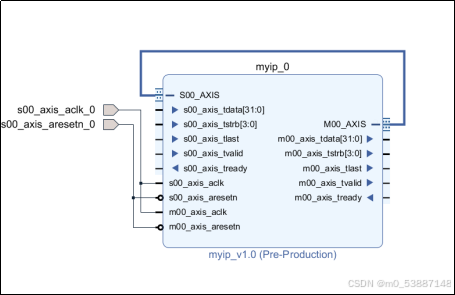

对AXI4_STREAM理解:在一个模块中调用AXI_STREAM的时候信号接口如下所示(数据回环的例子):

注意发送时:只有M(master主机)->S(slave从机)。

两个模块间通信,每个模块都有M端和S端,所以A模块的M发送数据给B模块的S。

B模块想给A模块发数据时,是B模块的M发数据给A模块的S。

每个端口都有上述的几个信号。

- 补充

- 总线,接口,协议

- AXI4又名AXI4_full,

- AXI4_lite(lite可以理解为轻量级的),

- AXI4_stream(stream流,是数据流的传输)

AXI4_full最多一次突发传输256个数据。为什么是256个数据而不是字节。

理解:因为AXI4数据发送是固定的。(比如数据发送是32根线,经过这32根线发出的是一个数据,256个数据可能指32根线并行发送,每根线发送256位。)

AXI4_lite突发长度为1,在传输的时候一次只发一个数据。

AXI4_stream突发长度为无限个,因为以流的方式传输。AXI4_Stream没有地址线。

7743

7743

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?