题目:

用Verilog实现以下电路:

1. 带复位端的正边沿触发的D触发器;

2.带复位端的正边沿触发的JK触发器。

一. D触发器的Verilog代码实现

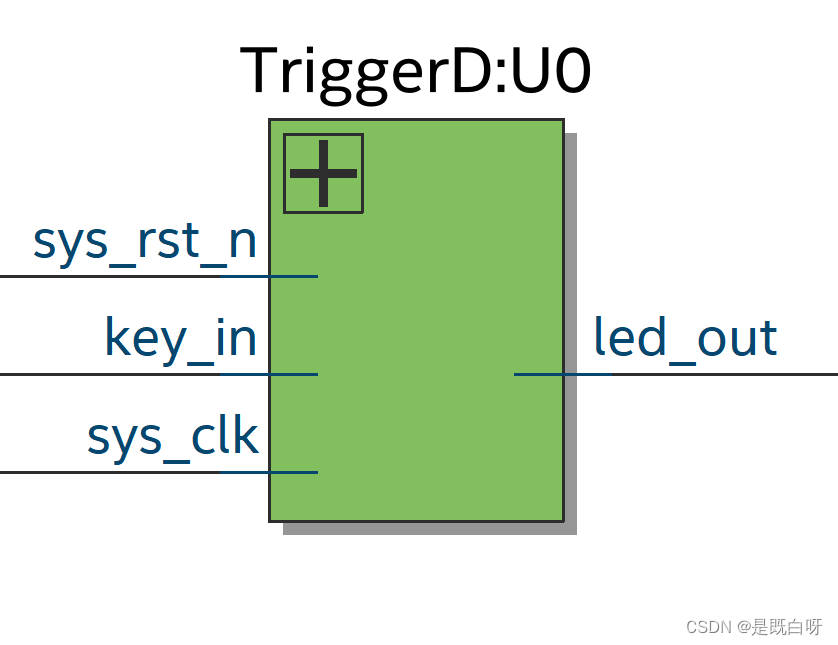

1. 模块框图

包括sys_clk,复位信号sys_rst_n,输入信号key_in以及输出信号led_out;

2. Verilog代码实现

采用行为级描述:

module TriggerD

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire key_in ,

output reg led_out

);

always@( posedge sys_clk or negedge sys_rst_n )

if( sys_rst_n == 1'b0 )

led_out <= 1'b1 ;

else

led_out <= key_in ;

endmoduletestbench仿真代码编写:

`timescale 1ns/1ns

module tb_TriggerD();

reg sys_clk ;

reg sys_rst_n ;

reg key_in ;

wire led_out ;

initial

begin

sys_clk <= 1'b0 ;

sys_rst_n <= 1'b0 ;

key_in <= 1'b1 ;

#30

sys_rst_n <= 1'b1 ;

end

always #10 sys_clk <= ~ sys_clk ;

always #100 key_in <= ~ key_in ;

TriggerD U0

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.key_in (key_in ),

.led_out (led_out )

);

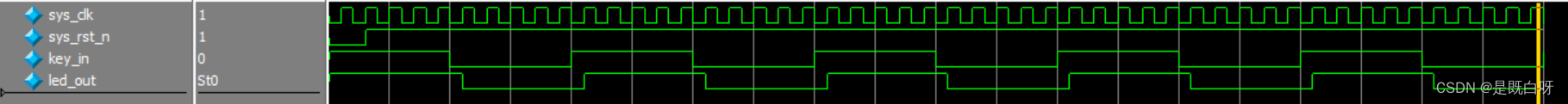

endmodule3. Modelsim仿真结果显示

可以看到,sys_clk信号正边沿到来时,led_out 跟随 key_in的值。

二. JK触发器的Verilog代码实现

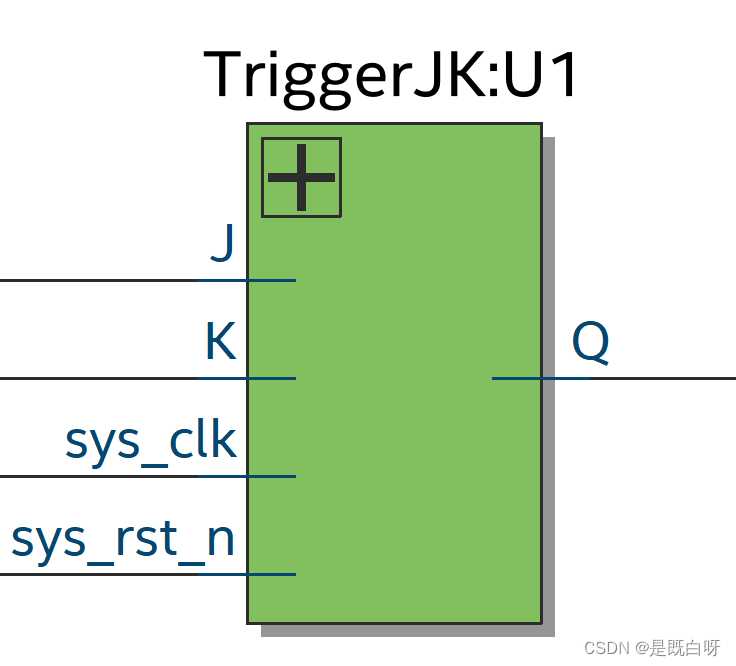

1. 模块框图

包括时钟信号sys_clk, 复位信号sys_rst_n,输入信号J,K,输出信号Q;

2. Verilog代码实现

采用case语句行为级描述:

module TriggerJK

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire J ,

input wire K ,

output reg Q

);

always@( posedge sys_clk or negedge sys_rst_n )

if( sys_rst_n == 1'b0 )

Q <= 1'b0 ;

else

begin

case( {J,K} )

2'b00: Q <= Q ;

2'b01: Q <= 1'b0 ;

2'b10: Q <= 1'b1 ;

2'b11: Q <= ~ Q ;

default: Q <= 1'b0 ;

endcase

end

endmoduletestbench仿真代码的编写:

`timescale 1ns/1ns

module tb_TriggerJK();

reg sys_clk ;

reg sys_rst_n ;

reg J ;

reg K ;

wire Q ;

initial

begin

sys_clk <= 1'b0 ;

sys_rst_n <= 1'b0 ;

J <= 1'b0 ;

K <= 1'b0 ;

#30

sys_rst_n <= 1'b1 ;

end

always #10 sys_clk <= ~ sys_clk ;

always #10 J <= {$random} % 2;

always #10 K <= {$random} % 2;

TriggerJK U1

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.J (J ),

.K (K ),

.Q (Q )

);

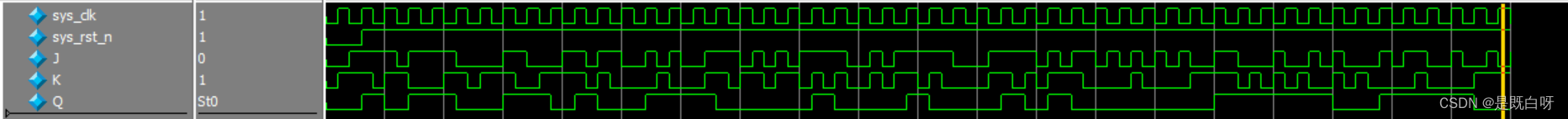

endmodule3. Modelsim仿真结果显示

上图表明:JK触发器逻辑功能为:JK 00不变,11翻转,01 10同J。

5544

5544

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?