前言

笔者在之前通过microblaze软核的方式实现了DDR3芯片的读写测试,当时对于Xilinx MIG DDR控制器的理解还比较肤浅。还是想通过控制用户接口时序的方式来读写DDR,扩展和加深自己对DDR的理解。

MIG IP核配置请看我的前一篇文章

【FPGA测试】Microblaze测试DDR读写_microblaze ddr-优快云博客

里面关于MIG参考时钟输入有错误的地方,这里改正一下。

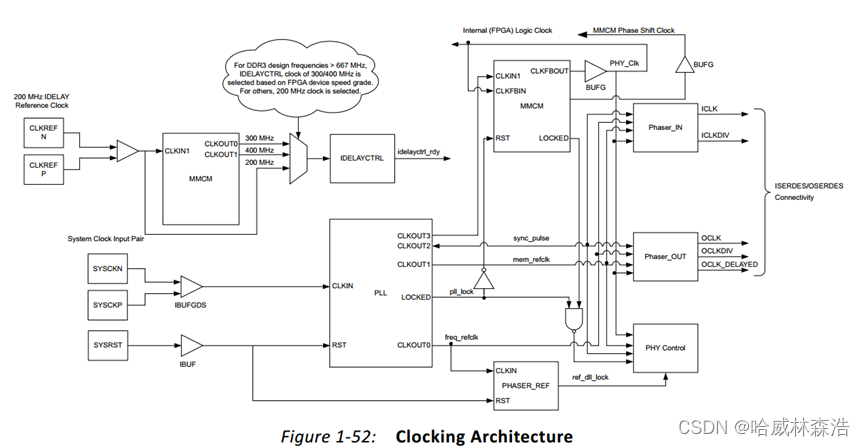

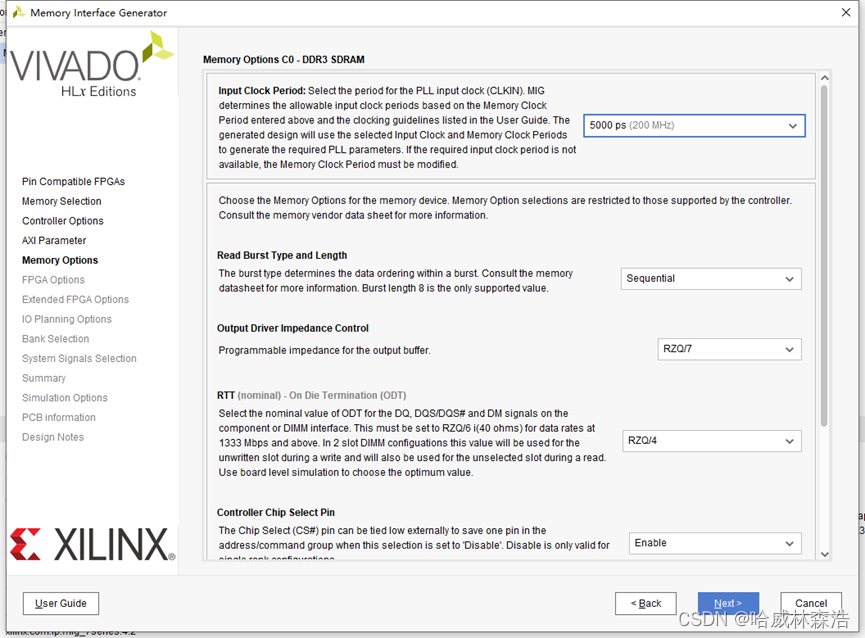

MIG的输入时钟有2种,一个是系统时钟,如下图所示,input Clock period。还有一个时钟为参考时钟,固定为200MHz。

DDR读写时序

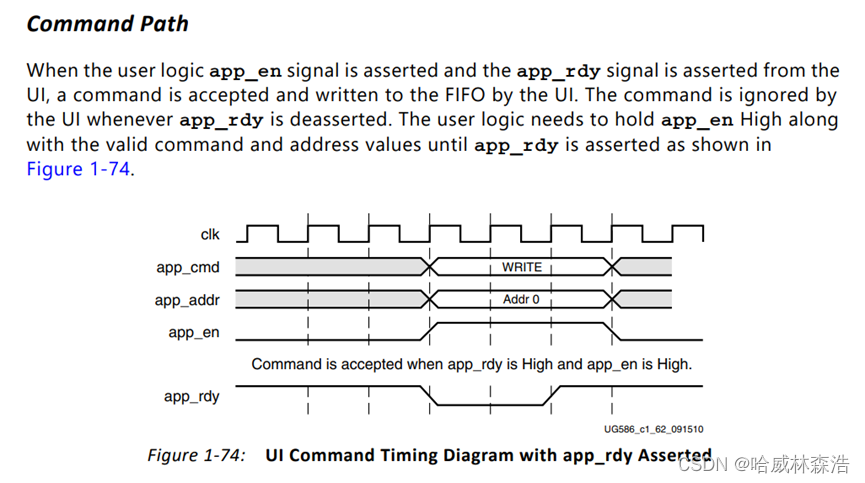

首先是命令,如图,只有当app_rdy信号为高时,用户给MIG的指令才有效。

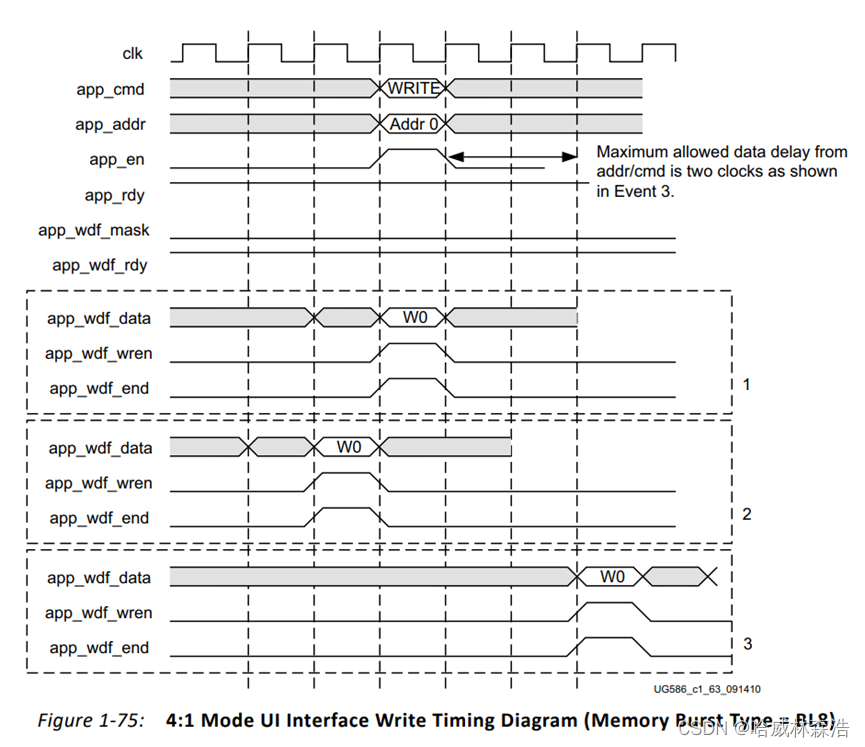

然后是写指令,一种是写数据和写命令同时进行。第二种是写的数据慢于写命令。第三种是写的数据快于写指令。一般来说采用同时写数据和写命令即可。

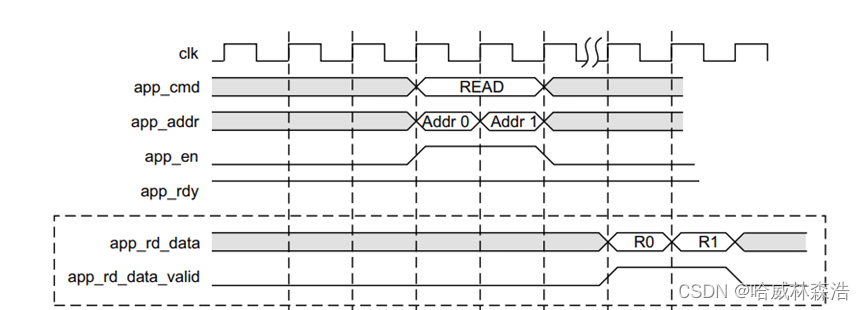

当输入读命令和读地址时,延迟几个时钟周期后,开始读出数据。当app_rd_data_vaild为高时,读出的数据才是正确且有效的。

测试代码如下:

每给一个地址,会往ddr里写8个32bit的数据。这样一次写命令就可以写满8个地址。

所以每写一次,地址都要加8。

同时。每读一次,会读出8个地址的数据,所以每次读一次,地址也要加8。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/23 14:03:36

// Design Name:

// Module Name: DDR3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module DDR3(

ddr3_addr,

ddr3_ba,

ddr3_cas_n,

ddr3_ck_n,

ddr3_ck_p,

ddr3_cke,

ddr3_cs_n,

ddr3_dm,

ddr3_dq,

ddr3_dqs_n,

ddr3_dqs_p,

ddr3_odt,

ddr3_ras_n,

ddr3_reset_n,

本文详细描述了如何通过Microblaze控制XilinxMIGDDR3控制器进行读写操作,包括MIG的输入时钟配置、命令发送、数据传输时序以及使用状态机实现的地址和数据处理。作者纠正了先前文章中的错误,并提供了测试代码示例。

本文详细描述了如何通过Microblaze控制XilinxMIGDDR3控制器进行读写操作,包括MIG的输入时钟配置、命令发送、数据传输时序以及使用状态机实现的地址和数据处理。作者纠正了先前文章中的错误,并提供了测试代码示例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3098

3098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?