1.原理

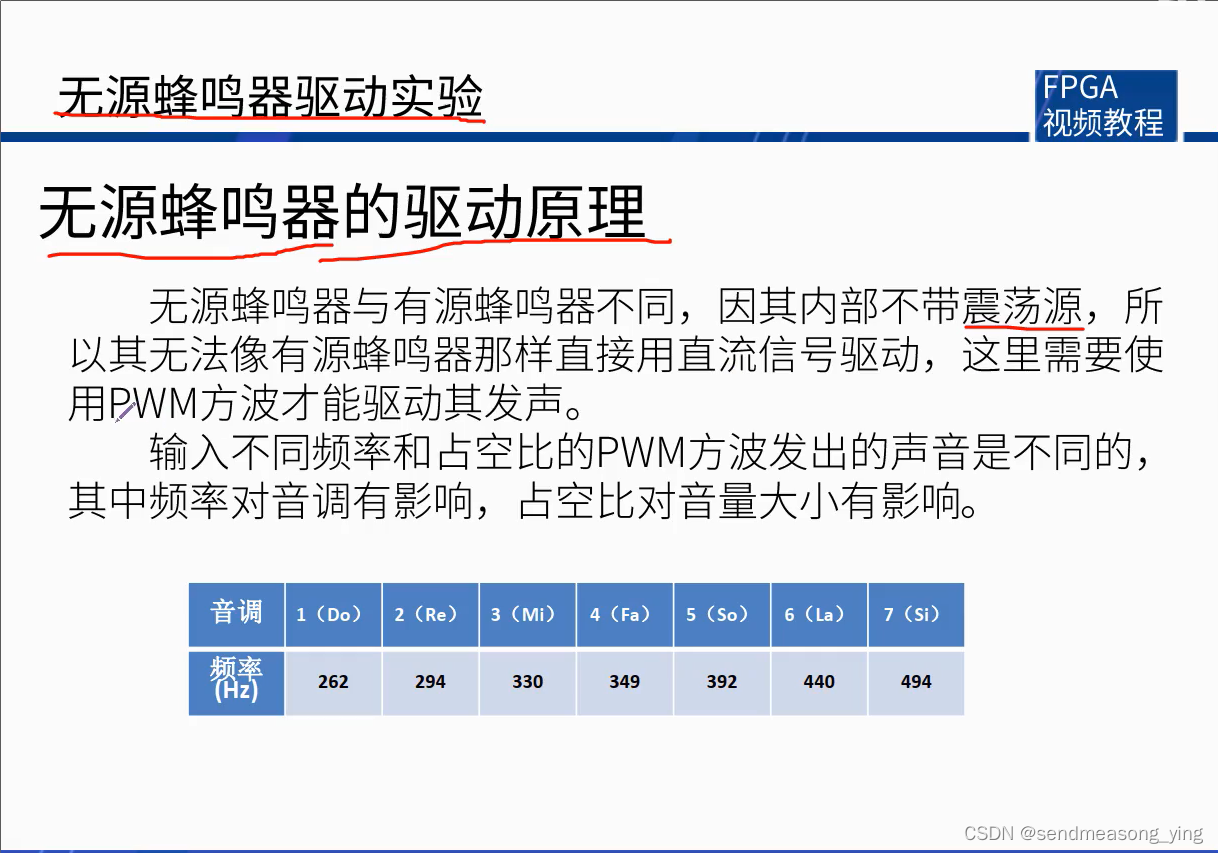

计划是,生成不同的7个频率控制蜂鸣器发声,每个音调发声0.5秒。

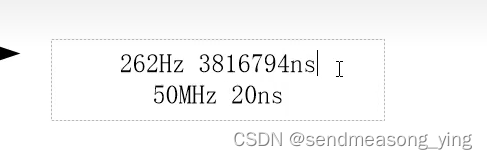

50MHZ计数0.5秒,50MHZ一个周期20ns,要计数0.5秒 ,0.5/0.000_000_02s=25000_000个时钟周期。因为是从0开始计数,所以计数的最大值是0-2499_999。

用一个计数器计数发音的7个0.5秒,当成是一个循环。

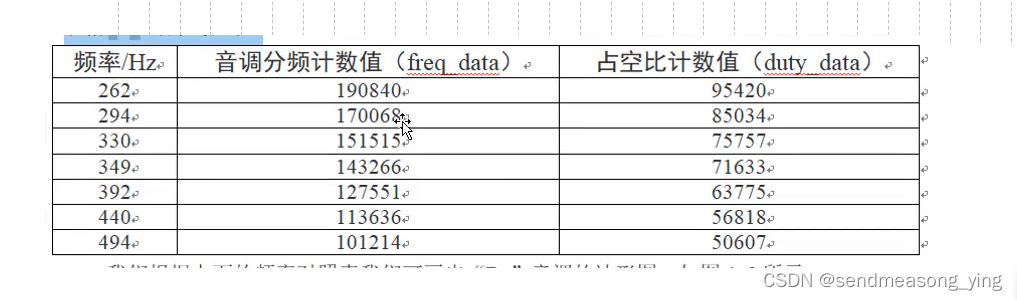

1/262hz=0.0038167938931298s,约等于3816794 ns。因此3816794/20=190,839.7。约等于190840。也就是说要计数0-190839个时钟周期才是262hz。占空比是50%(占空比:

是一个脉冲周期内,高电平的时间与整个周期时间的比例)。

该文章详细描述了一个使用Verilog语言设计的电路,通过计数器控制不同频率的蜂鸣器发声,每种频率持续0.5秒。电路涉及时序逻辑和组合逻辑,用于生成7个特定频率的音频信号,如262Hz等。

该文章详细描述了一个使用Verilog语言设计的电路,通过计数器控制不同频率的蜂鸣器发声,每种频率持续0.5秒。电路涉及时序逻辑和组合逻辑,用于生成7个特定频率的音频信号,如262Hz等。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7080

7080

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?