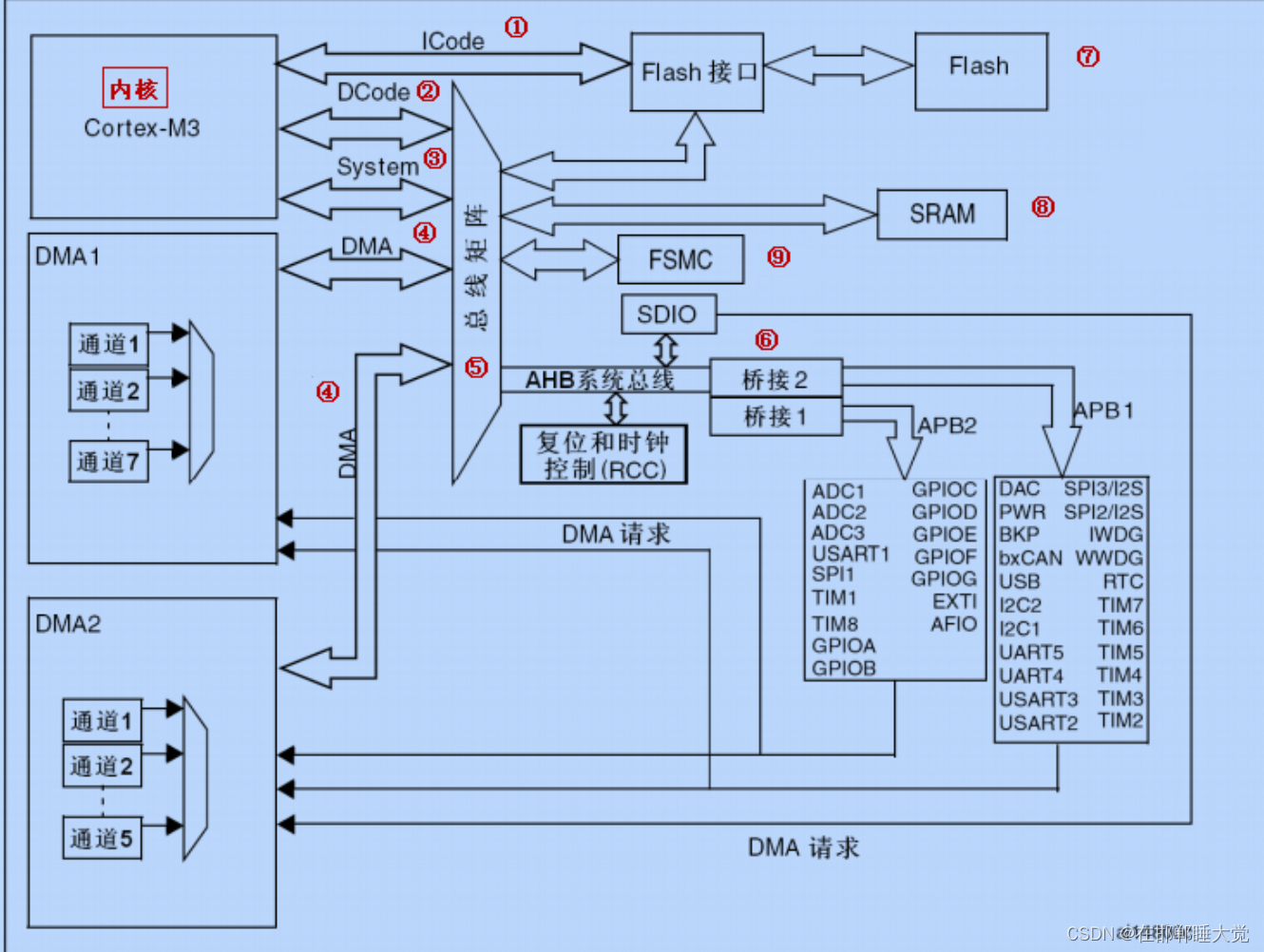

一、STM32F103系列系统架构

主系统主要由四个驱动单元和四个被动单元构成。

四个驱动单元是: 内核 DCode 总线;系统总线;通用 DMA1;通用 DMA2;

四被动单元是:AHB 到 APB 的桥:连接所有的 APB 设备; 内部 FlASH 闪存;内部 SRAM;FSMC;

下面我们具体讲解一下图中几个总线的知识:

1 ICode总线:该总线将M3内核指令总线和闪存指令接口相连,指令的预取在该总线上

面完成。

2 DCode总线:该总线将M3内核的DCode总线与闪存存储器的数据接口相连接,常量

加载和调试访问在该总线上面完成。

3 系统总线:该总线连接 M3 内核的系统总线到总线矩阵,总线矩阵协调内核和 DMA 间

访问。

4 DMA总线:该总线将DMA的AHB主控接口与总线矩阵相连,总线矩阵协调CPU的

DCode 和 DMA 到 SRAM,闪存和外设的访问。

5 总线矩阵:总线矩阵协调内核系统总线和 DMA 主控总线之间的访问仲裁,仲裁利用

轮换算法。

6 AHB/APB桥:这两个桥在AHB和2个APB总线间提供同步连接,APB1操作速度限于

36MHz,APB2 操作速度全速。

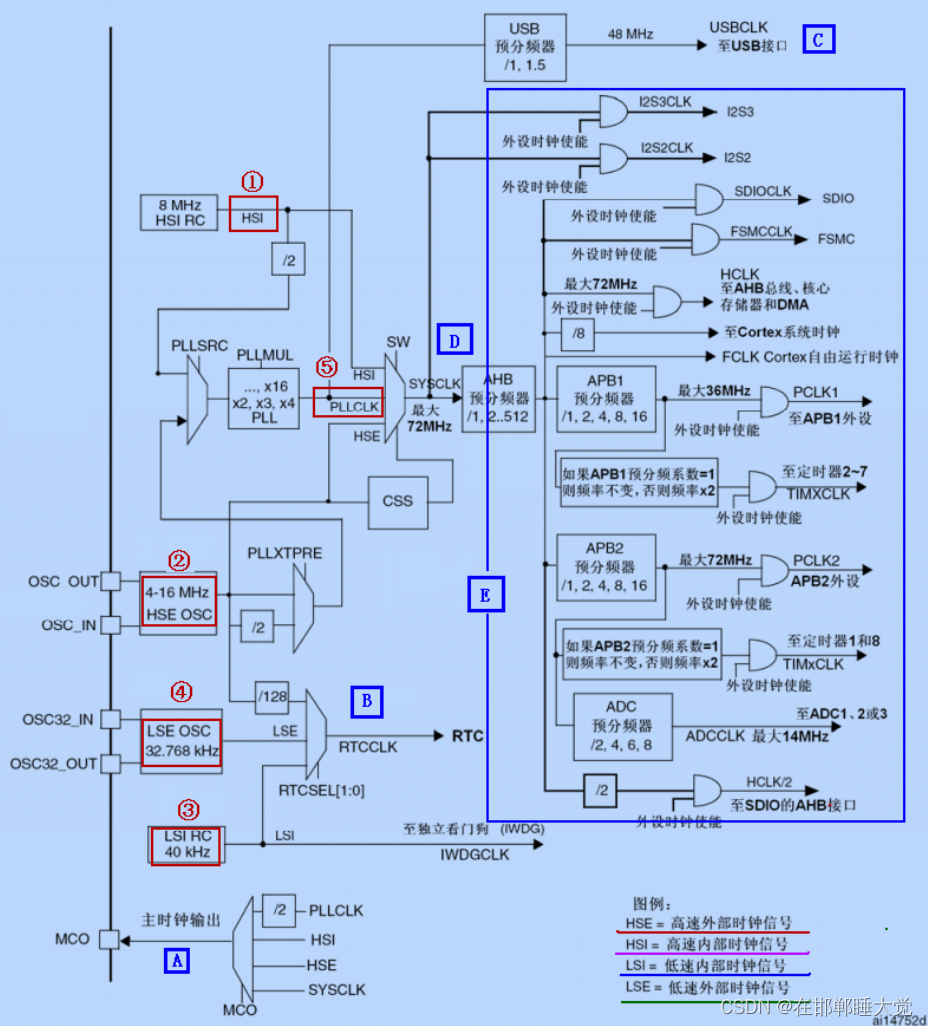

二、系统时钟

时钟系统是 CPU 的脉搏,就像人的心跳一样。STM32有许多时钟,同一个电路,时钟越快功耗越大。所以需要不同时钟。如图STM32有5个时钟。有五个时钟源,为 HSI、HSE、LSI、LSE、PLL。

1、HSI 是高速内部时钟,RC 振荡器,频率为 8MHz。

2、HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~16MHz。我们的开发板接的是 8M 的晶振。

3、LSI 是低速内部时钟,RC 振荡器,频率为 40kHz。独立看门狗的时钟源只能是 LSI,同

时 LSI 还可以作为 RTC 的时钟源。

4、LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体。这个主要是 RTC 的时钟源。 5、PLL 为锁相环倍频输出,其时钟输入源可选择为 HSI/2、HSE 或者 HSE/2。

SystemInit()函数中设置的系统时钟大小: SYSCLK(系统时钟)72,AHB 总线时钟(使用 SYSCLK) 72,APB1 总线时钟(PCLK1)36, APB2 总线时钟(PCLK2)72,PLL 时钟72

APB1 上面连接的是低速外设,包括电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3 等等,APB2 上面连接的是高速外设包 括 UART1、SPI1、Timer1、ADC1、ADC2、所有普通 IO 口(PA~PE)、第二功能 IO 口等。

本文详细介绍了STM32F103系列微控制器的系统架构,包括主系统的驱动单元(内核DCode总线、系统总线、DMA)和被动单元(AHB/APB桥、Flash、SRAM、FSMC),以及五个时钟系统的功能和配置。特别关注了总线矩阵和时钟选择的重要性。

本文详细介绍了STM32F103系列微控制器的系统架构,包括主系统的驱动单元(内核DCode总线、系统总线、DMA)和被动单元(AHB/APB桥、Flash、SRAM、FSMC),以及五个时钟系统的功能和配置。特别关注了总线矩阵和时钟选择的重要性。

4133

4133

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?