网表生成后进行IP封装步骤

总目录链接:https://blog.youkuaiyun.com/m0_37660088/article/details/122646925

**说明:**verilog代码可直接生成IP核,下面介绍通过网表文件生成IP核

步骤:

1 生成网表文件

1.1 打开源代码工程文件

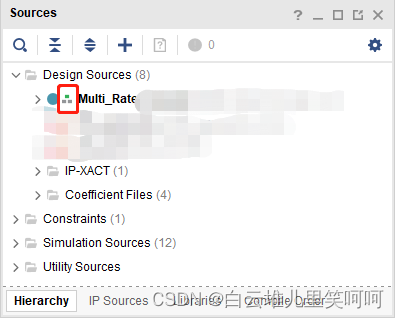

1.2 将需要生成网表文件的源代码设置成顶层文件(点击文件,右击后列表中“Set as Top”)

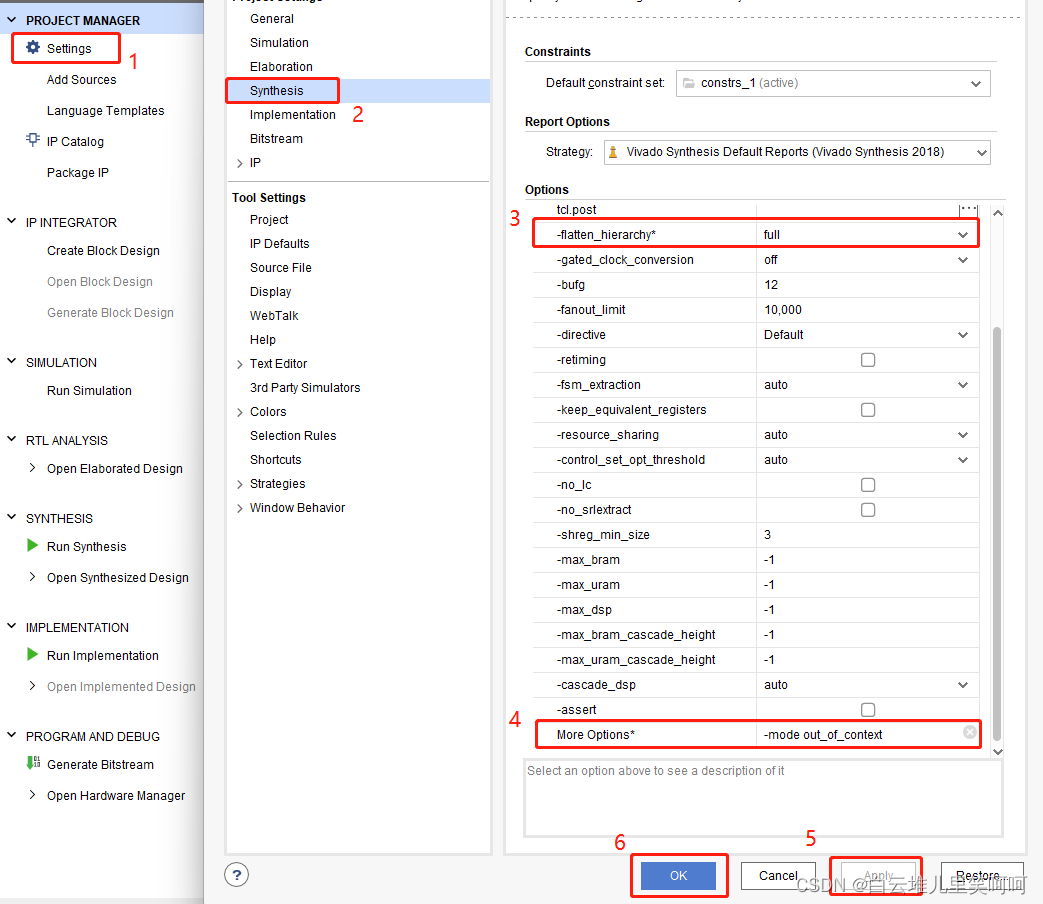

1.3 综合设置

说明:在第3步中,不同的选择封装IP时会有不同,后面分类进行介绍。

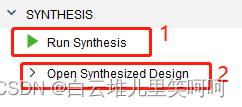

1.4 对模块综合(不用进行下一步)

1.5 生成网表文件

该过程分两种情况。当1.3综合设置第3步选full时,需要生成.edf与.v两个文件才能封装IP。当1.3综合设置第3步选rebuilt时,只需生成.edf文件即可封装IP。

**说明:**full可将生成的网表文件仅包含输入输出名,将代码中的结构关系一同隐藏了。rebuilt则包含结构关系。

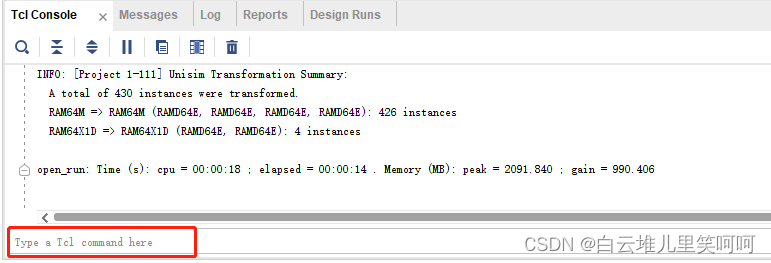

生成.v文件,在上框内输入以下内容:

//vivado 2017.4及以前

write_verilog -mode port <design_name>.v

//vivado 2018.1及以后

write_verilog -mode synth_stub <design_name>.v

//<design_name>.v为设置的文件路径及.v文件名,例如:D:/Users/Desktop/1/a.v (注意斜线)

生成.edf文件,在上框内输入以下内容:

//模块不包含Xilinx的IP

write_edif <design_name>.edf

//模块包含Xilinx的IP

write_edif -security_mode all <design_name>.edf

//<design_name>.edf为设置的文件路径及.edf文件名,例如:D:/Users/Desktop/1/a.edf (注意斜线,与.v文件名保持相同)

当1.3综合设置第3步选full时生成的文件:

当1.3综合设置第3步选rebuilt时生成的文件:

2 将网表文件封装成IP核

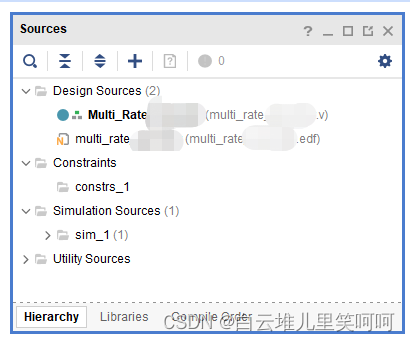

2.1 当1.3综合设置第3步选full时,新建工程并导入.edf与.v文件

然后按照IP核的生成步骤完成即可。

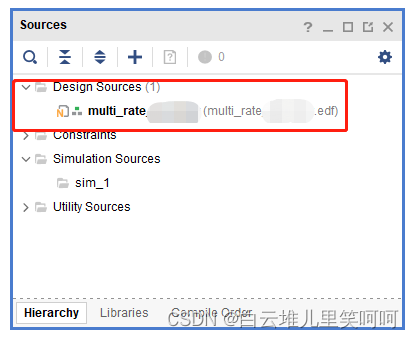

2.2 当1.3综合设置第3步选rebuilt时,新建工程并导入.edf文件(改文件与上步.edf文件不同)

然后按照IP核的生成步骤完成即可。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?