目录

一、 内容概要

- 分别用Verilog和Nios软件编程, 实现DE2-115开发板串口输出“Hello Nios-II”字符到笔记本电脑串口助手。

二、 Hello Nios-II

2.1 Nios-II编程

2.1.1 硬件

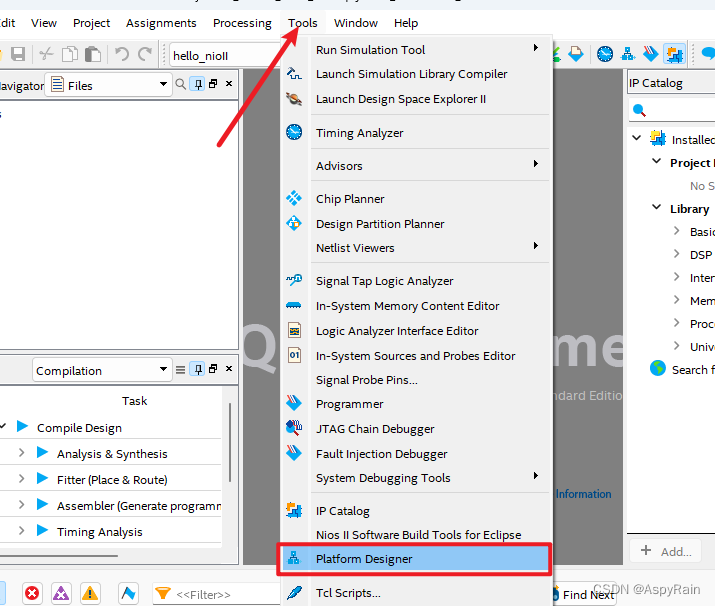

Ⅰ 搭建环境

新建工程,选择开发板

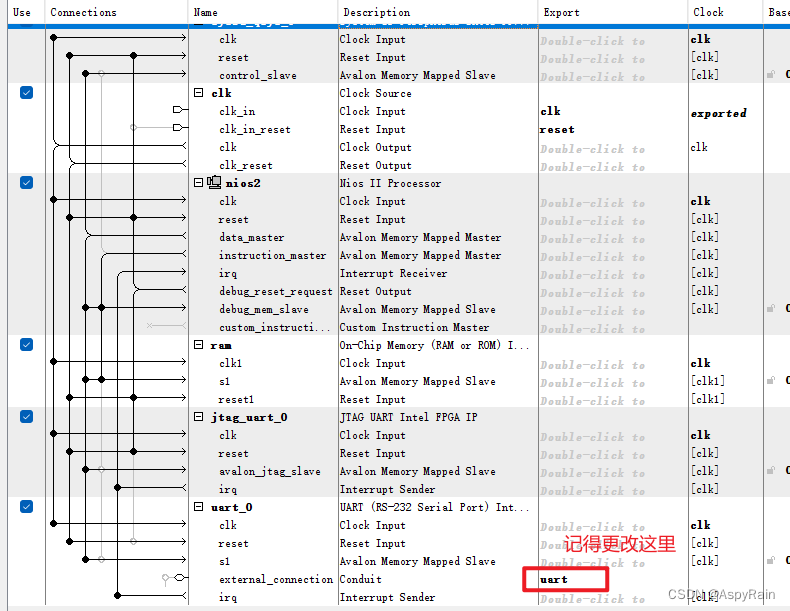

进行模块添加和连接

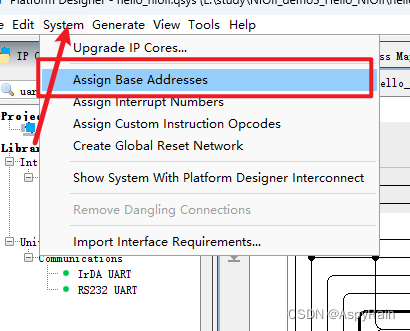

分配地址

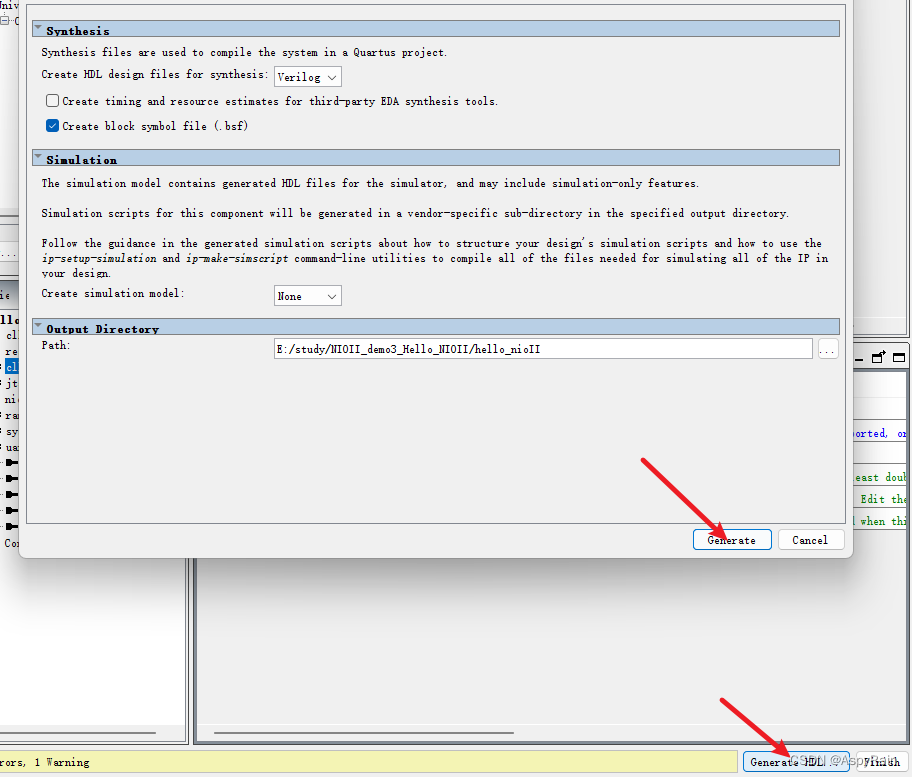

Generate

Ⅱ 编写代码

新建Verilog文件

module uart(

input clk,

input reset_n,

//uart的接收和发送端

input rxd,//接收

output txd//发送

);

endmodule

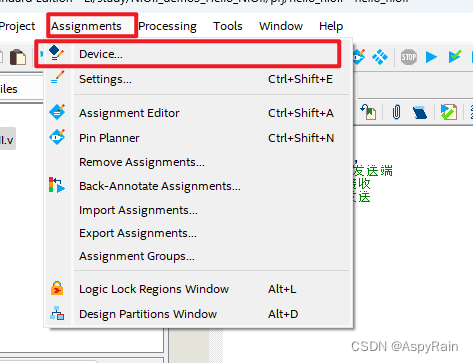

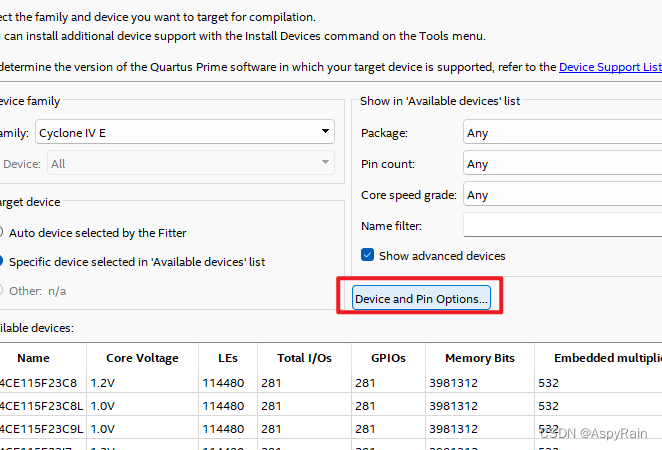

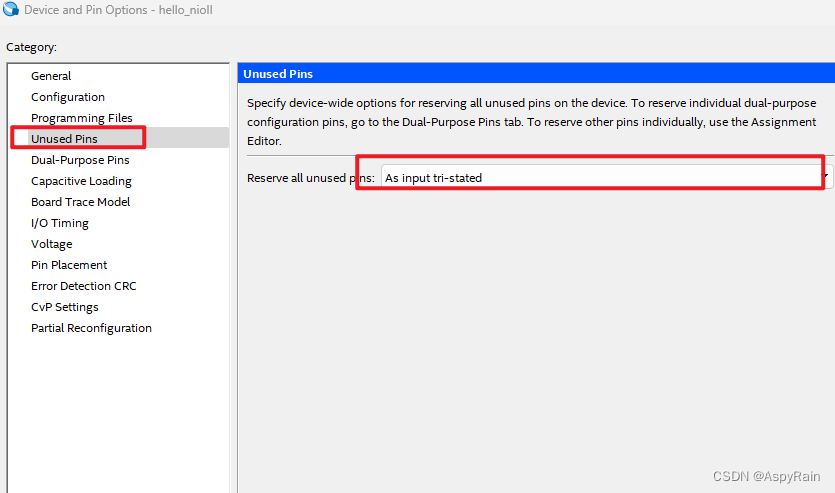

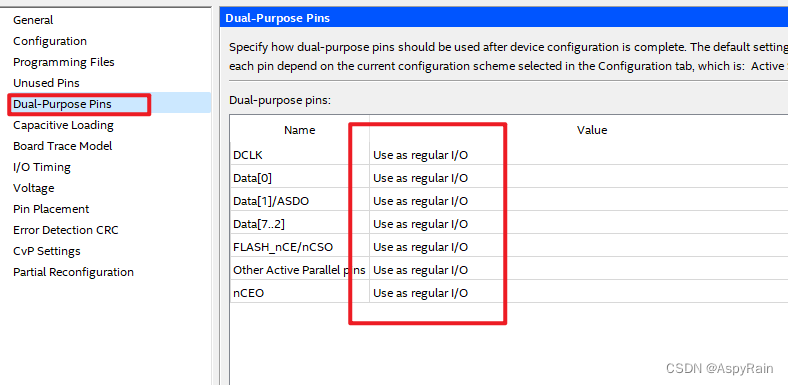

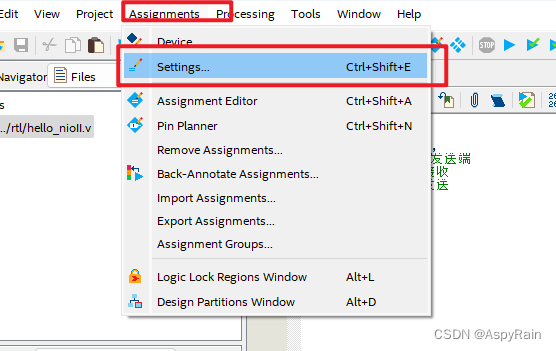

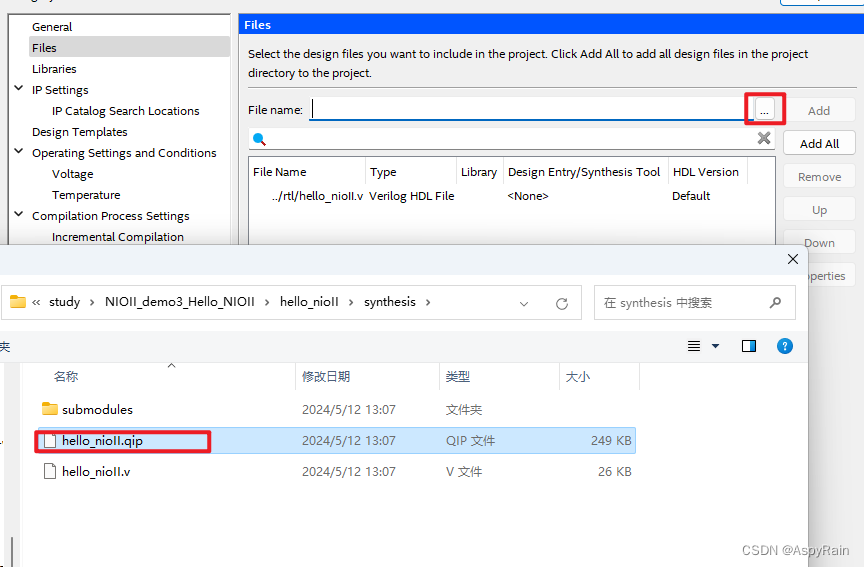

配置

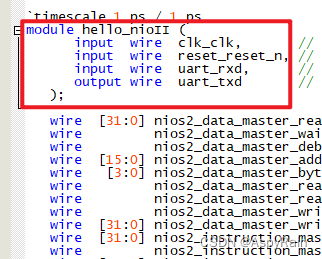

进入qip文件的第一个verilog文件

根据模块信息,在顶层文件里增加:

hello_nioII u0 (

.clk_clk (clk), // clk.clk

.reset_reset_n (reset_n), // reset.reset_n

.uart_rxd (rxd), // uart.rxd

.uart_txd (txd) // .txd

);

完整代码为:

module uart(

input clk,

input reset_n,

//uart的接收和发送端

input rxd,//接收

output txd//发送

);

hello_nioII u0 (

.clk_clk (clk), // clk.clk

.reset_reset_n (reset_n), // reset.reset_n

.uart_rxd (rxd), // uart.rxd

.uart_txd (txd) // .txd

);

endmodule

编译

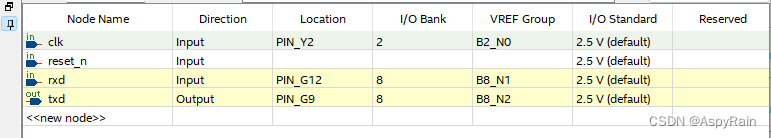

配置管脚

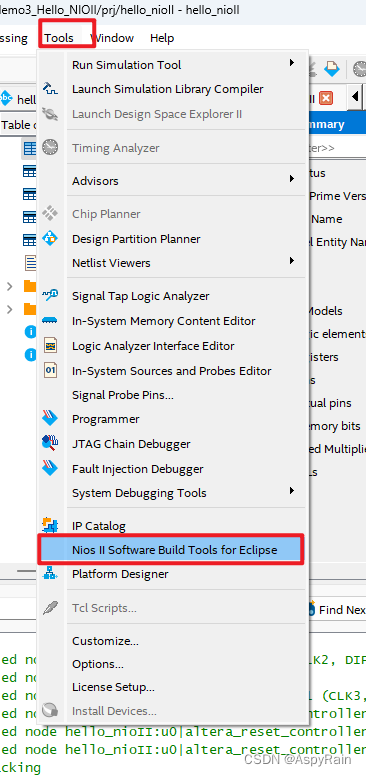

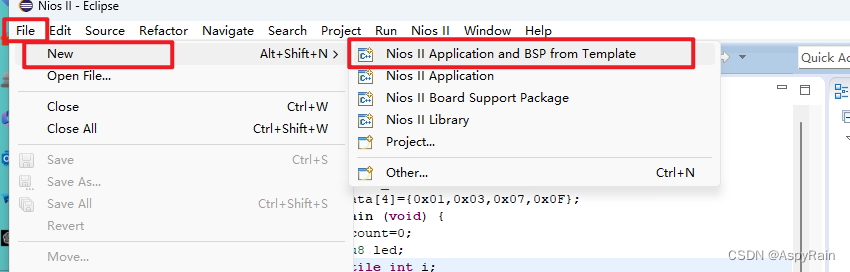

2.1.2 软件

修改hello_world.c

#include <stdio.h>

#include "unistd.h"

#include "system.h"

#include "alt_types.h"

#include "altera_avalon_uart_regs.h"

#include "sys\alt_irq.h"

alt_u8 txdata=0 Nios-II与Verilog在DE2-115上的串口通信实战与心得

Nios-II与Verilog在DE2-115上的串口通信实战与心得

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3953

3953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?