背景

使用门控时钟可以有效降低动态功耗。

门控时钟在 ASIC 中使用较多,在 FPGA 使用较少,使用门控时钟会影响时序分析

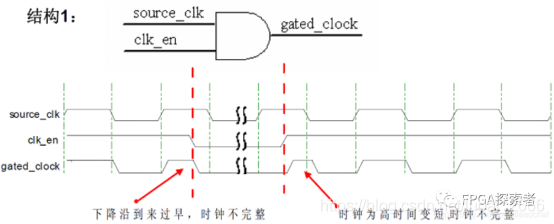

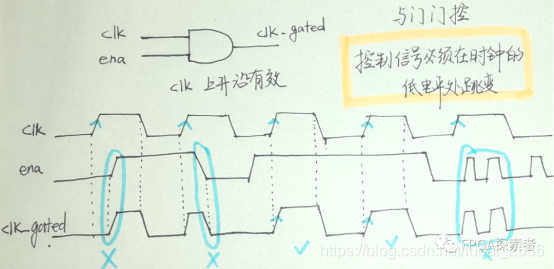

原则:门控时钟的输出只能跟着时钟信号进行跳变,而不能跟着控制信号进行跳变

上升沿有效的clk

对上升沿有效的 clk,使用与门进行门控,ena 控制信号只能在时钟低电平处跳变,这样才能保证时钟的完整

在clk高电平区间,只要en变化,输出的data_clk也会跟着变化,因此会带来毛刺或者时钟不完整问题。所以在clk高电平区间,ena要保持稳定。

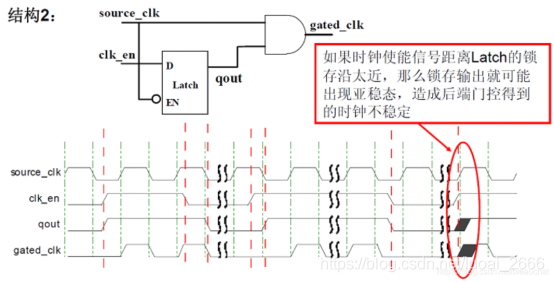

改进(1):使用一个锁存器,时钟 CLK 取反后作为使能端。

作用:保证clk高电平期间,锁存器处于锁存状态,ena稳定。

这种门控方法避免了门控时钟的不完整性,也可以避免毛刺的产生,但门控后的时钟可能会产生亚稳态。

改进(2):使用下降沿触发的 D 触发器寄存使能信号。

门控时钟用于降低动态功耗,常见于ASIC设计中。文章讨论了上升沿和下降沿有效的门控时钟设计,强调了控制信号跳变的正确时机以避免时钟不完整和毛刺。提出了两种改进方案:使用锁存器和下降沿触发的D触发器,以解决亚稳态和时序问题。最后提出,控制信号在时钟的低电平或高电平区跳变是遵循设计原则的关键。

门控时钟用于降低动态功耗,常见于ASIC设计中。文章讨论了上升沿和下降沿有效的门控时钟设计,强调了控制信号跳变的正确时机以避免时钟不完整和毛刺。提出了两种改进方案:使用锁存器和下降沿触发的D触发器,以解决亚稳态和时序问题。最后提出,控制信号在时钟的低电平或高电平区跳变是遵循设计原则的关键。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?