提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

背景:我自己的项目,需要应用到STM32F401,启动时候需要从HSI RC内部振荡器工作,等外部HSE工作后,再切换到外部。有时候HSE会停止。这时候还能够回到初始状态作。

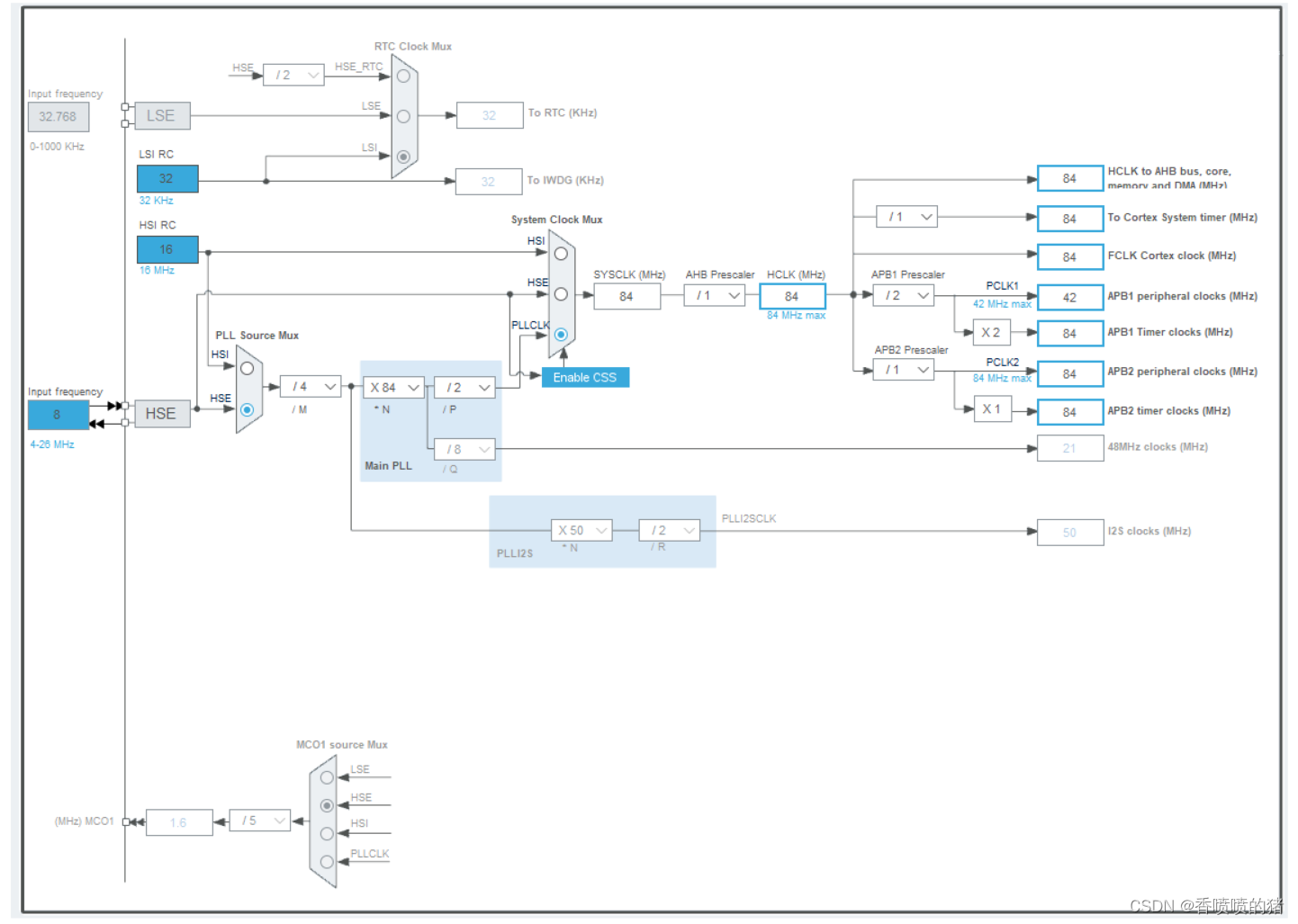

一、STM32时钟树

STM32F4的时钟系统如下图:

二、HSI切换到HSE

1.初始化

由于切换到HSE后,如果HSE停止,系统将不工作,所以需要增加看门狗来回倒初始状态。并且RCC->CR中的RCC_CR_HSERDY状态会出错,所以更需要看门狗来处理。

代码如下:

int main(void)

{

HAL_Init();

SystemClock_Config();

MX_GPIO_Init();

MX_USART1_UART_Init();

MX_TIM1_Init();

MX_TIM3_Init();

MX_IWDG_Init();

/* USER CODE BEGIN 2 */

printf("====================================================\r\n");

printf("System Freq : %dMHz\r\n",HAL_RCC_GetHCLKFreq()/1000000);

printf("====================================================\r\n");

printf("Opening HSE......\r\n");

SET_BIT(RCC->CR, RCC_CR_HSEON);

printf("Check HSE......\r\n");

while(READ_BIT(RCC->CR, RCC_CR_HSERDY) == RESET)

{

HAL_Delay(50);

HAL_IWDG_Refresh(&hiwdg);

}

printf("Check HSE is ready.\r\n");

2.外部时钟频率检测

代码如下:

HAL_RCC_MCOConfig(RCC_MCO1, RCC_MCO1SOURCE_HSE, RCC_MCODIV_5);

printf("OPEN MCO DIV_5......\r\n");

打开MCO,5分频输出到TIM1做计数器。来计算当前的频率。

3.切换到HSE

切换HSE,如果直接 SystemClockHSE_Config()会出错。需要先HAL_RCC_DeInit();

代码如下:

HAL_RCC_DeInit();

SystemClockHSE_Config();

4.错误处理

当HSE停止的时候有一定的概率会出错。HSI的初始化也不成功。进入到Error_Handler();

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

Error_Handler的处理代码如下,否则就死在这里,因为看门狗这个时候还没有初始化。只能软复位重新再来。当HSE恢复的时候一切就正常了。在我的 应用中是如此的。对于错误的具体表现就是RCC_CR_HSERDY一直是Ready状态。即使没有打开HSE。并且也无法清除状态,复位也不能恢复,只有掉电或者HSE恢复才能清掉这个状态。

/* USER CODE END 4 */

/**

* @brief This function is executed in case of error occurrence.

* @retval None

*/

void Error_Handler(void)

{

/* USER CODE BEGIN Error_Handler_Debug */

/* User can add his own implementation to report the HAL error return state */

__disable_irq();

while (1)

{

__disable_irq();

__set_FAULTMASK(1);

CLEAR_BIT(RCC->CR, RCC_CR_PLLON);

CLEAR_BIT(RCC->CR, RCC_CR_HSEON);

MX_USART1_UART_Init();

printf("No sclk signal input, pls reset local slave chip.......\r\n");

printf("The system will restart\r\n");

NVIC_SystemReset();

}

/* USER CODE END Error_Handler_Debug */

}

总结

HSI和HSE切换,这样的应用比较少。所以记录一下,希望有所帮助。有问题可以留言讨论一下。

本文详细介绍了在STM32F401项目中,如何从HSI内部振荡器切换到HSE外部振荡器,并在HSE停止时通过看门狗恢复初始状态。过程中涉及STM32的时钟树结构,HSI到HSE的切换步骤,外部时钟频率检测以及错误处理机制。在HSE出现问题时,系统能通过错误处理函数进行软复位,重新启动。

本文详细介绍了在STM32F401项目中,如何从HSI内部振荡器切换到HSE外部振荡器,并在HSE停止时通过看门狗恢复初始状态。过程中涉及STM32的时钟树结构,HSI到HSE的切换步骤,外部时钟频率检测以及错误处理机制。在HSE出现问题时,系统能通过错误处理函数进行软复位,重新启动。

2547

2547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?