原文链接:https://blog.youkuaiyun.com/tbzj_2000/article/details/88304245

为了提供更好的信号完整性,DDR3的memory controller可以使用write leveling来调整DQS差分对和CK差分对的相对位置,利用DQS差分对路径上的可调整延时来达成该目的。

对于简单的运用,比如on-board DDR memory,并且仅有一颗DDR内存的情况下可以考虑不需要做write leveling。

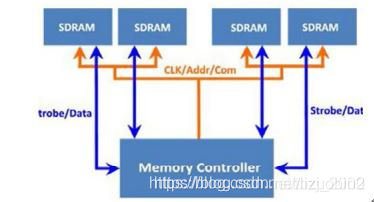

T型布线,如下图。该布线方式同步切换噪声(Simultaneous Switching Noise) 较大。

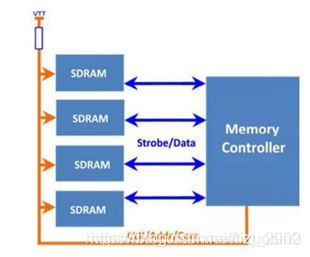

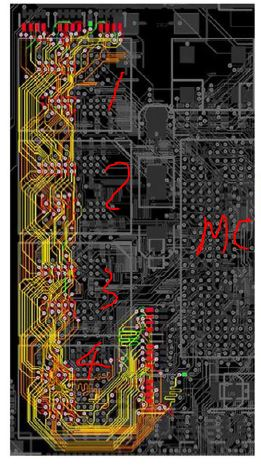

所谓的fly-by 布线,指地址、命令和时钟的布线依次经过每一颗DDR memory芯片(即每一颗芯片共用了这些信号,在Lattice DDR SDRAM controller IP配置时,则ClockWidth要求设置为1)。而dq和dqs作了点到点的连接。因此,dq dqs 到每一个DDR颗粒与clk不等长。VTT表示这些信号都接了ODT端接电阻。fly-by 结构相对于T布线,有助于降低同步切换噪声(Simultaneous Switching Noise)。

Write Leveling的功能是调整DRAM颗粒端DQS信号和CLK信号边沿对齐;调节过程描述:DDR控制器不停地调整DQS信号相对于CLK的延迟,DRAM芯片在每个DQS上升沿采样CLK管脚上的时钟信号,如果采样值一直低,则会将所有的DQ[n]保持为低电平来告知DDR控制器,tDQSS(DQS, DQS# rising edge to CK, CK# rising edge,在标准中要求为+/-0.25 tCK。tCK为CLK时钟周期)相位关系还未满足,如果发现在某个DQS上升沿,采样到此时的CLK电平发现了迁越(由之前的低跳变为高),则认为此时DQS和CLK已经满足tDQSS,同时通过DQ[n]向DDR控制器发送一个高,表征一个写均衡成功,同时DDR控制器会锁住这个相位差。这样,在每个DRAM端,看到的CLK和DQS信号都是边沿对齐的。

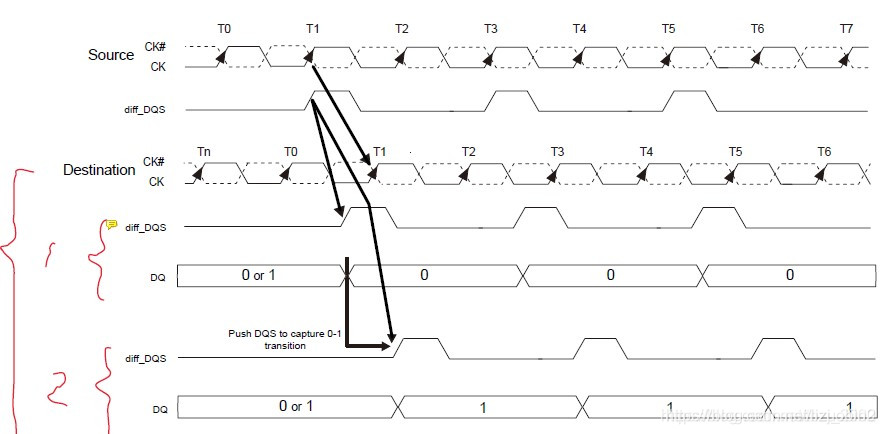

参考DDR3标准的写入均衡的4.8.2 procedure description一节和上图,写入均衡的修调过程:

t1:将ODT拉起,使能on die termination;

t2:等待tWLDQSEN时间后(保证DQS管脚上的ODT已设置好),DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ保持为0。

t3:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ仍然保持为0。

t4:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=1,则等待一段时间后,DDR memory将dq信号置起。

采取以上策略的原因:对于DDR controller来说,其无法测定clk边沿和dqs边沿的绝对位置,故采用了不断调整dqs delay,在dqs上升沿判断clk从0到1或1到0的一个变化,一旦检测到变化,则写入均衡停止。

DDR3标准的Figure 17 write leveling concept图不太好理解,以下进行说明。

从1中的两个信号diff_DQS和DQ,可以看到 diff_DQS的上升沿采到的CK值都是0;

将diff_DQS加延时,直到如2 中所示diff_DQS的上升沿采到的CK值都是1,进而DQ输出从0到1,完成写入均衡(write leveling)。

注意:在DDR3的标准文档中,在同一个时序图中经常性看到有多个相同信号名,但波形不同的情况,需要结合上下文分析波形。

布线要求:

只有使用了fly-by的情况下需使能write leveling

CPU内部的内存控制器只能对DQS信号做延迟,不能做超前处理,所以CK要大于DQS信号线的长度,否则将不能满足tDQSS

实战说明:

对于Lattice VIP board,两块DDR芯片的布线使用了fly-by布线,故需使能Write leveling。即在Clarity designer的DDR3 SRAM controller的配置窗口的Type页面,将Write leveling钩选上。

将MR1寄存器的A7设置为1进入write leveling模式,然后在检测到DQ上有0到1的跳变后,说明已结束,则设置A7为0退出该模式。

本文详细介绍了DDR3中Write Leveling技术的工作原理及其在不同布线方式下的应用。包括如何通过调整DQS信号相对于CLK信号的位置实现信号完整性优化,以及在fly-by布线结构中的必要性和具体实施步骤。

本文详细介绍了DDR3中Write Leveling技术的工作原理及其在不同布线方式下的应用。包括如何通过调整DQS信号相对于CLK信号的位置实现信号完整性优化,以及在fly-by布线结构中的必要性和具体实施步骤。

799

799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?