在使用UVM寄存器模型时,当对寄存器进行读操作时,有很多种方法,这里介绍最常用的方法:

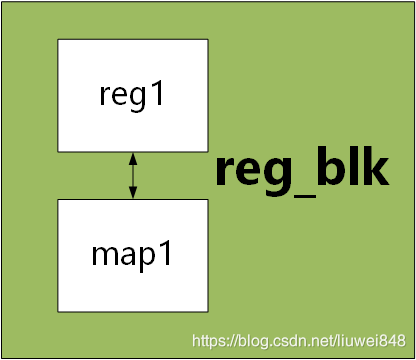

假设已经生成了一个uvm_reg_block模型,名字时reg_blk,在模型中有一个寄存器名字叫reg1。并且reg1添加到了名字是map1的uvm_reg_map中

在这里插入代码片

下面来讲解一下寄存器模型是如何完成read操作的

extern virtual task read(output uvm_status_e status,

output uvm_reg_data_t value,

input uvm_door_e path = UVM_DEFAULT_DOOR,

input uvm_reg_map map = null,

input uvm_sequence_base parent = null,

input int prior = -1,

input uvm_object extension = null,

input string fname = "",

input int lineno = 0);

status: 表示操作状态,OK or NOT OK

value: 表示读出的值

path: 表示是前门访问还是后门访问

map: 表示 如果是前门访问时用哪个map。

parent:表示哪个sequence来发送RAL item读操作请求

prior:表示item的优先级

extension:表示一些扩展信息,这个后续博客介绍

fname和lineno没有什么用,暂时不用去care

task uvm_reg::read(output uvm_status_e status,

output uvm_reg_data_t value,

input uvm_door_e path = UVM_DEFAULT_DOOR,

input uvm_reg_map map = null,

input uvm_sequence_base parent = null,

input int prior = -1,

input uvm_object extension = null,

input string fname = "",

input int lineno = 0);

XatomicX(1);

XreadX(status, value, path, map, parent, prior, extension, fname, lineno);

XatomicX(0);

endtask: read

XatomicX(1)也是为了获得操作权限,重点是方法XreadX

task uvm_reg::XreadX(output uvm_status_e status,

output uvm_reg_data_t value,

input uvm_door

本文详细介绍了在UVM寄存器模型中如何执行读操作,包括前门和后门访问的实现过程,涉及do_read、check_access、预读回调等关键步骤,以及front_door_sequence和backdoor访问策略的判断。

本文详细介绍了在UVM寄存器模型中如何执行读操作,包括前门和后门访问的实现过程,涉及do_read、check_access、预读回调等关键步骤,以及front_door_sequence和backdoor访问策略的判断。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6753

6753

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?