目录

01异常现象

某信息技术类产品依据标准GB 9254.2进行静电放电试验。在对外壳缝隙处进行空气放电±8kV时,出现系统死机,需要重新上电才能正常工作。判定不合格。

02原因分析

静电放电空气放电形成拉弧放电的电磁干扰,存在高频的空间辐射噪声。在以往的静电整改案例中都有提及,不再做过多的描述。感兴趣可以翻看我以往发的文章。该产品同样是空气放电出现工作异常,因此产品内部必然存在比较大的信号环路,拾取到了静电放电所产生的高频电磁干扰。环路的大小与其所感应电动势成正比,相同电磁环境中,环路越大,感应电动势也越大。

查看产品内部整体结构,没有发现明显的非屏蔽长线缆,整体结构相对比较紧凑。询问软件同事,该死机问题是由于DDR数据错误导致。为验证是否是DDR被干扰导致产品异常,将静电放电电压调至200V,对着DDR信号放电测试。发现确实会出现死机问题。DDR的供电电压是1.5V,相对来讲是比较低的。按通用0.7倍VCC为高电平,0.3倍VCC为低电平的原则 ,其容噪电压才0.45V。这类信号的抗干扰能力是比较差,在原理图和PCB设计时就需要提前规划,做EMC设计。

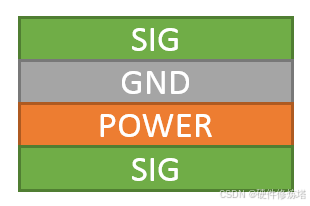

查看DDR的PCB设计,发现DDR走线最小环路并不是第一优先级,还给其它信号线有让路的情况。这导致DDR走线环路增加不少。另外PCB采用4层板设计,为比较经典的4层板层叠设计方案:SIG-GND-POWER-SIG,如下图所示。

在4层板层叠设计中,采用“信号层-地层-电源层-信号层”的结构是一种常见的设计方式。这种方式的从EMC设计角度来讲,其优点有:

信号层与地层和电源层相邻,能够提供良好的信号回流路径,减少信号干扰和串扰。

电源完整性高:电源层与地层相邻,能够降低电源平面的阻抗,提高电源的稳定性。电源层和地层的紧密耦合可以减少电源噪声,为电路提供更稳定的电源。

但实际这个板的DDR信号,有存在穿层打过孔的情况,这样DDR信号便不在是完美的以GND作为信号回流路径。

03整改方案

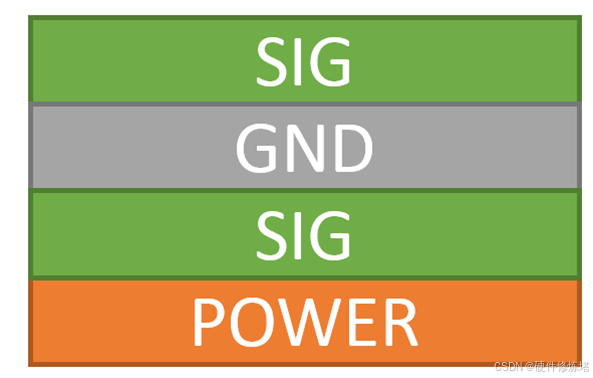

结合PCB的实际情况。最终定下的方案是将PCB的层叠设计改为:SIG-GND-SIG-POWER,如下图所示。DDR信号线走内层。这样的设计方案牺牲了一定的电源完整性,但加强了DDR的抗干扰能力。GND层和POWER层起到一定的屏蔽效果。经PCB重新改板设计测试通过空气放电±8kV测试。

04总结

PCB板的层叠设计并不是一成不变,在通常情况下常用经典层叠设计,基本没啥问题。但有些时候需要根据实际情况做调整。

在静电整改过程中,将静电放电电压调低对某信号线放电测试,是一种常用的定位手段。为啥要将静电电压调低,因为很多芯片抗不住±4kV的静电测试,别一测试,将产品弄坏,还得花大量时间修机。

本博客持续更新中,欢迎大家收藏与关注,谢谢!

457

457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?