助记符 | 说 明 | 操 作 |

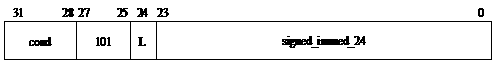

B | 跳转指令 | pc←label |

BL | 带返回的连接跳转 | pc←label(lr←BL后面的第一条指令) |

BX | 跳转并切换状态,绝对地址 | pc←Rm&0xfffffffe, T←Rm&1 |

BLX | 带返回的跳转并切换状态 | pc←lable, T←1 pc←Rm&0xfffffffe, T←Rm&1 lr←BL后面的第一条指令 |

2.STR(条件) 源寄存器,<存储器地址>。

它们是存储器访问指令。ARM中对ROM,RAM,IO地址采用统一编址,除RAM外,对外围IO、程序数据的访问都要采用L/S指令进行操作。2.1 LDR和STR(加载到寄存器,存储到存储器如内存中)

LDR用于把内存中的数据加载到寄存器中,而STR则相反。

LDR R0, [R1] ,把R1所指向的存储单元的内容加载到R0寄存器中

比如 STR R0, [R1] ,意思是R0-> [R1],它把源寄存器写在前面,跟MOV、LDR都相反。

LDR应该是非常常见了。LDR就是把数据从存储器传输到寄存器上。

LDR应该是非常常见了。LDR就是把数据从存储器传输到寄存器上。

例一:

| @ disable watch dog timer mov r1, #0x53000000 //立即数寻址方式 mov r2, #0x0 str r2, [r1] 立即数寻址方式,立即数要求以“#”作前缀,对于十六进制的数,还要求在#后面加上0x或者&。 |

mov r1, #GPIO_CTL_BASE

add r1, r1, #oGPIO_F

ldr r2,=0x55aa // 0x55aa是个立即数啊,前面加个=干什么?

对于当中的ldr 那句,如果你把=去掉,是不能通过编译的。

这个=应该表示LDR不是ARM指令,而是伪指令。作为伪指令的时候,LDR的格式如下: LDR 寄存器, =数字常量/Label 它的作用是把一个32位的地址或者常量调入寄存器。嗬嗬,那大家可能会问, “MOV r2,#0x55aa”也可以啊。应该是这样的。不过,LDR是伪指令啊,

也就是说编译时编译器会处理它的。怎么处理的呢?——规则如下:

如果该数字常量在MOV指令范围内,汇编器会把这个指令作为MOV。

如果不在MOV范围中,汇编器把该常量放在程序后面,

用LDR来读取,PC和该常量的偏移量不能超过4KB。

3.LDM和STM

LDM把一块连续内存单元的数据加载到多个寄存器中 LDM{Con}<mode> Rn{!},{reg_list}{^} STM把多个寄存器的内容存储到一块连续的内存单元中。STM{Con}<mode> Rn{!},{reg_list}{^} CON如IA,FD Rn为基址寄存器,它不能为PC !表示是否要改变Rn的值。 LDMIA R0,{R1-R4},把【R0】开始的四个字加载到R1-R4中,

但R0的值没有变。如果为R0!,则最后R0=R0+4*4

4.MRS(read)和MSR(store)p107ARM9嵌入式系统设计

ARM中对程序状态寄存器的操作由上述两条专用指令实现,而不能由其它指令, MRS 读程序状态寄存器 MSR 写程序状态寄存器。 5.BIC,把标志中的1清0,

实现 “1+2+3+.........+n” AREA TEST, CODE, READONLY ;定义一个代码段 TEST ldr r1, =n ; r1=n begin |

http://blog.chinaunix.net/uid-24219701-id-1628854.html

555

555

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?