- HDMI接口原理

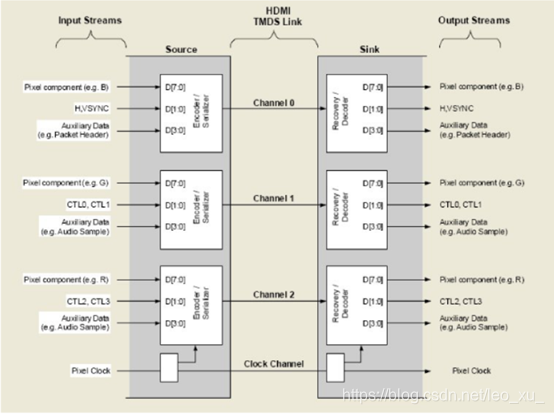

HDMI的连接架构如下图所示,其包括三个TMDS数据通道,一个TMDS时钟通道。每个TMDS时钟通道周期中,三个TMDS数据通道会发送10bit数据。Channel0通道的输入数据流由8bit的蓝色像素点数据、H,VSYNC数据线和包头数据组成。Channel1通道的输入数据流由8bit绿色像素点数据、控制信号和音频采样信号组成。Channel2通道的输入数据流由8bit红色像素点数据、控制信号和音频采样信号组成。三个通道的输入源数据流经过8B/10B编码、并串转换后,形成差分对信号并输出到相应的引脚上。

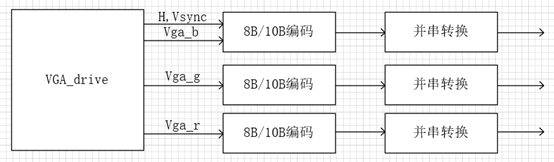

下图为HDMI接口结构的简化图,图中没有用到包头信息、音频采样信号和控制信号。VGA驱动模块输出的像素点数据和行场信号作为HDMI接口驱动模块的输入数据源。

- VGA驱动原理

显示器采用逐行扫描,扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

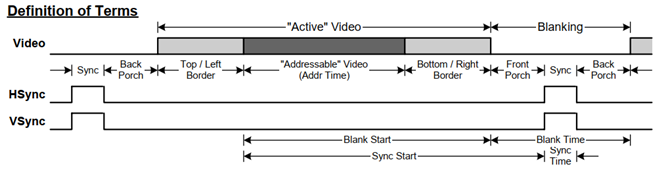

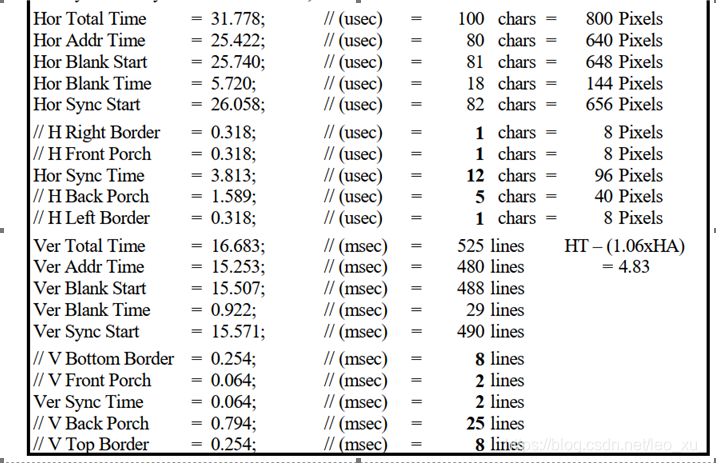

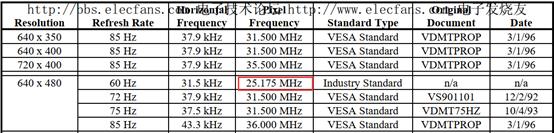

以640x480分辨率的VGA为例,下图是VGA的时序图及其对应的时间参数。VGA时序中,每一行都有一个高电平的行同步脉冲,这个行同步信号的高电平占了96个像素点时钟。在同步脉冲之后是后沿(back porch),左边界(left border)属于消隐区,激活像素区(active video)为显示时序段,最后是右边界(right border)和前沿(front porch)。每扫描完一帧图像会产生一个高电平的场同步脉冲,这个行同步信号的高电平占了2行像素点时钟。

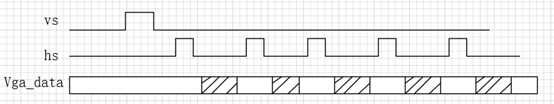

下图是简化的vga时序图,像素数据vga_data中阴影部分为有效显示像素区域。

- HDMI接口实现

行场时序和RGB(8,8,8)像素数据可利用VGA驱动模块进行实现,8B/10B编码模块可采用迪芝伦公司提供的免费模块进行实现,并串转换可采用OSEDERS模块将10bit信号转换成串行差分信号输出。

1.VGA驱动模块代码如下,该模块可以让屏幕显示出3个彩条:

`timescale 1ns/1ns

module vga_drive(

// system signals

input sclk ,

input s_rst_n ,

// VGA

output wire vga_hs ,

output wire vga_vs ,

output reg [7:0] vga_r ,

output reg [7:0] vga_b ,

output reg [7:0] vga_g ,

output reg vga_de

);

//========================================================================\

// =========== Define Parameter and Internal signals ===========

//====================&

本文介绍了基于FPGA的HDMI接口设计方法,包括HDMI接口原理,其连接架构包含三个TMDS数据通道和一个时钟通道。内容详细讲解了VGA驱动模块的工作原理,以及如何利用VGA驱动模块、8B/10B编码模块和OSEDERS模块实现HDMI接口。最后提供了VGA驱动模块代码和SelectIO IP核的配置示例。

本文介绍了基于FPGA的HDMI接口设计方法,包括HDMI接口原理,其连接架构包含三个TMDS数据通道和一个时钟通道。内容详细讲解了VGA驱动模块的工作原理,以及如何利用VGA驱动模块、8B/10B编码模块和OSEDERS模块实现HDMI接口。最后提供了VGA驱动模块代码和SelectIO IP核的配置示例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?