set power_analysis_mode

-averaged

平均功耗

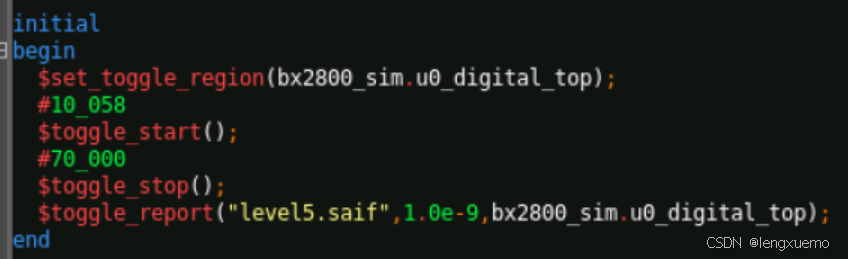

vcs仿真截取一段波形,生成.saif文件,在PTPX中读入.saif文件,然后分析得到平均功耗值.

其中生成.saif文件的命令如图:

-time_base

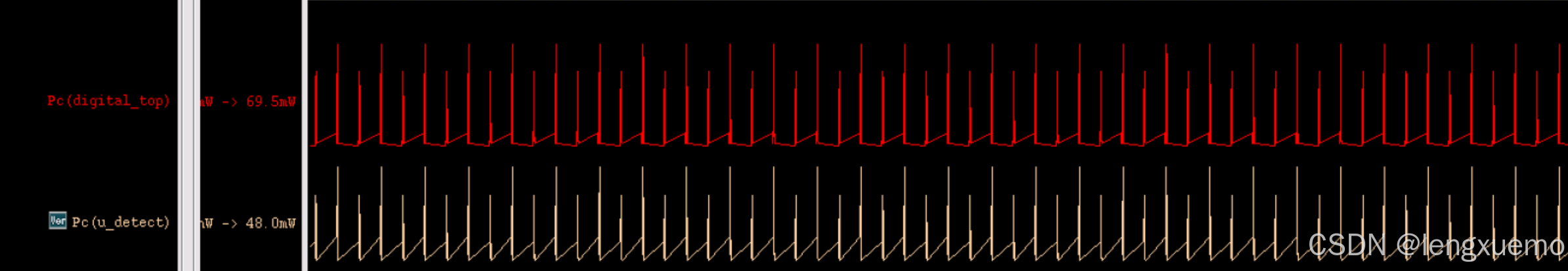

可以理解成瞬时功耗,放到verdi中可以看到每个时刻点的功耗情况,如图:

想要得到这样的瞬时功耗,需要把vcs仿真得到的.fsdb文件读入到PTPX中,然后通过PTPX生成一个带功耗信息的.fsdb文件(px.fsdb).然后将px.fsdb读入到verdi中就可以查看每个时刻点的功耗.

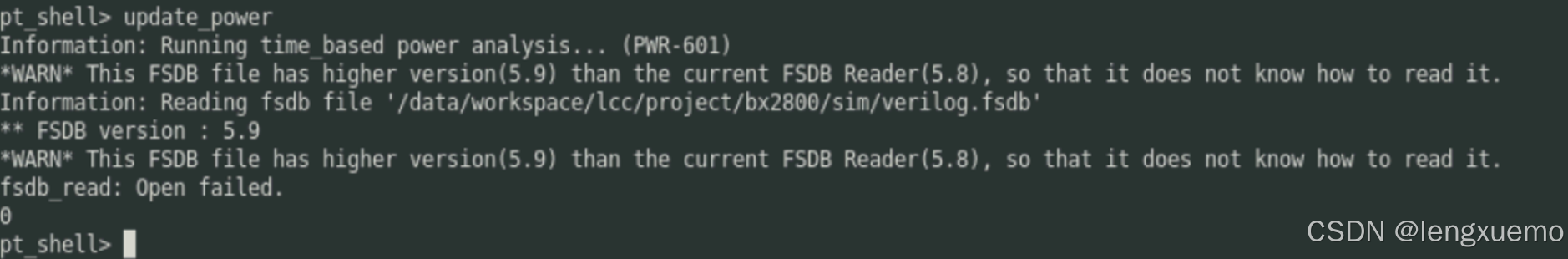

其中,在PXPT读入.fsdb时可能会出现版本不兼容的问题,如图:

在网上查了各种办法都没有解决,最后通过将fsdb转换成vcd文件可以解决这个问题,因为PXPT也可以读入vcd文件.

转换命令:

fsdb2vcd verilog.fsdb -o verilog.vcd

可以理解成这也是一个小软件.至于fsdb和vcd的区别,可以网上自行查资料,简单来说就是vcd文件要比fsdb文件大,等等

有了vcd文件后,将vcd文件读入到ptpx.经过ptpx分析后,吐出新的fsdb文件.因为verdi支持的fsdb版本高,所以可以直接吐出fsdb文件,不然的话需要吐出vcd文件.

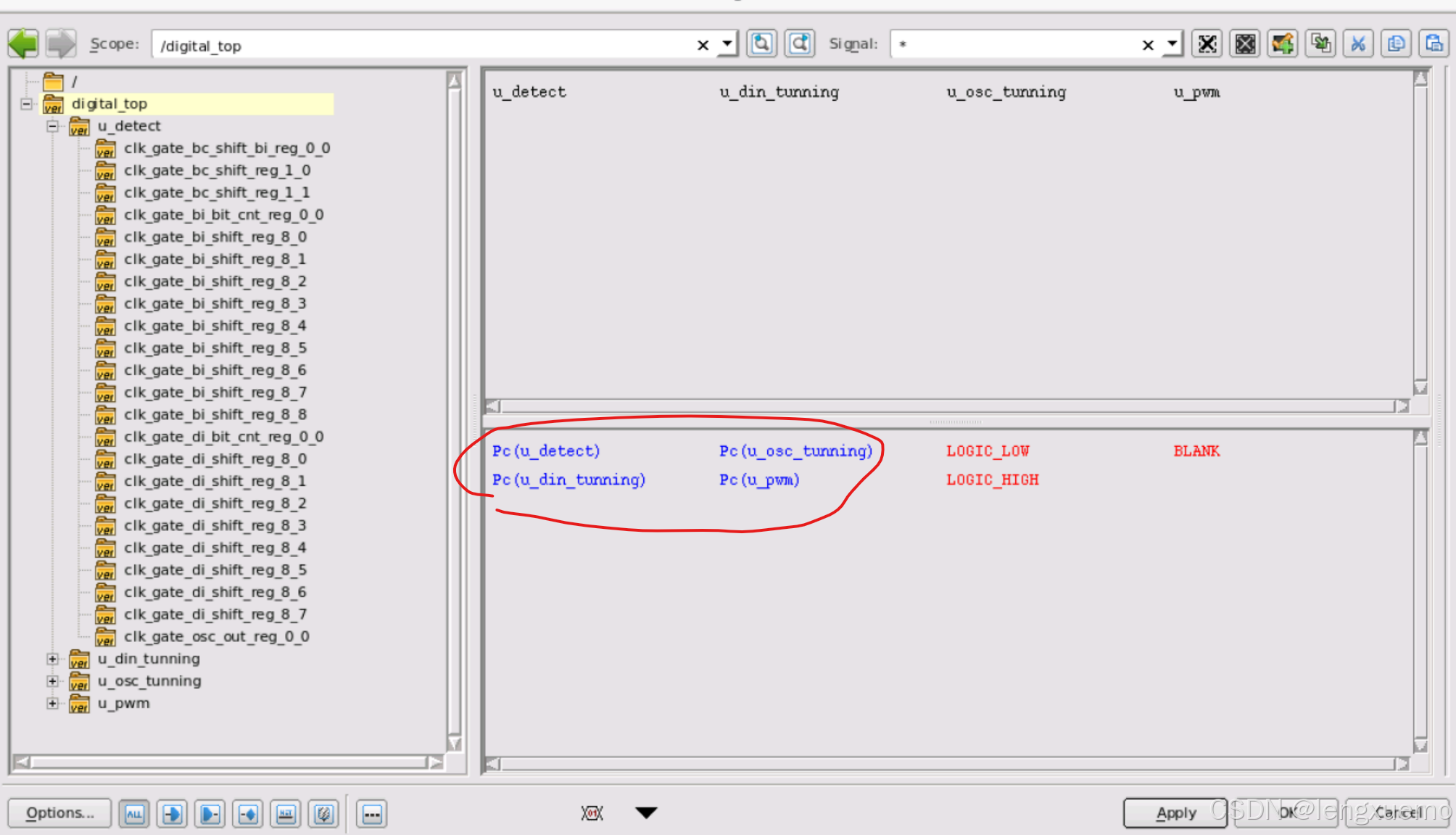

这里还有一点需要注意, verdi看功耗波形时,不知如何显示波形请参考以下:

verdi 加载完fsdb后,在波形窗口按g,然后出现如图:

其中Pc(xxx) 就是功耗的波形.

完成的tcl文件如下图:

set link_library {* xxx.db}

set search_path {* ../pr/output/ ../lib_db/}

set power_enable_analysis TRUE

#set power_analysis_mode averaged

set power_analusis_mode time_base

read_verilog digital_top.v

current_design digital_top

link

read_sdc -echo ../syn/sdc/digital_top.sdc

#read_fsdb ../sim/verilog.fsdb -strip_path tb_sim/u_digital_top

read_vcd ../sim/verilog.vcd -strip_path tb_sim/u_digital_top

#read_saif ../sim/digital_top.saif -strip_path tb_sim/u_digital_top

report_switching_activity -list_not_annotated

check_power

update_power

report_power -hierarchy -verbose

set_power_analysis_options -waveform_format fsdb -waveform_output px

PTPX与verdi功耗分析实战指南

PTPX与verdi功耗分析实战指南

5799

5799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?