`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name:

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module matrix5x5 #(

parameter C_PIXEL_WIDTH = 16 ,

parameter C_IMAGE_WIDTH = 12'd1280 ,

parameter C_IMAGE_HEIGHT = 12'd1024

)(

input wire sysclk ,

input wire sysrstn ,

input wire [C_PIXEL_WIDTH - 1 : 0] s_axis_rdata ,

input wire s_axis_rvalid ,

input wire s_axis_ruser ,

input wire s_axis_rlast ,

output reg m_axis_tuser ,

output reg m_axis_tlast ,

output reg m_axis_tvalid ,

output reg m_axis_dvalid ,

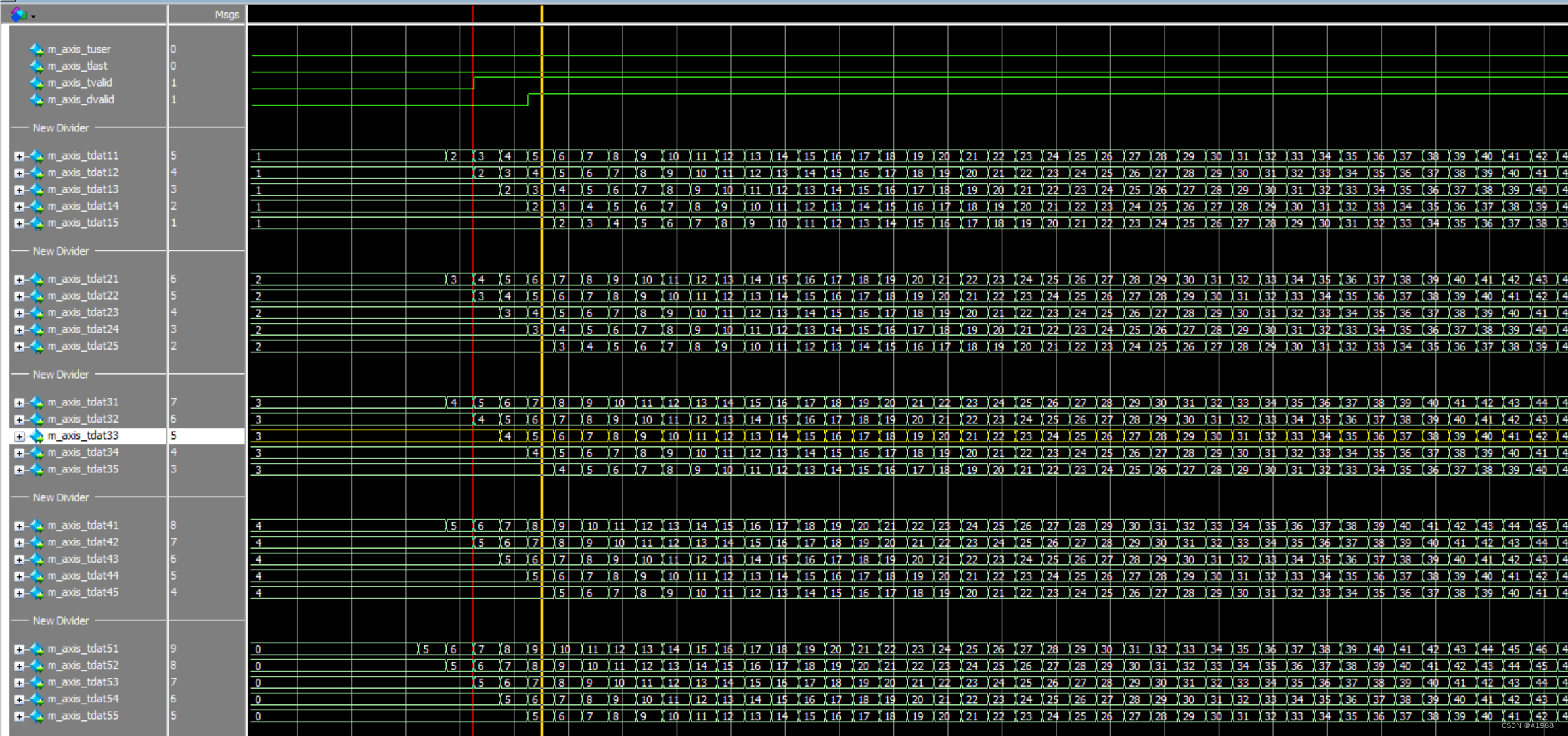

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat11 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat12 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat13 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat14 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat15 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat21 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat22 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat23 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat24 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat25 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat31 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat32 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat33 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat34 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat35 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat41 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat42 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tdat43 ,

output reg [C_PIXEL_WIDTH - 1 : 0] m_axis_tda

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1306

1306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?