文章目录

一、整体项目简介

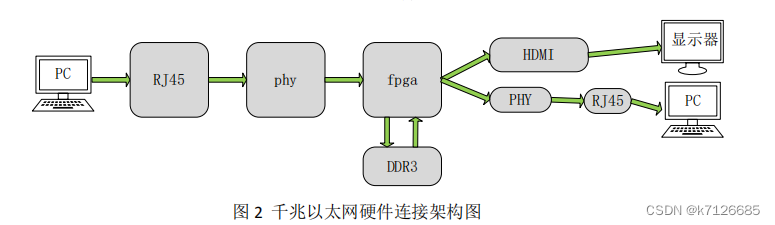

本项目使用 PC 机将图像数据信息通过千兆以太网发送给 FPGA,存储到DDR3 中,HDMI 将 DDR3 中数据读出显示到显示器上,同时将图像数据回传到PC 机对应的上位机上。

二、过程描述

用户通过电脑上位机将一幅 1024*768 图片通过双绞线(网线),发送给板卡网口(RJ45),RJ45 将数据传输给网卡(PHY),PHY 将差分信号转换成双沿数据传输给 FPGA,FPGA 处理完成后将图像信息缓存数据到 DDR3 中,当一帧图像

信息数据存储完成后,将 DDR3 中的数据读出显示加上 UDP 协议传回 PC 机,同时将 DDR3 中数据读出显示到显示器上。

三、设计步骤:

1.PC机到显示器之间的链路通信

首先实现从PC机到FPGA之间的链路通信(fpga到hdmi的链路在uart+ddr3+hdmi中已经实现)。

该链路分三个步骤进行:

1. 学会使用IDDR原语,打通PHY到FPGA中双沿数据到单沿数据转换。 (本章内容实现)

2.

该项目通过PC机发送图像数据到FPGA,经RGMII接口和IDDR原语处理后存储于DDR3,再由HDMI显示。介绍了RGMII协议、PHY芯片、IDDR原语的使用,以及从PHY到FPGA的双沿数据转换。涉及协议包括RGMII和UDP。

该项目通过PC机发送图像数据到FPGA,经RGMII接口和IDDR原语处理后存储于DDR3,再由HDMI显示。介绍了RGMII协议、PHY芯片、IDDR原语的使用,以及从PHY到FPGA的双沿数据转换。涉及协议包括RGMII和UDP。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?