描述

根据指示信号select的不同,对输入信号a,b实现不同的运算。输入信号a,b为8bit有符号数,当select信号为0,输出a;当select信号为1,输出b;当select信号为2,输出a+b;当select信号为3,输出a-b.

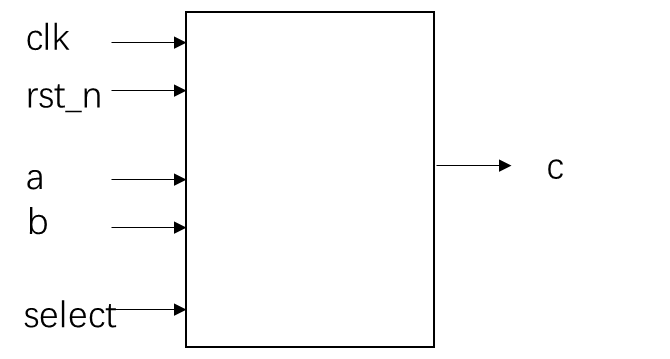

接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:复位信号,低电平有效

a,b:8bit位宽的有符号数

select:2bit位宽的无符号数

输出描述:

c:9bit位宽的有符号数

解题分析:

有符号数+有符号数=有符号数

这其中,如果加数中有无符号数,那么就会按照无符号运算。

如果表达式中有一个无符号数,则所有的操作数都会被强行转换为无符号数;

即:有符号A +无符号B时,会将补码表示的有符号A当成无符号数A1,,再计算A1+B,这样得到的结果就是错的了。

两种解决方法:

(1)涉及到有符号数运算时,和有符号相关的输入、输出、中间变量均定义成signed有符号数,这样全部遵循有符号数运算规则;

(2)用位拼接符补齐符号位;

代码如下:

方法一:

`timescale 1ns/1ns

module data_select(

input clk,

input rst_n,

input signed[7:0]a,

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

begin

c <= 0;

end

else

begin

case(select)

'd0:

begin

c <= a;

end

'd1:

begin

c <= b;

end

'd2:begin

c <= a+b;

end

'd3:begin

c <= a-b;

end

endcase

end

end

endmodule方法二:

`timescale 1ns/1ns

module data_select(

input clk,

input rst_n,

input signed[7:0]a,

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

always @ (posedge clk&nbs***bsp;negedge rst_n)

begin

if( ~rst_n ) begin

c <= 9'b0;

end

else begin

case ( select )

2'b00 : begin

c <= {a[7], a};

end

2'b01 : begin

c <= {b[7], b};

end

2'b10 : begin

c <= {a[7], a} + {b[7], b};

end

2'b11 : begin

c <= {a[7], a} - {b[7], b};

end

default : begin

c <= 9'b0;

end

endcase

end

end

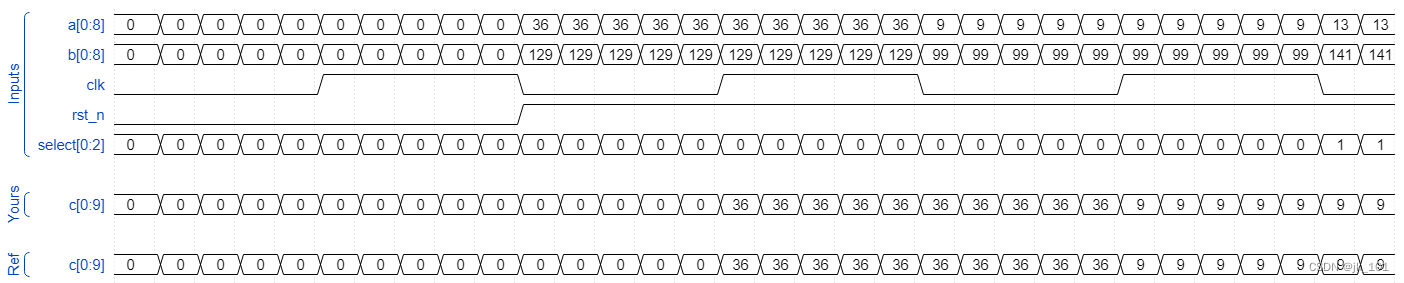

endmodule波形图:

1462

1462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?