1、实验目的

(1)学习 Quartus Prime 、Platform Designer、Nios II SBT 的基本操作;

(2)初步了解 SOPC 的开发流程,基本掌握 Nios II 软核的定制方法;

(3)掌握 Nios II 软件的开发流程,软件的基本调式方法。

2、实验设备

硬件:PC 机、DE2-115 FPGA 实验开发平台;

软件:Quartus Prime 18.1、Platform Designer、Nios II SBT

3、实验内容

使用 FPGA 资源搭建一个简单 Nios II 处理器系统,具体包括:

(1) 在 Quartus Prime 中建立一个工程;

(2) 使用 PD 建立并生成一个简单的基于 Nios II 的硬件系统;

(3) 在 Quartus Prime 工程中编译基于 Nios II 的硬件系统并生成配置文件.sof;

(4) 在 Nios II SBT 中建立对应硬件系统的用户 C/C++工程,编写一简单用户程序,在

Nios II SBT 中编译程序生成可执行文件.elf;

(5) 将配置文件.sof 和可执行文件.elf 都下载到 FPGA 进行调试运行。

4、实验原理

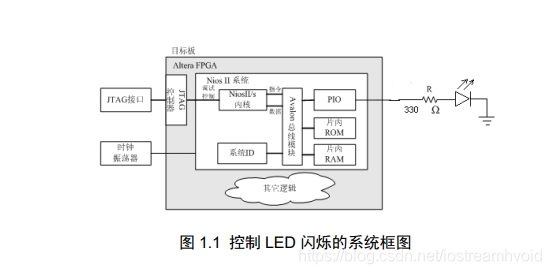

控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈

等空间使用片内 RAM,不使用任何片外存储器。整个系统的框图如图 1 所示。

从图 1.1 控制 LED 闪烁的系统框图可知,其它逻辑与 Nios II 系统一样可存在于 FPGA

中。Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。为了简单起见,本实

验在 FPGA 内不包括其它逻辑。

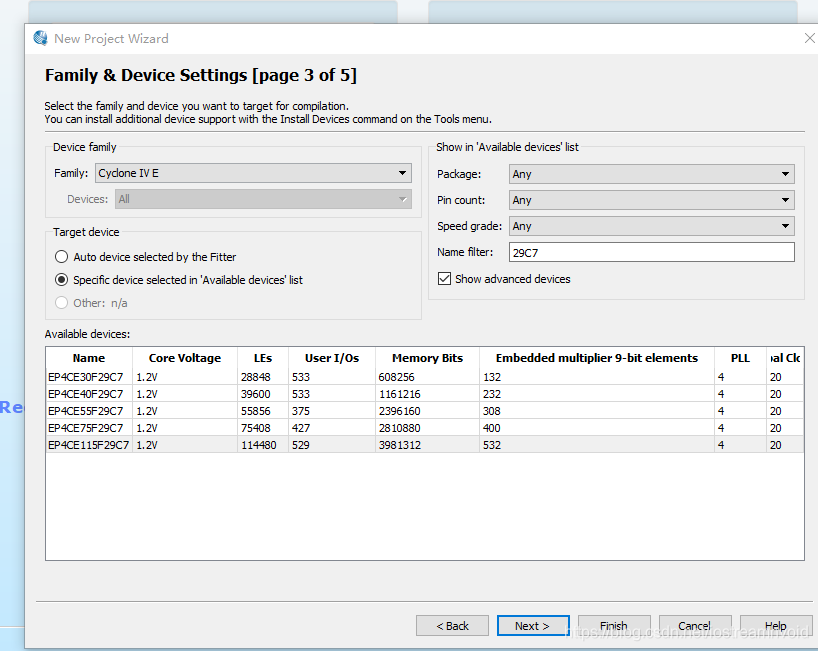

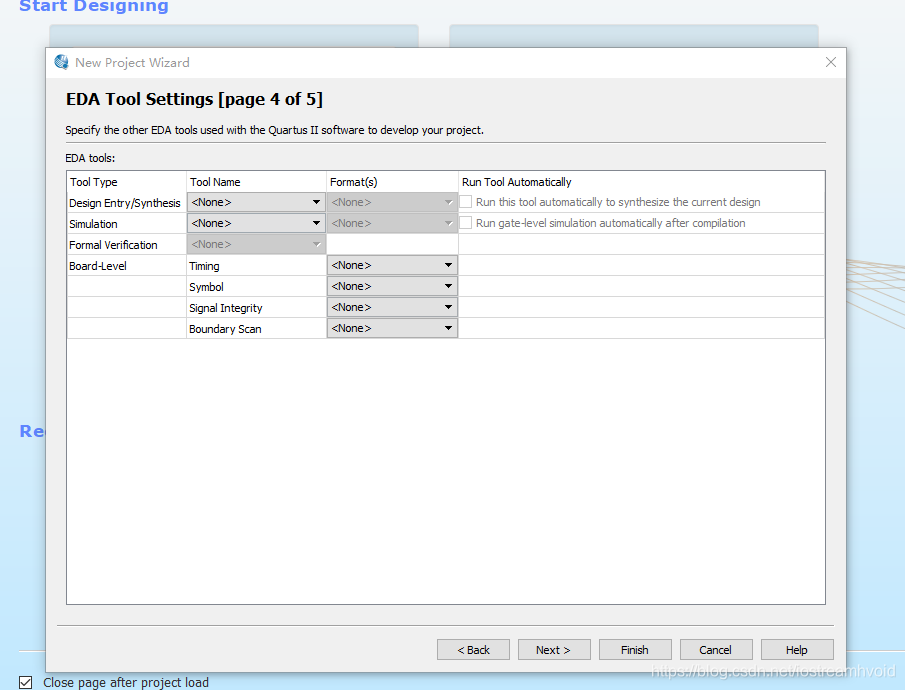

5.新建工程:

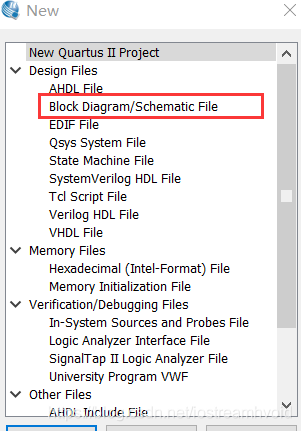

6.顶层设计:

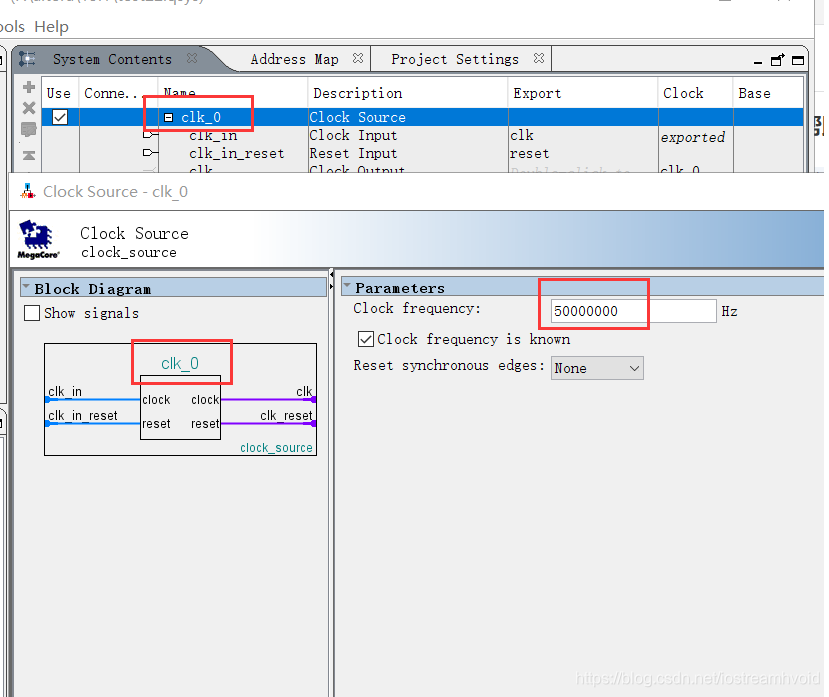

7.时钟设计:

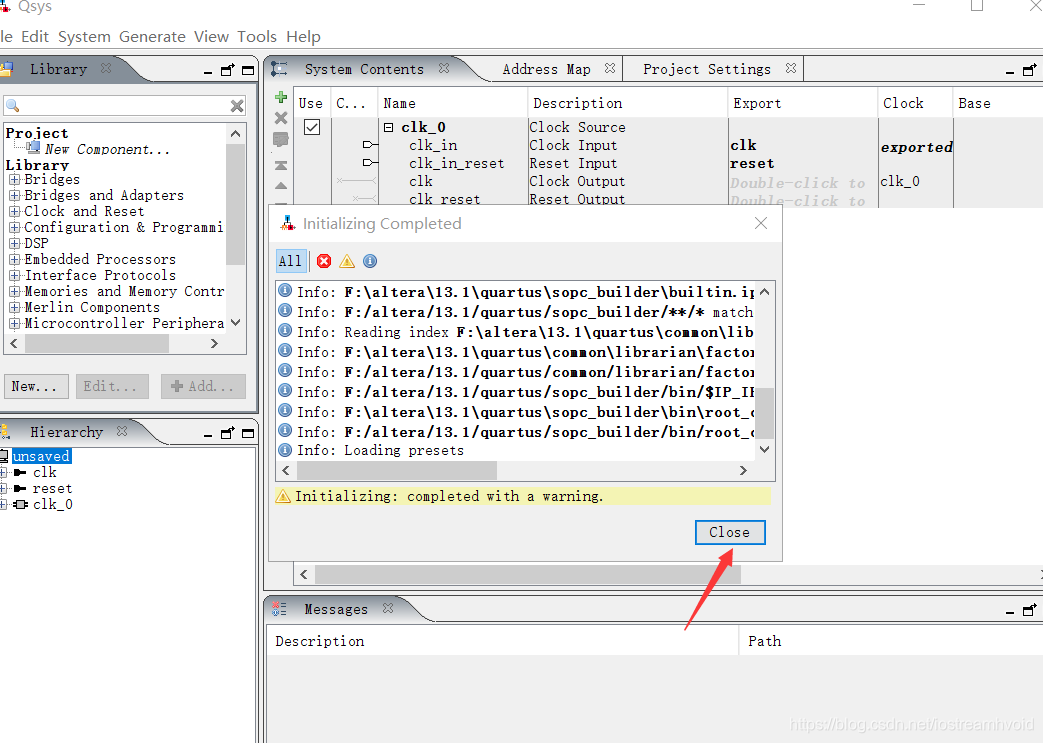

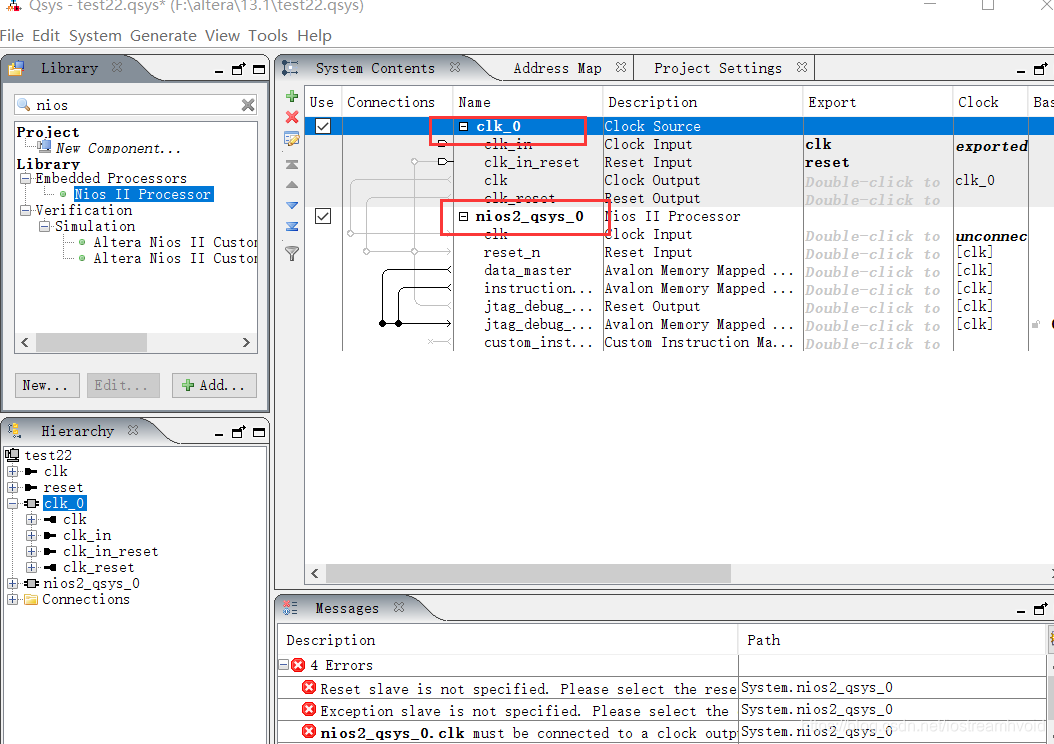

打开tool里面的Qsys设计:

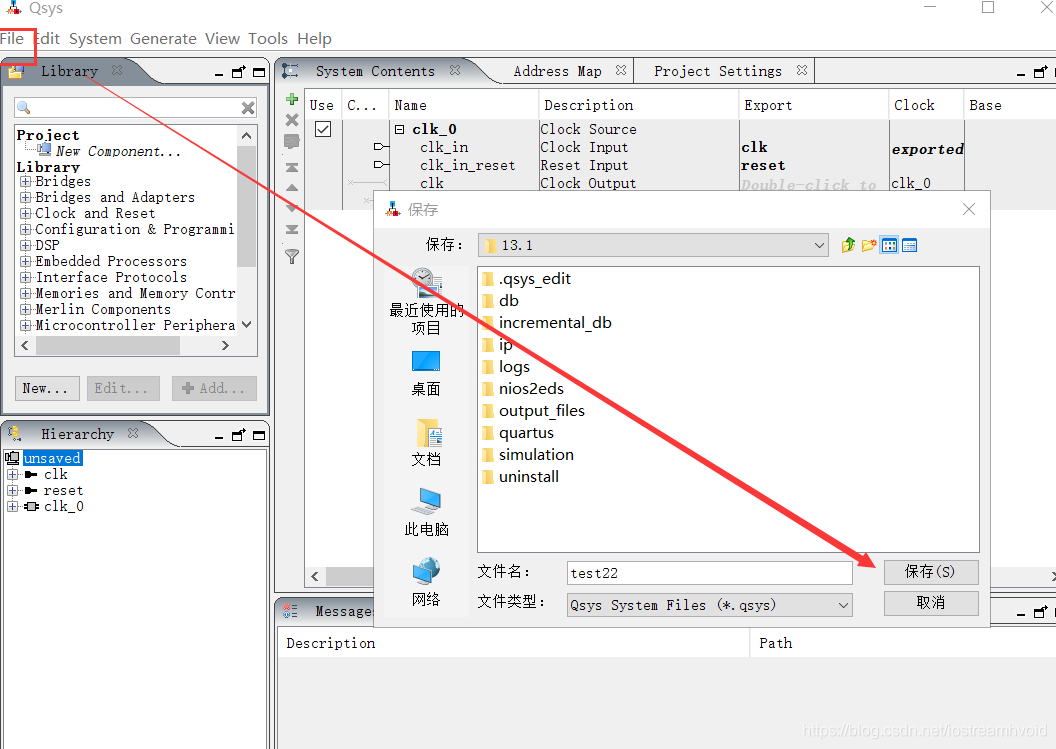

直接保存:

在library中找到时钟源:

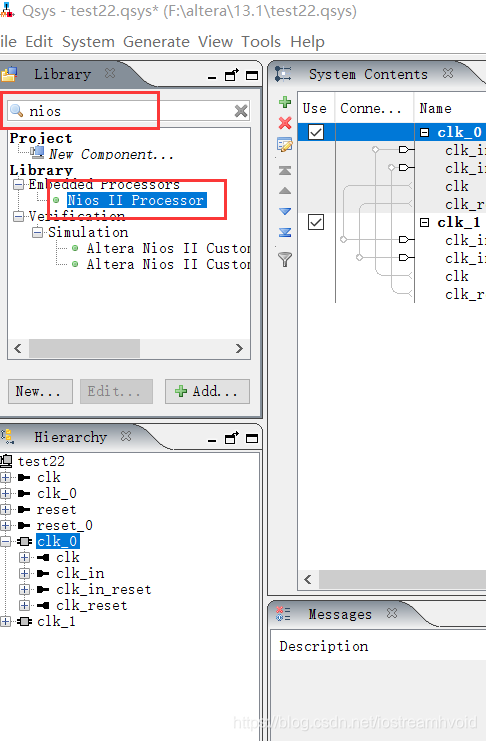

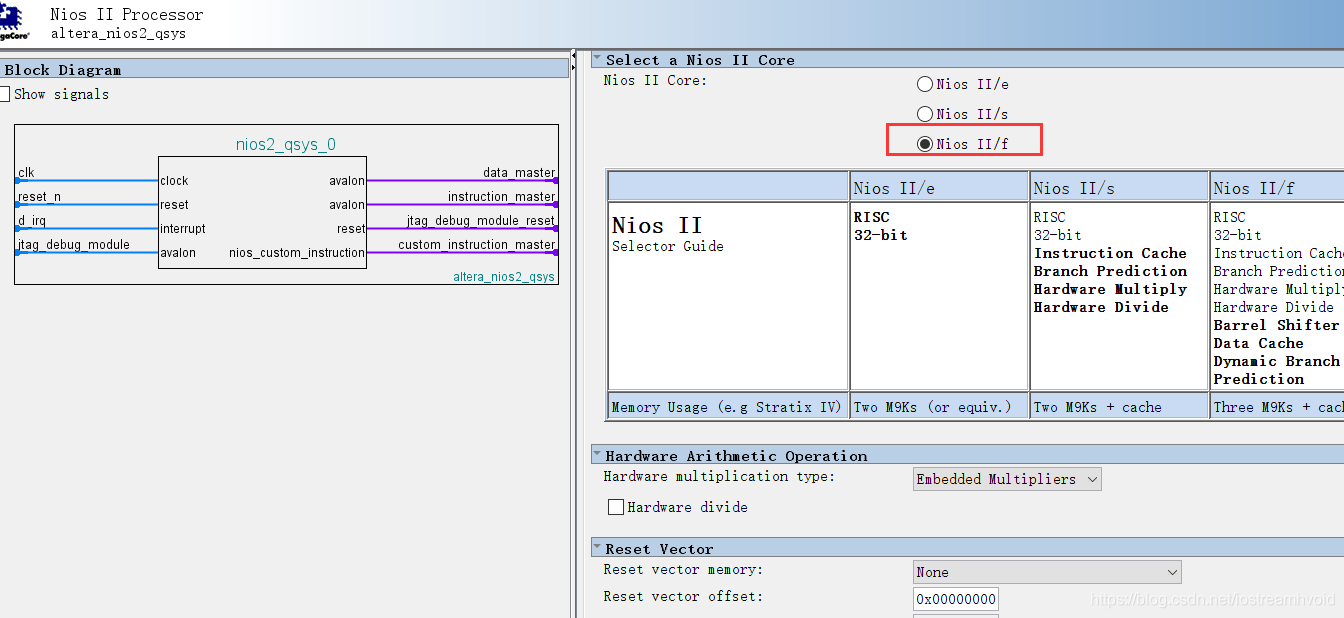

8. 添加控件:

右击之后

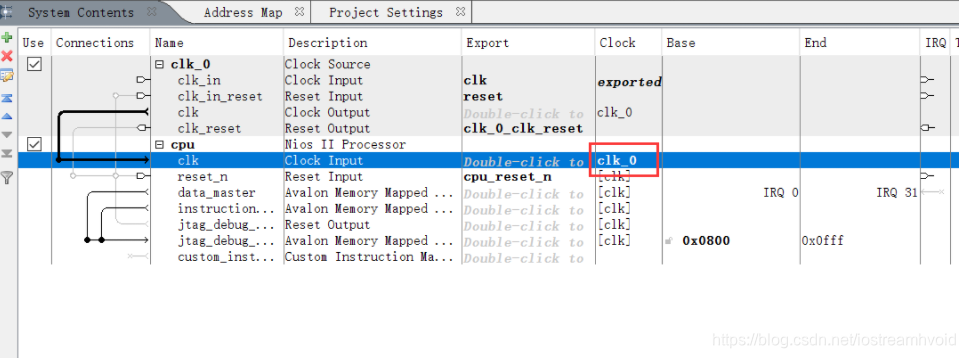

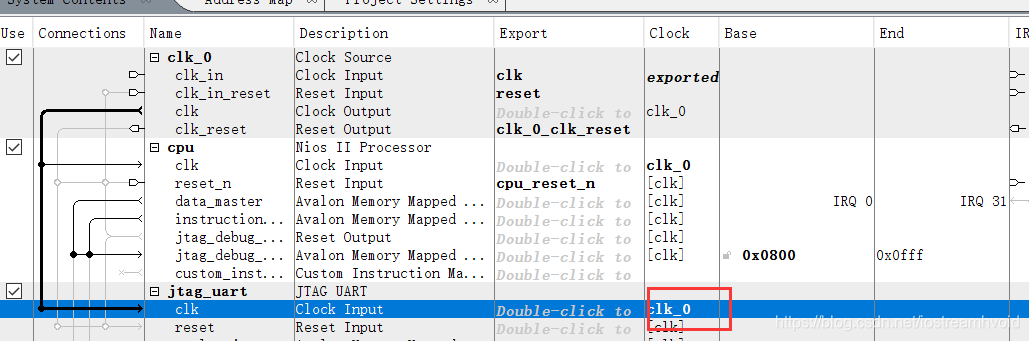

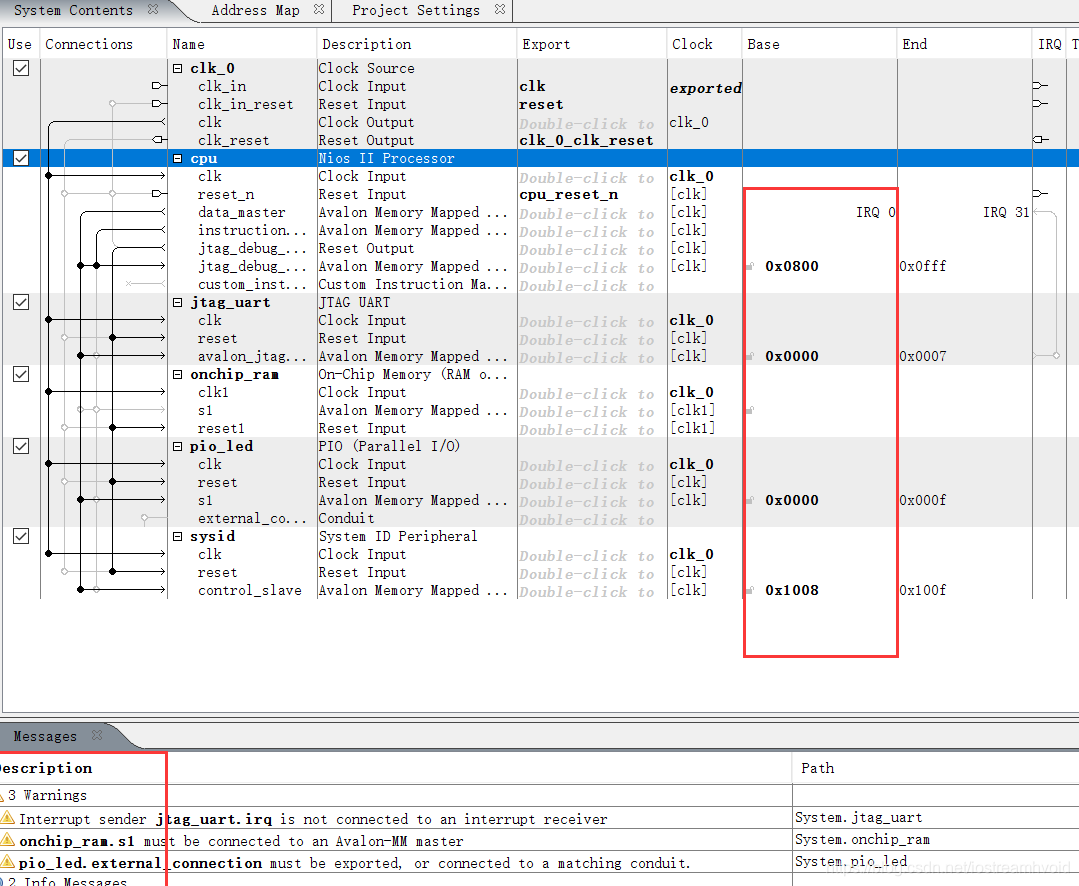

将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连:

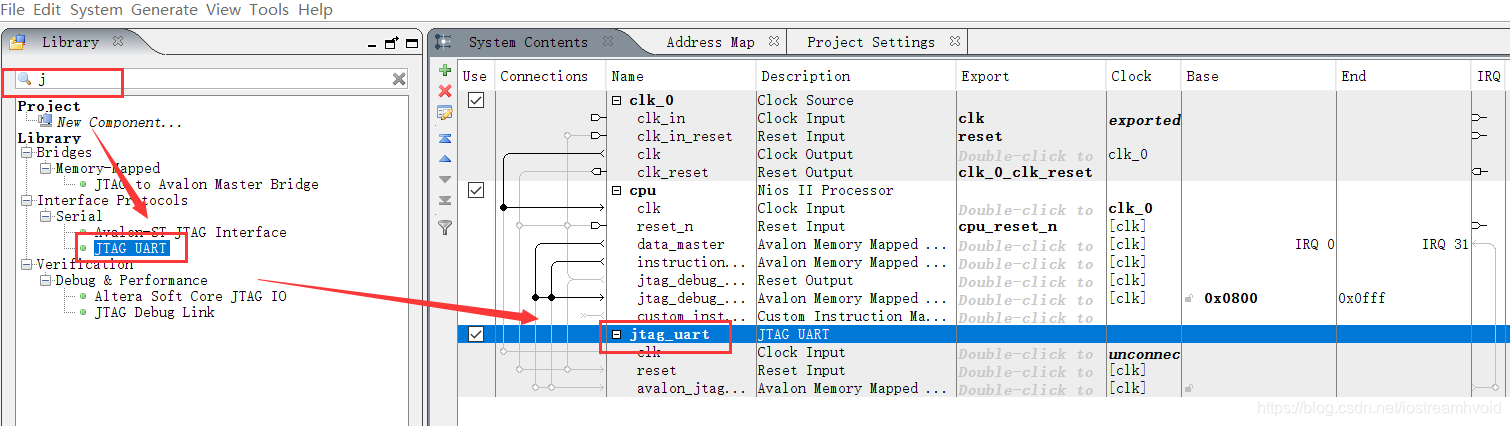

添加 jtag uart 接口:

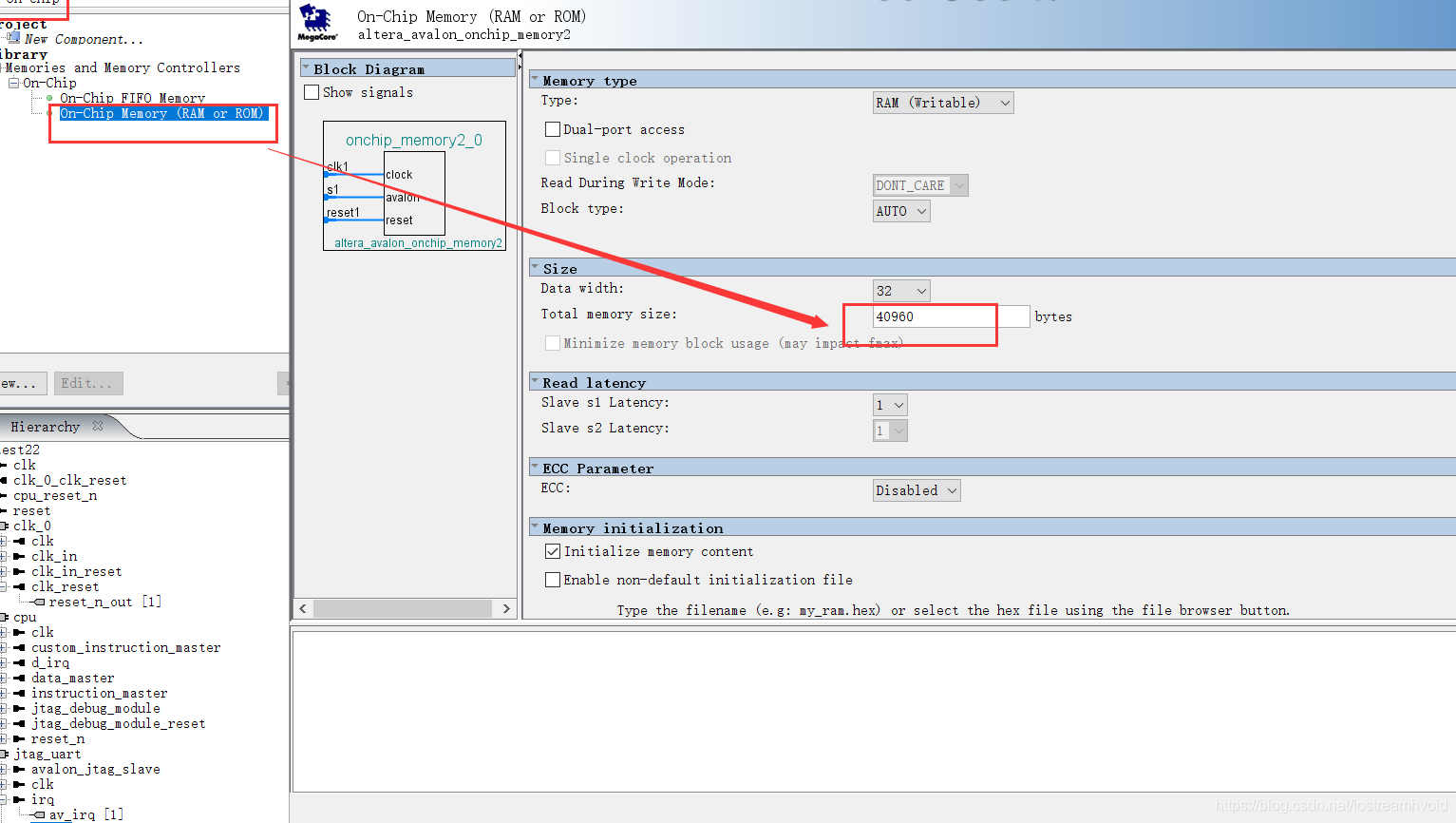

添加片上存储器

大小更改为40KB:

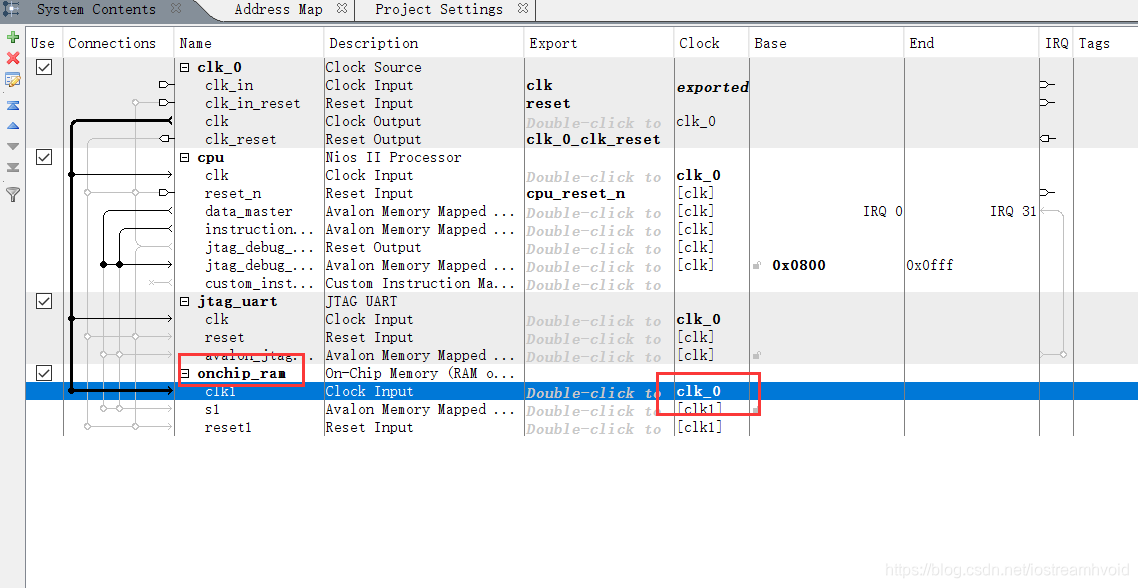

更改名称并连接:

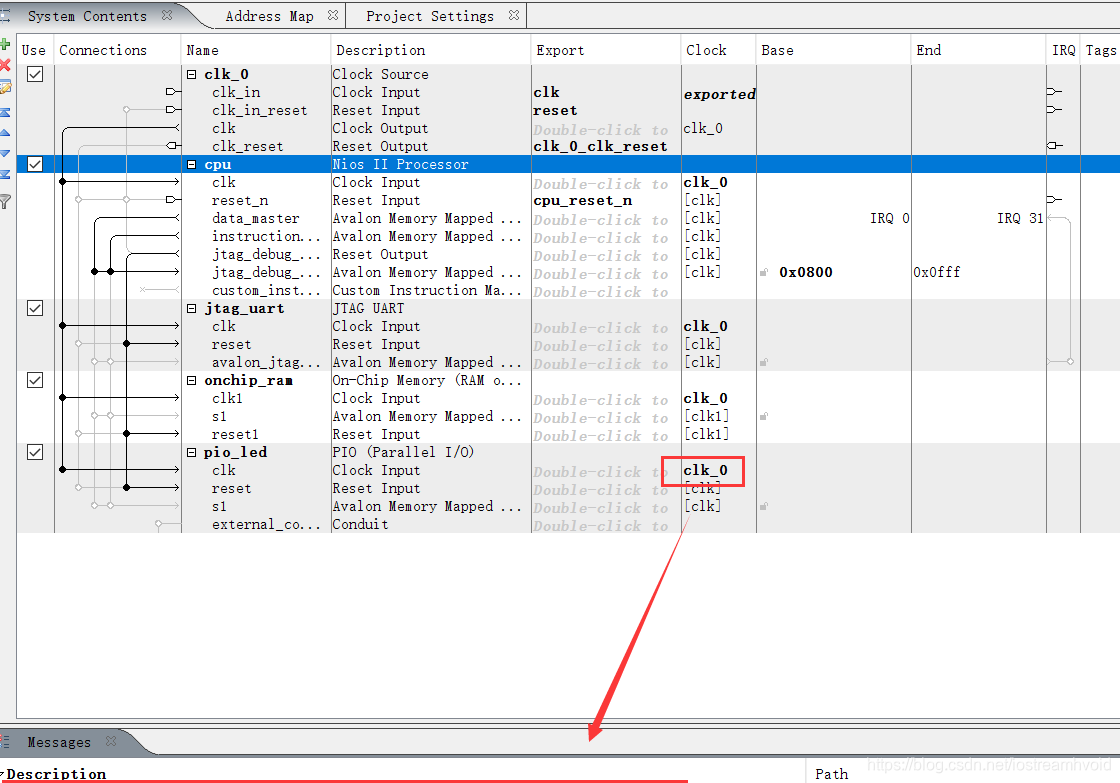

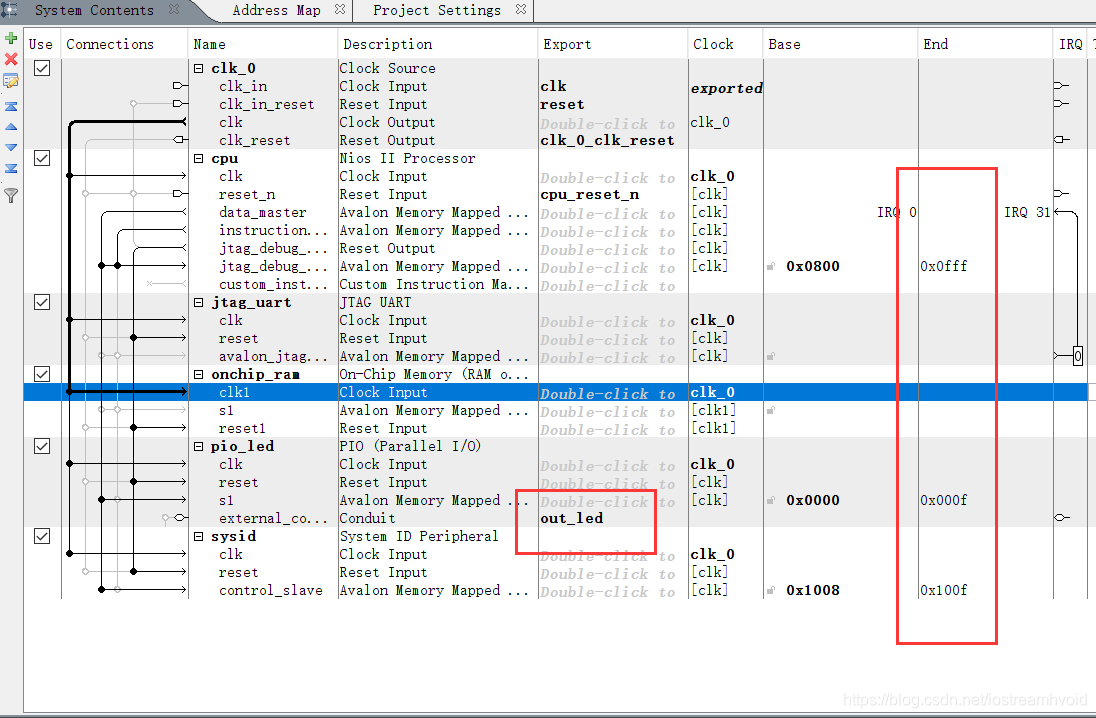

添加 PIO 接口:

添加片 System ID Peripheral 核:

9. 完成后续:

基地址分配:

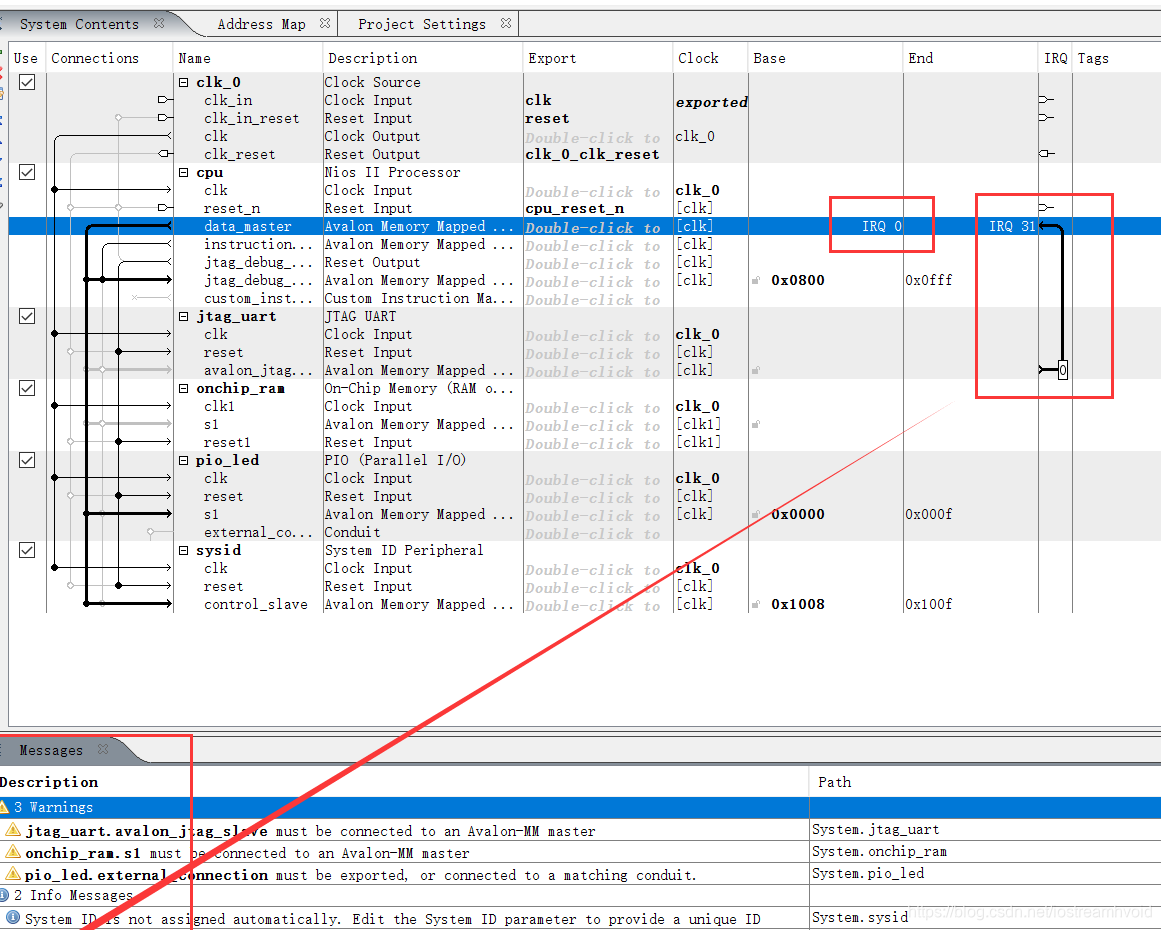

分配中断号:

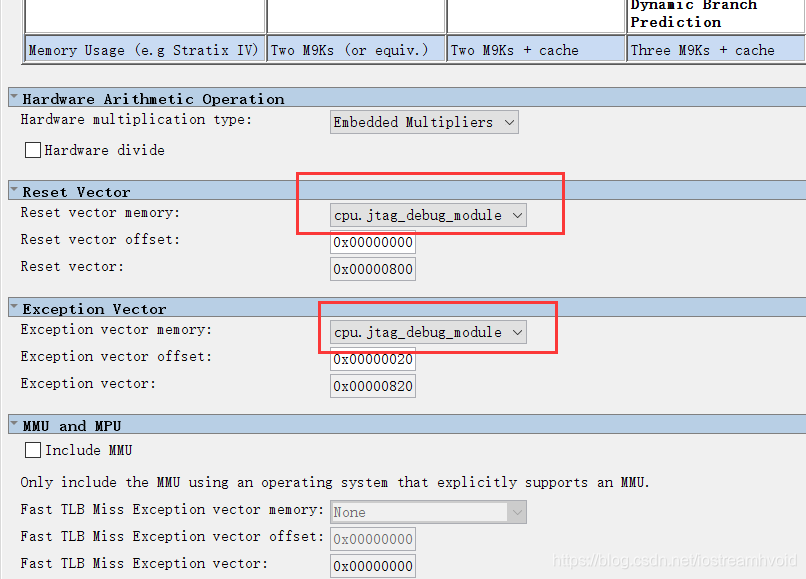

配置 Reset Vector 和 Exception Vector 为””onchip_ram.s1”:

连接所有复位端口:

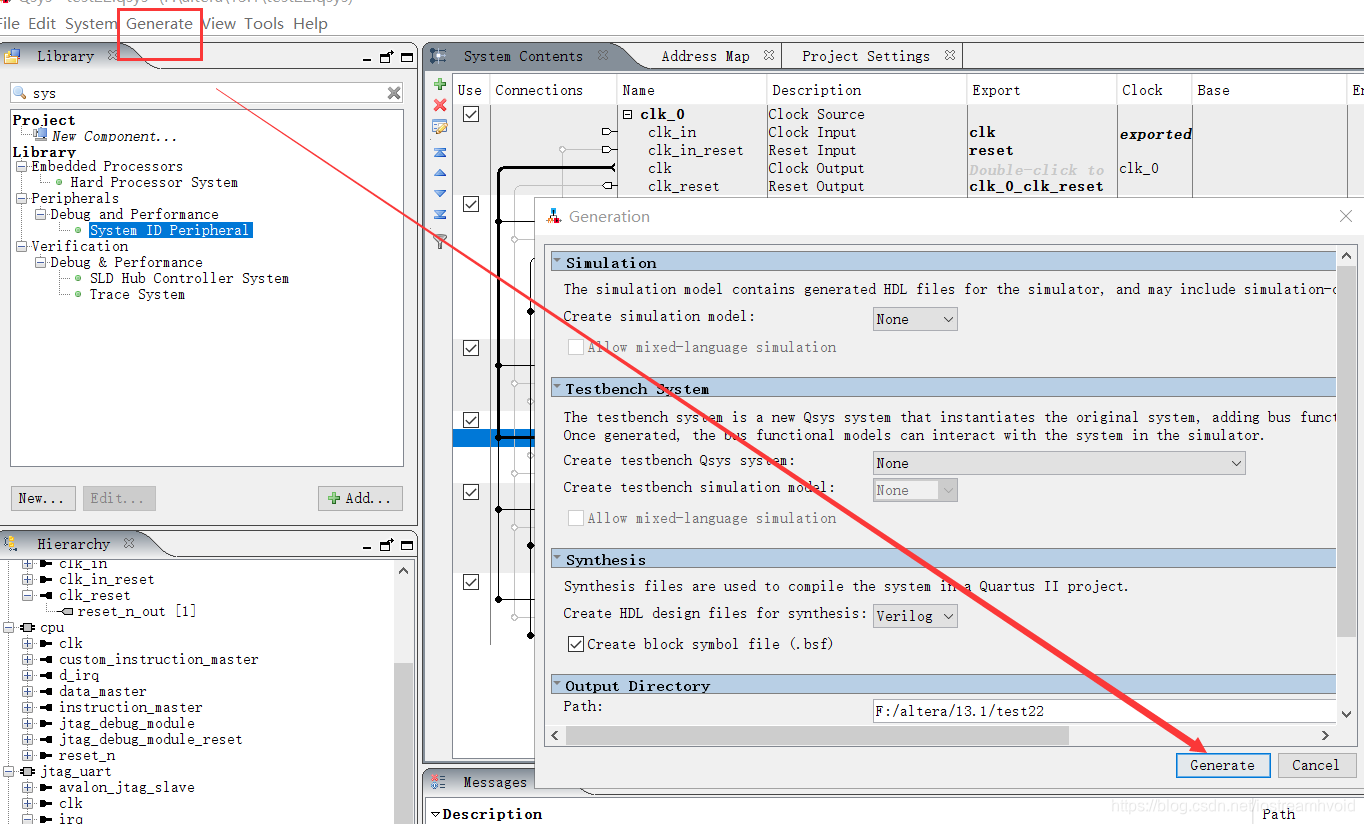

生成 Qsys 系统:

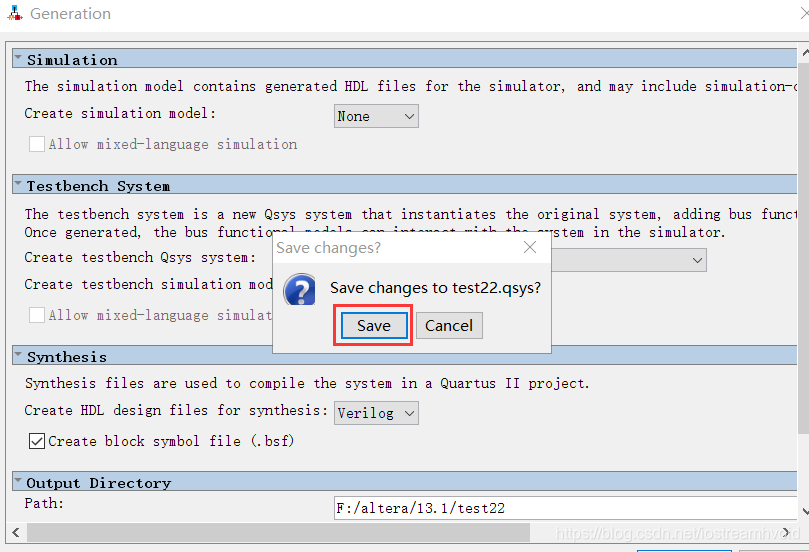

保存.qsys 文件:

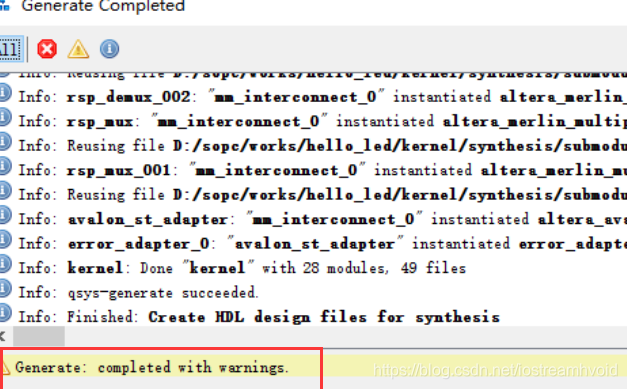

有警告无错误:

该实验介绍了如何使用Quartus Prime、Platform Designer和Nios II SBT进行FPGA开发,重点是搭建一个包含Nios II软核的简单处理器系统。实验内容包括创建工程、定制硬件系统、编写并调试用户程序,目标是学习SOPC开发流程和Nios II软核的使用。实验最后将系统和程序下载到FPGA进行运行。

该实验介绍了如何使用Quartus Prime、Platform Designer和Nios II SBT进行FPGA开发,重点是搭建一个包含Nios II软核的简单处理器系统。实验内容包括创建工程、定制硬件系统、编写并调试用户程序,目标是学习SOPC开发流程和Nios II软核的使用。实验最后将系统和程序下载到FPGA进行运行。

816

816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?