概述

在前面的课程中,讨论了用基本的触发器设计减法计数器,也提到了其缺陷,即只有脉冲输入,没有其它输入,不受控。因此,硬件工程师根据设计中常用的电路设计了163计数器,本节内容首先介绍74LS163的基本功能,然后以163为基础设计一个分频器和一个2421码模8电路(重点讲设计思路,verilog程序请自行完成)。

74LS163计数器

74LS163计数器有5个控制端、4个数据输入端和5个输出端,其逻辑功能和对应的逻辑符号如下图1和图2所示:

RCO表示进位,其语义为:当从0000~1111计满一轮,并且ENT为1时,RCO为1,其它时候均为0.

由图1,74LS163具有置位、保持、加1计数等功能,在这些功能的基础上,可以完成相对复杂的电路。

例1:以74LS163为基础设计一个6分频电路

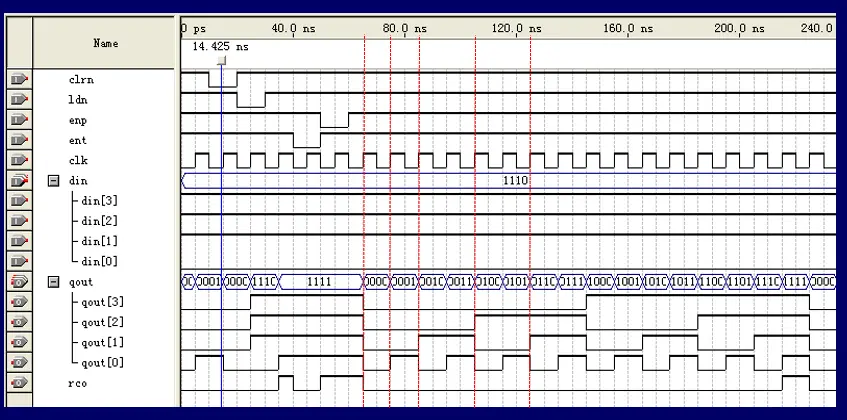

首先,需要明白什么叫分频,图3展示了分频的效果:

分频通常以CP(时钟脉冲)为基础,从图3中可以看出:qout[0]的周期为CP的2倍,qout[1]的周期为CP的4倍,qout[2]位8倍,qout[3]为16倍,显然,其频率分别为CP的1/2, 1/4, 1/8, 1/16,即所谓的2-分频,4-分频,8-分频,16-分频。

再进一步分析,对于qout[0],其变化为:当一个时钟脉冲来临时,qout[0]变化一次;对于qout[1],每两个时钟脉冲,qout[1]值变化一次;对于qout[2],每四个时钟脉冲,qout[2]值变化一次;对于qout[3],每8个时钟脉冲,qout[3]值变化一次。依次类推,如果要做6分频,显然应该是每3个时钟脉冲,值变化一次,如何用74LS163来做6-分频呢?

显然,这个问题变为:如何使74LS163中的某一位每3个时钟脉冲跳变一次。显然,只有QD和QC这两位的变化可能满足(QB每两个脉冲跳变一次,QA每个脉冲跳变一次),如果选择QC,显然可以找出一个序列:

0000 —> 0001 —> 0010 —> 1101 —> 1110 —>1111 —>0000 —> …

对于QC,先是3个0,然后是3个1,开始循环,正好是6分频。仔细观察,发现这个循环对于QD也是6分频。

针对上面分析得到的状态迁移序列,如何用74LS163来实现呢?对于前半部0000 —> 0001 —> 0010,执行的是正常的计数功能,对于后半部1101 —> 1110 —>1111( —>0000),执行的也是正常的计数功能,只有0010 —> 1101是一个跳跃,即当计数器状态为0010时,下一个状态需要用到163计数器的并行置数功能,因此,需要对163的计数器的输出进行判断,当输出为0010时,用1101对电路进行置数(确保下一时刻电路状态为1101)。

在此分析的基础上,其电路图如图4所示:

例2:2421码的模8电路

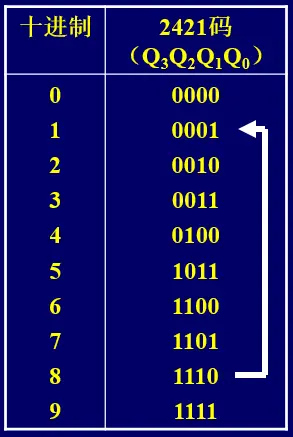

假设要求模8的状态序列如下图5所示:

在图5中,模8的状态迁移序列为:

0001 —> 0010 —> 0011 —> 0100 —> 1011 —> 1100 —> 1101 —> 1110 —> 0001 —> …

即:初始状态为0001,当状态为1110时,一轮计满并迁移到状态0001。

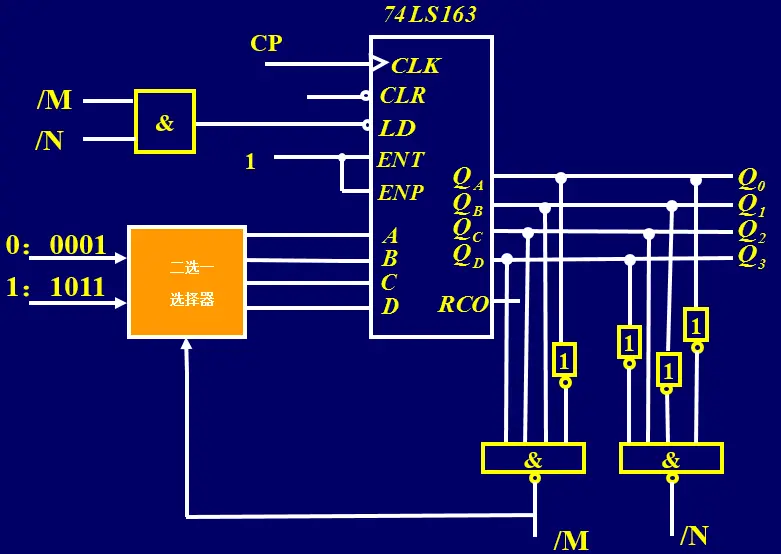

这个状态迁移序列中,需要注意的地方包括:

- 初始状态为0001,即初始时需要置位

- 序列前半部分 0001 —> 0010 —> 0011 —> 0100和序列后半部分1011 —> 1100 —> 1101 —> 1110执行的是正常的计数功能

- 0100 —> 1011有状态跳跃,在到达状态0100时,需要置数;1110 —> 0001,即记录一轮满时,需要置数

从上面的分析中得知,这个电路中存在两次置数,一次为初始状态的置数,另一个则为0100 —> 1011状态迁移时的置数,并且两次需要置的数值是不一样的,其它情况正常计数。因此,置数的时候需要作二选一,即从两个数中选择一个置数,需要一个二选一的选择器;另外,还要确定置数的时机,显然,当状态为1110时,需要置数为0001,当状态为0100时,需要置数为1011。

由上分析可知,其对应的电路图如图6所示:

小结

上面两个例子都是相对较难的例子,需要综合前面学习的组合电路,要求对组合电路和时序电路的基本功能非常熟悉。其基本思路相对而言,比较明晰,把需要跳转的状态找出来,然后需要置位的状态进行相应的设置即可。

如有错误,请各位批评指正!谢谢!

本文介绍了74LS163计数器的功能,通过实例详细讲解如何利用74LS163设计6分频电路和2421码的模8电路,强调了计数器状态迁移和并行置数在电路设计中的关键作用。

本文介绍了74LS163计数器的功能,通过实例详细讲解如何利用74LS163设计6分频电路和2421码的模8电路,强调了计数器状态迁移和并行置数在电路设计中的关键作用。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?