TLB与Cache访问谁先访问?

1 Cache与TLB简介

Cache与TLB本质上都是利用数据访问的局部性原理,就是把最常用的数据放在最快可以访问的地方。具体而言,Cache是用于缓存CPU常用的数据和指令的,分别称为dcache(data cache)和icache(instruction cache)。Cache通常有多级,比如L1 Cache、L2 Cache和L3 Cache,只有L1 Cache中是将指令和数据分开存放的,L2/L3 Cache中指令和数据通常是混合存放的。TLB(Translation Lookaside Buffer)是用于缓存虚拟地址到物理地址的映射关系的,通常位于MMU中。在操作系统中,进程使用的虚拟地址需要转换成物理地址才能得到数据在物理内存中的真正存放位置,而内存管理单元MMU的一个功能就是进行虚拟地址到物理地址的转换。注意:多个虚拟地址可能会对应同一个物理地址。通常来说,CPU发出的数据访问请求都是虚拟地址的,那CPU发出的数据请求是先到Cache中查找有无该虚拟地址对应的数据还是先利用MMU进行虚拟地址到物理地址转换然后再查找Cache呢?。

2 Cache与TLB谁先访问?

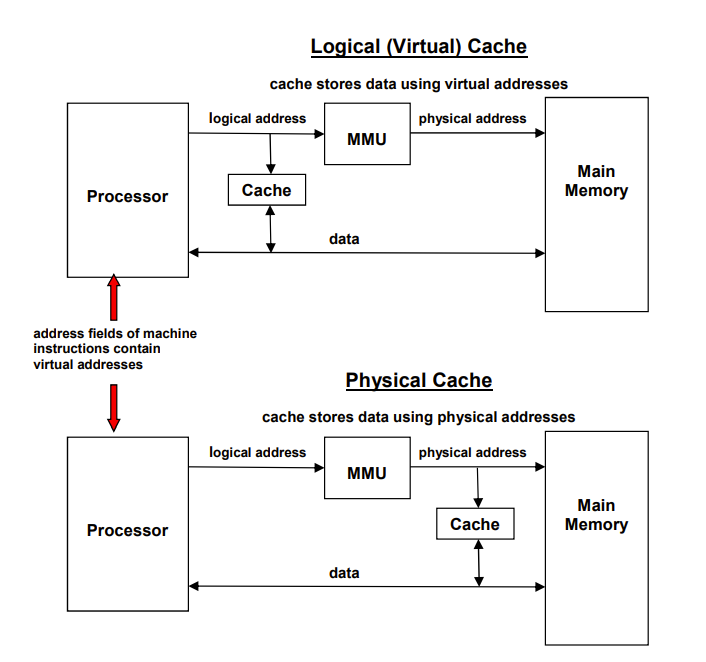

答案是上述2种情况都有可能,这取决于TLB与Cache的先后顺序。如果TLB介于 CPU 和 Cache之间,其实就是MMU介于CPU和Cache之间,则是先访问TLB后访问Cache且此时访问Cache使用的是物理地址,这种情况称为物理Cache。如果TLB介于 Cache和Memory之间,即MMU介于Cache与Memory之间,则是先访问Cache后访问TLB且此时访问Cache使用的是虚拟地址,这种情况称为逻辑Cache(注意:实际上此时可以同时向Cache发出请求,如果Cache命中则最好,如果Cache未命中此时MMU可以进行地址转换以便于Cache未命中后的从内存中获取数据)。具体示意如下图:

物理Cache与逻辑Cache各有优缺点。对于逻辑Cache:(1)CPU可以更快得知数据是否被cache,因为不需要等待MMU进行虚拟地址到物理地址的转换。(2)一方面,由于不同进程之间会存在相同的虚拟地址。另一方面,不同的虚拟地址可能会对应相同的物理地址。因此,逻辑Cache在进行进程上下文切换时需要flush cache或者通过在每一个cache line中添加额外的位来区分各个进程或者物理地址对应的Cache。对于物理Cache:(1)CPU获取被Cache缓存的数据速度更慢,因为需要先利用MMU进行虚拟地址到物理地址的转换,然后才查找cache。(2)每一个cache line的位数可以更少,因为物理地址是唯一的,不像虚拟地址那样会出现重复,而且在进程上下文切换时也不必flush cache。

本文介绍了Cache与TLB的基本概念及其在内存访问中的作用。讲解了Cache与TLB的访问顺序,指出物理Cache是先访问TLB后访问Cache,逻辑Cache则是先访问Cache后访问TLB。并分析了两种方式的优缺点,物理Cache虽慢但避免了上下文切换时的flush操作,逻辑Cache快但需处理虚拟地址冲突。

本文介绍了Cache与TLB的基本概念及其在内存访问中的作用。讲解了Cache与TLB的访问顺序,指出物理Cache是先访问TLB后访问Cache,逻辑Cache则是先访问Cache后访问TLB。并分析了两种方式的优缺点,物理Cache虽慢但避免了上下文切换时的flush操作,逻辑Cache快但需处理虚拟地址冲突。

2412

2412