在内存技术不断进步的今天,DDR4带来了许多创新功能,其中Per DRAM Addressability,简称PDA,是一项非常实用却鲜为人知的技术。这项技术解决了之前DDR内存无法单独编程各个DRAM芯片的限制,下面我来聊聊这个功能的细节。

传统模式寄存器编程的问题

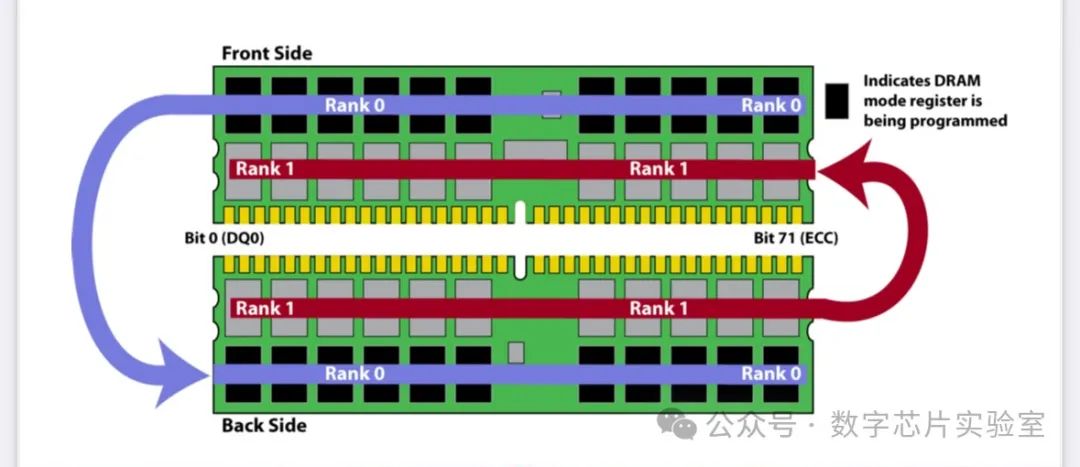

在DDR3及更早的内存中,当我们需要设置内存参数时,会使用"模式寄存器设置"(MRS)命令。这个命令会同时影响一个内存条上所有的DRAM芯片。举个例子,当我们设置DDR3的某个参数时,比如设置CWL为7个时钟周期,整个内存条上的所有18个DRAM芯片都会被完全相同地编程,没有例外。

这种方式简单直接,但缺少灵活性。有时候我们可能需要对不同DRAM进行不同设置,尤其是当ECC内存芯片需要特殊配置时。

DDR4的解决方案:Per DRAM Addressability

DDR4通过一个巧妙的方法解决了这个问题。它利用每个DRAM的数据线DQ[0]和对应的时钟线,让host可以单独选择要编程的DRAM芯片。

这个过程分三步走:

- 首先,把所有DRAM芯片置于PDA模式(类似DDR3的MRS功能)

- 然后,通过数据线上的特定编码,选择性地编程特定DRAM位置

- 最后,退出PDA模式

实际操作案例

假设我们想对内存条上的ECC校验位DRAM进行特殊设置:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

707

707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?