控制器主要功能

- 支持 NAND flash memory型号:Samsung, 128Mx8 (K9F1G08R0A, 1.8V)

- 支持如下命令:

Erase (block)

Program Page (copy internal page buffer into flash memory)

Read Page (a flash page into internal buffer).

- 为了实现高数据可靠性,将在编程期间使用 ECC(汉明码) - 在备用页面区域写入 ECC 字节,并读取操作 - 计算页面 (2048 B) 上每个扇区 (512 B) 的传入数据的 ECC,纠正单个错误 并检测双重错误)

- 提供用于在同一 FPGA 上使用的简单主机接口

- 提供两个双端口 RAM 缓冲区(位于 FPGA Block RAM 中),以便主机为将来的传输准备一个缓冲区,而控制器可以使用另一个缓冲区进行当前与闪存之间的传输

- 创建一个紧凑的实现,可以多次实例化,以便在同一 FPGA 设备上提供多个 NAND 闪存接口

擦除操作

时序图

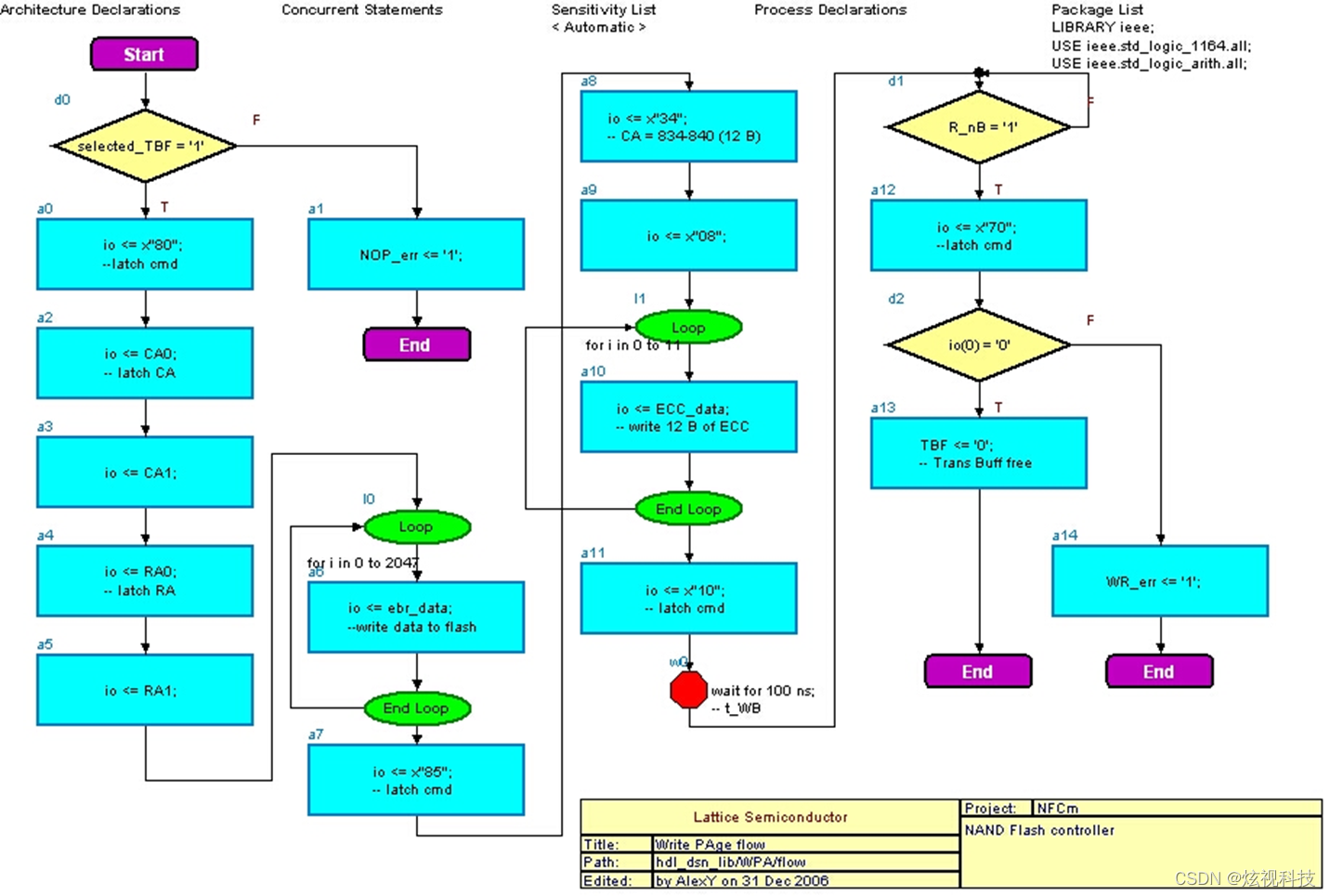

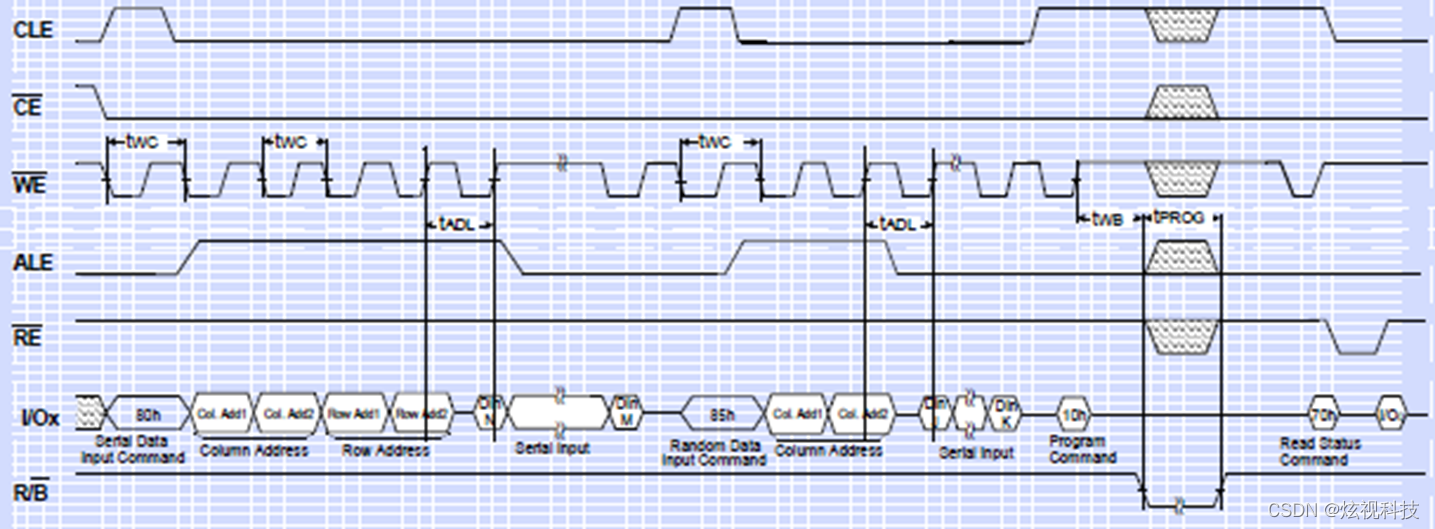

页编程

时序图

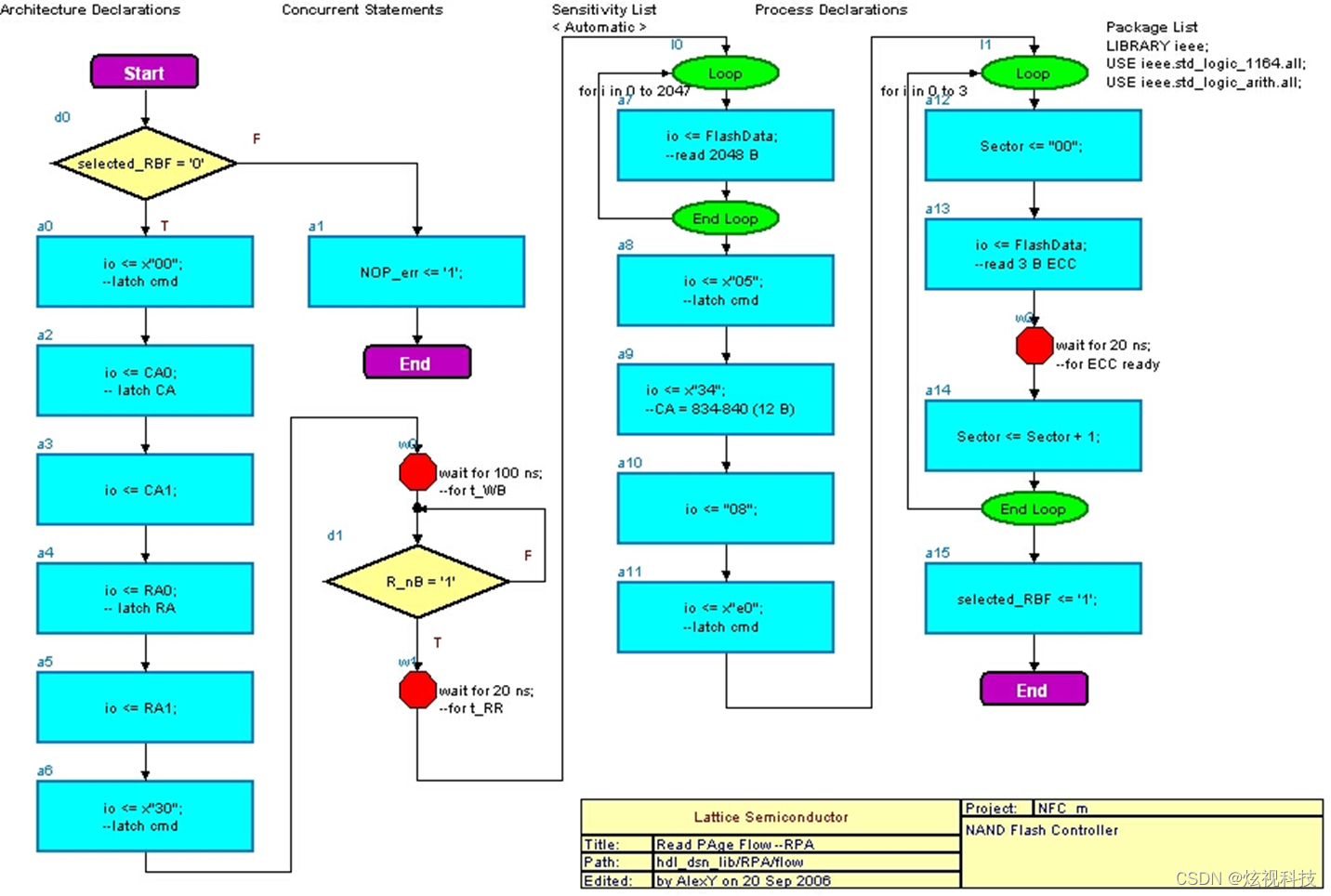

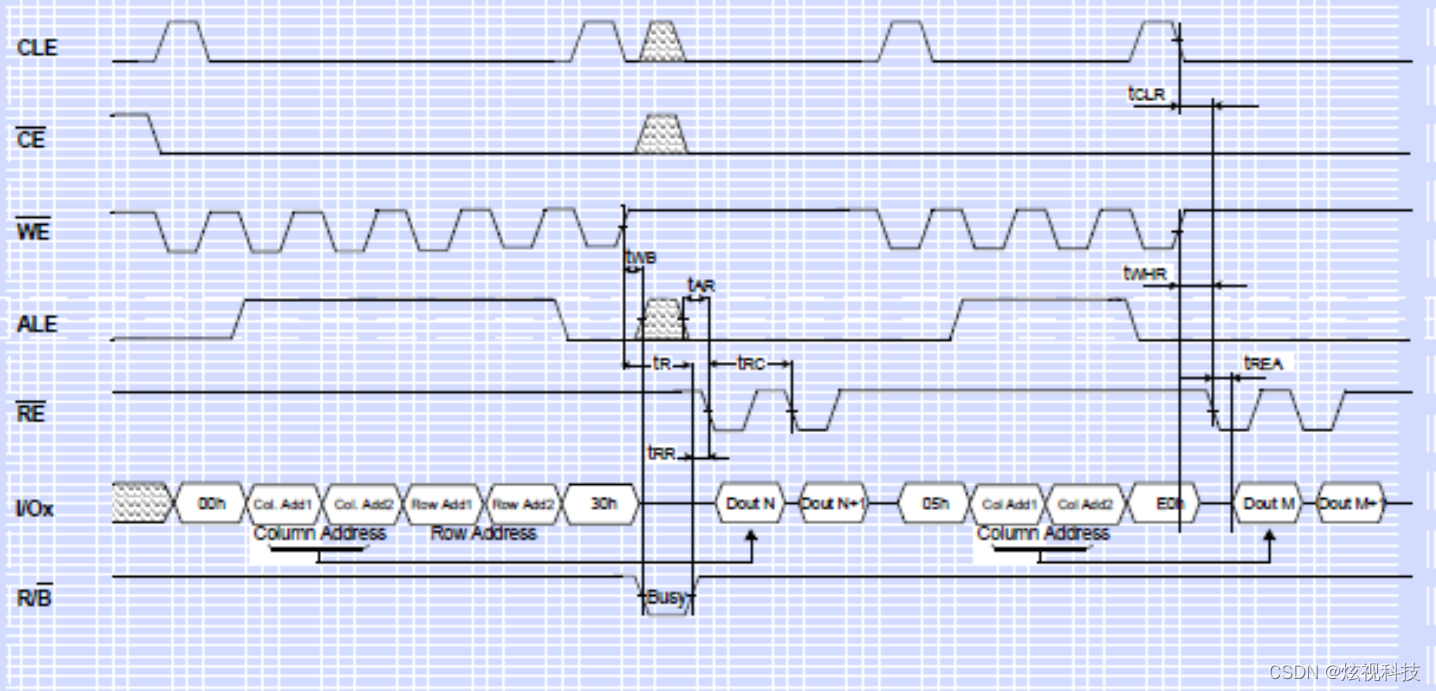

页读取模式

时序图

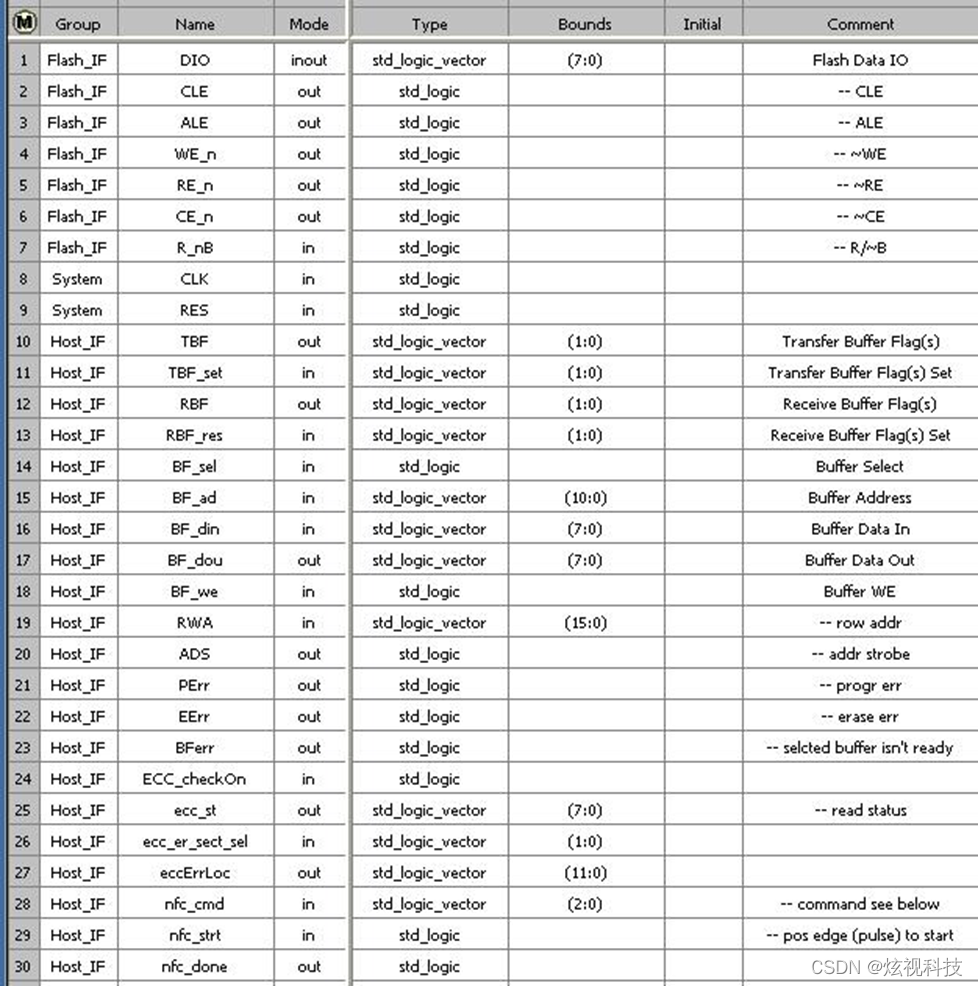

顶层接口设计

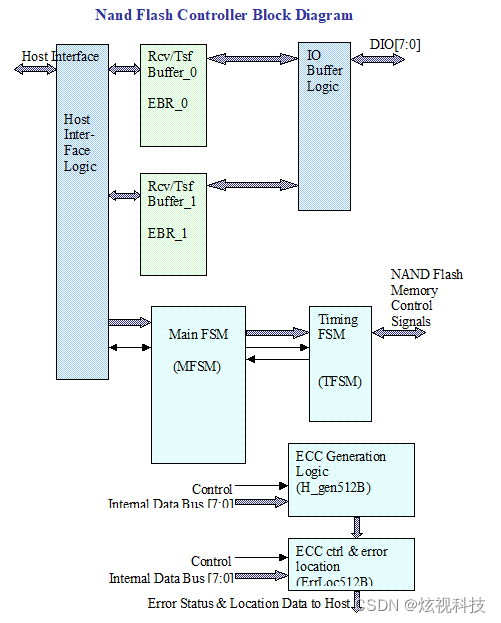

模块设计图

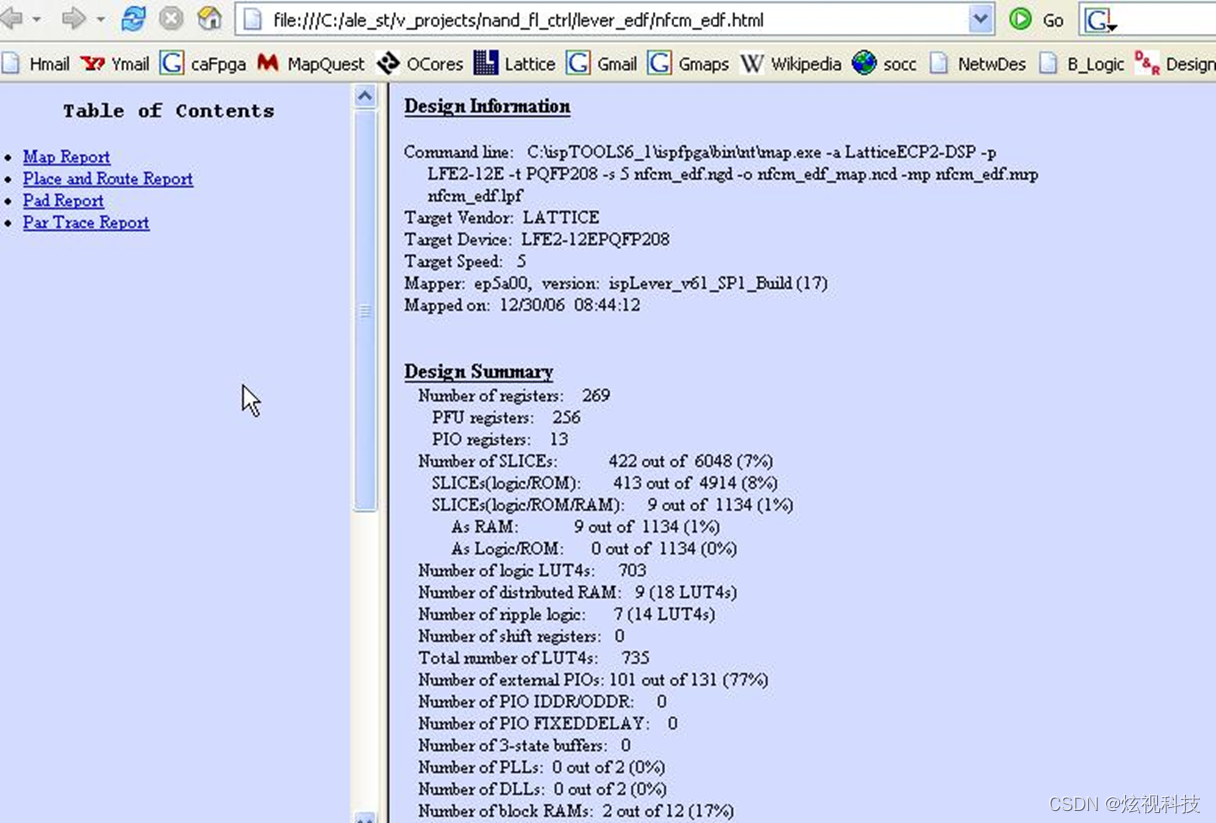

资源消耗

本文详细介绍了如何使用FPGA实现NAND flash控制器,支持Samsung 128Mx8 K9F1G08R0A型号,包含擦除、编程和读取操作。为了保证数据可靠性,采用ECC(汉明码)并在编程和读取过程中进行错误检查和校正。设计还包括了双端口RAM缓存和紧凑的顶层接口,适于在同一FPGA上实现多个NAND闪存接口。

本文详细介绍了如何使用FPGA实现NAND flash控制器,支持Samsung 128Mx8 K9F1G08R0A型号,包含擦除、编程和读取操作。为了保证数据可靠性,采用ECC(汉明码)并在编程和读取过程中进行错误检查和校正。设计还包括了双端口RAM缓存和紧凑的顶层接口,适于在同一FPGA上实现多个NAND闪存接口。

1234

1234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?