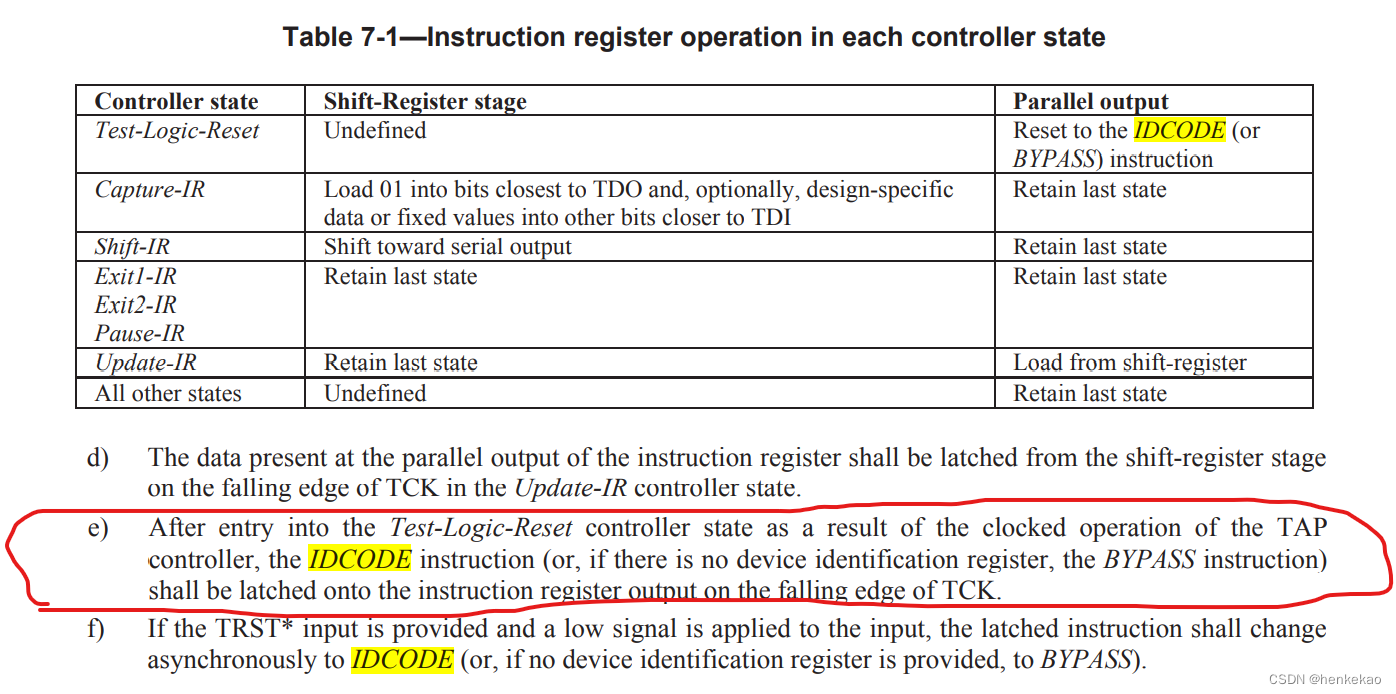

1. 在Test-logic-Reset状态时,需要在TCK的下降沿讲指令寄存器复位到IDCODE或者BYPASS

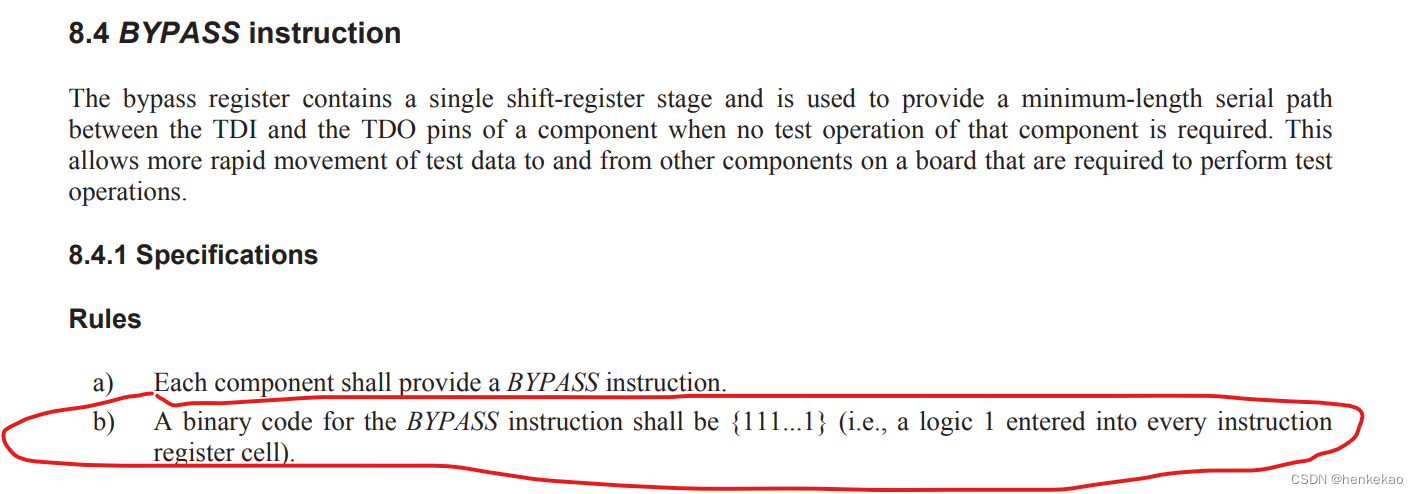

2. bypass指令必须是全1

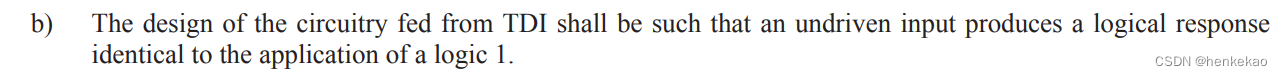

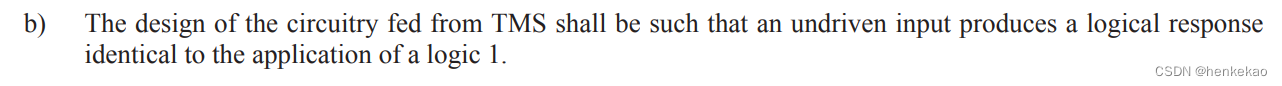

3. TDI的默认值应该为1(保证内部指令可能是bypass),TMS默认值应该是1(让状态机保持在test-logic-reset)

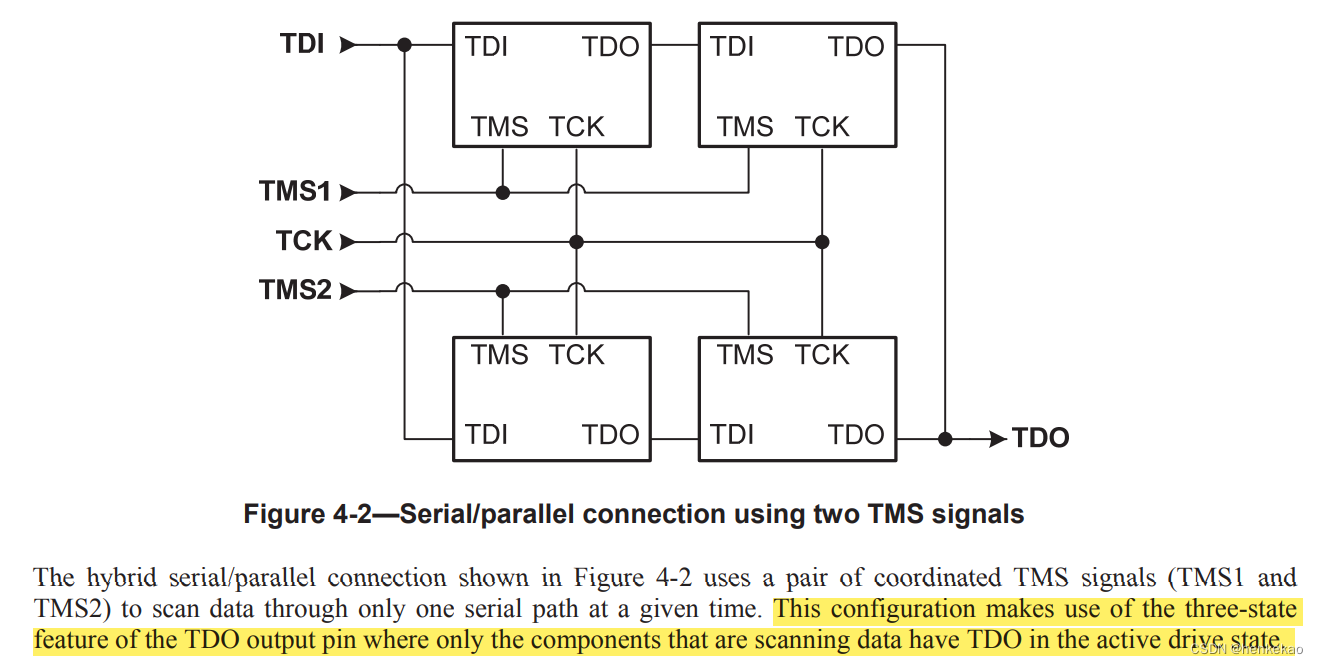

4. TDO在shift-i/dr状态外都是high-z

是high-z的原因是会有下述的拓扑结构,TDO会有分时复用的情况,所以必须是high-z

5. Host(例如Trace 32)输出的TCK需要尽可能的保证duty cycle为50%,因为芯片内部的TDO是在TCK的下降沿驱动的,所以TDO的setup time比较紧。如果TCK的duty cycle低电平占空比较小,就容易在频率较高时导致Host在TCK上升沿采样到的是TDO跳变前的值。

6. update DR寄存器需要状态为update-DR,在TCK的下沿将shift-DR的值更新

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?