简述

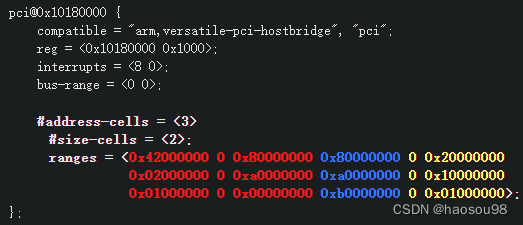

如上图定义了pcie三组地址转换关系,每一组的几个数字分别定义了属性(32bit),pci地址空间(64bit),cpu地址(32bit/64bit),长度(64bit)

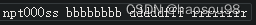

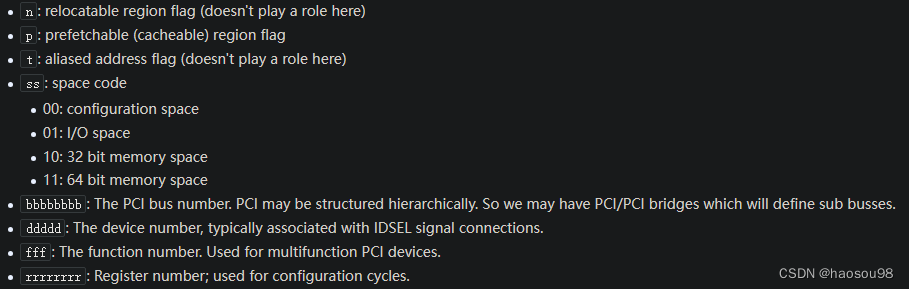

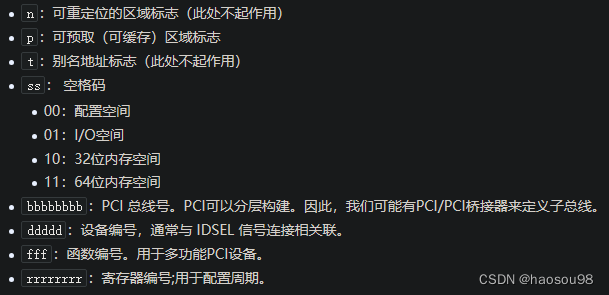

属性的含义

设备树之中三组地址映射的解释

- 从 PCI 地址0x80000000开始的 32 位可预取内存区域,大小为 512 MB,将映射到主机 CPU 上的地址0x80000000。

- 从 256 MB 大小的 PCI 地址0xa0000000开始的 32 位不可预取内存区域,将映射到主机 CPU 上的地址0xa0000000。

- 从 PCI 地址0x00000000开始的 I/O 区域大小为 16 MB,将映射到主机 CPU 上的地址0xb0000000。

本文解析了PCIExpress(PCIe)中的地址转换机制,包括预取和非预取内存区域以及I/O区域的映射,分别对应于PCI地址空间、CPU地址和大小。详尽介绍了从PCI地址0x80000000到0xa0000000和0x00000000到0xb0000000的映射规则,来源自elinux.org。

本文解析了PCIExpress(PCIe)中的地址转换机制,包括预取和非预取内存区域以及I/O区域的映射,分别对应于PCI地址空间、CPU地址和大小。详尽介绍了从PCI地址0x80000000到0xa0000000和0x00000000到0xb0000000的映射规则,来源自elinux.org。

5118

5118