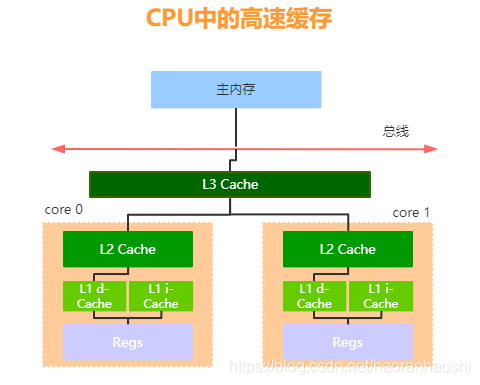

CPU结构

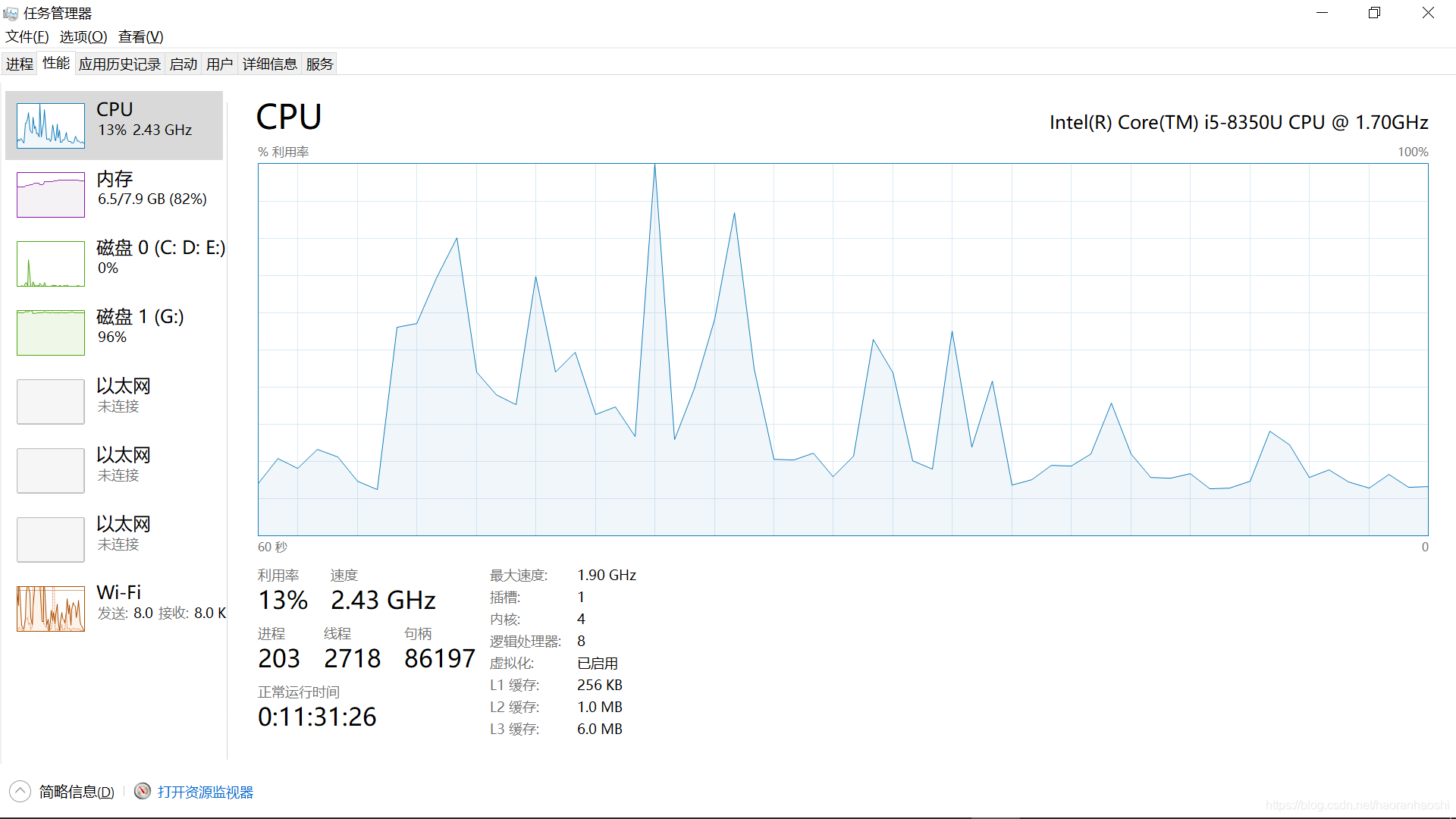

任务管理器CPU部分右下中会展示高速缓存(L1、L2、L3):

一级缓存(Level 1 Cache)为一级数据缓存(Data Cache,D-Cache,L1 d-Cache)和一级指令缓存(Instruction Cache,I-Cache,L1 i-Cache)。

L1、L2、L3参考:为什么CPU缓存会分为一级缓存L1、L2、L3?有什么意义?

总线探测

总线层面解决数据一致性问题。

涉及共享的变量存储的时候,总线会探测到,加锁,禁止其他线程读取,变量值写入到主内存变量后,才会解锁,允许其他线程读取。会锁住有此变量的其他线程的整个缓存,而不是缓存行,不利于其他线程处理效率,所以有了缓存一致

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1255

1255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?