今天是内存问题案例第2篇:内存走线拓扑问题。

01 问题描述

某主板使用DDR3表贴颗粒,X8颗粒正反贴,含ECC,TOP/BOTTOM面各9颗颗粒,每通道共18颗颗粒。实际测试发现内存速率只能到400Mbps,而另一个项目的单板内存速率可以到677Mbps。

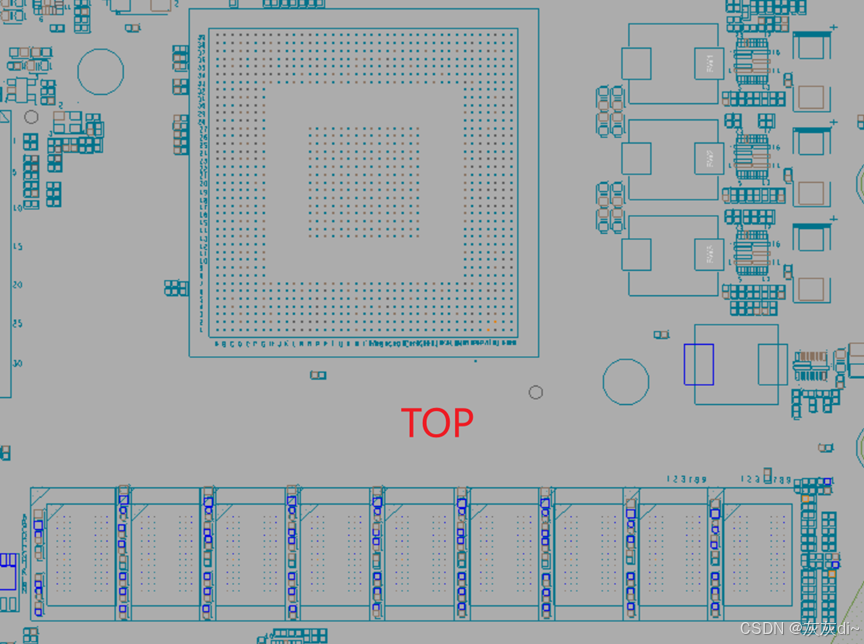

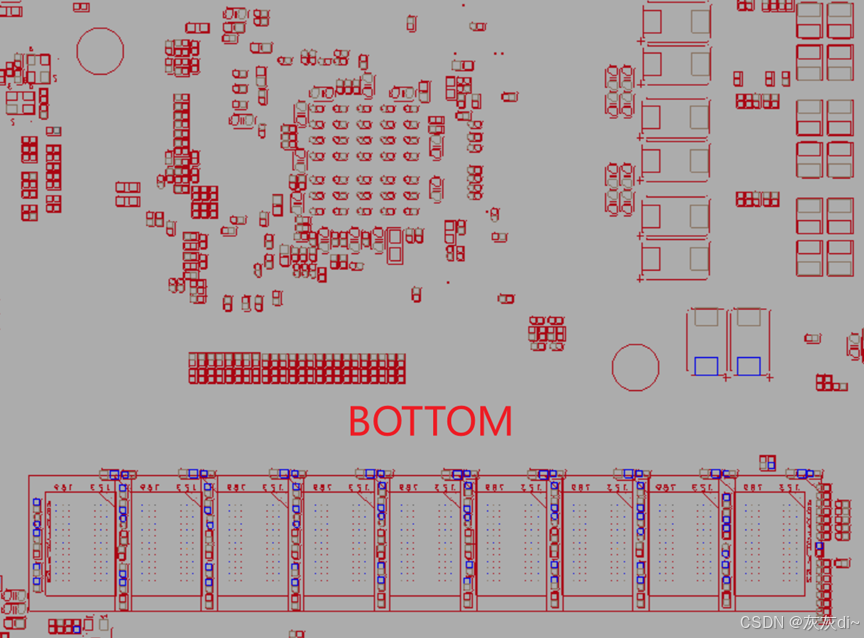

主板内存布局如下图所示,地址控制命令时钟信号的端接电阻在最右侧:

02 问题分析

此板卡送到CPU厂商适配时,厂商反馈CS1信号眼图很差。于是重点检查CS信号走线,CS0/CS1走线分别如下图:

更多详细内容,请关注《信号完整性之仿与测》公众号了解。

6899

6899

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?