VL5 位拆分与运算

点击进入题目

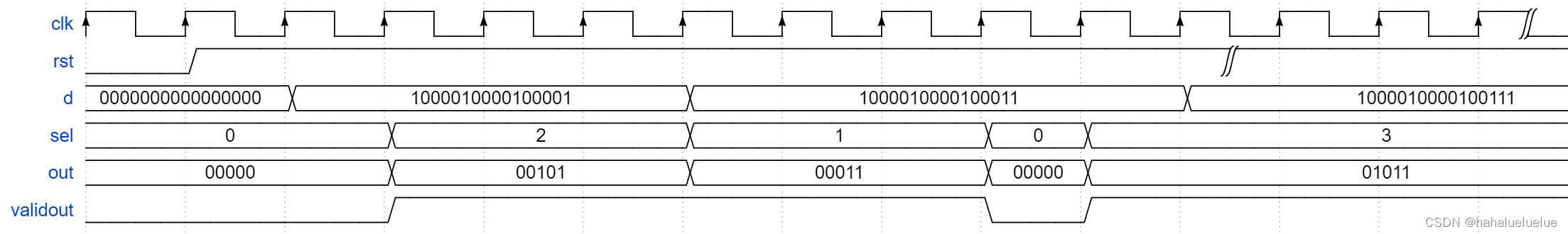

这是通过的代码,但总觉得波形图不对,根据波形图sel和out、validout中间应该没有寄存器才对

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output reg[4:0]out,//注意out和validout都是reg型变量

output reg validout

);

//*************code***********//

reg [15:0] din;//用来暂存,sel=0时才有效的输入d

always @(posedge clk or negedge rst)begin

if(!rst)begin

out<=0;

validout<=0;

din<=0;

end

else begin

case(sel)

0:begin

din<=d;

out<=0;

validout<=0;

end

1:begin

out<=din[3:0]+din[7:4];

validout<=1;

end

2:begin

out<=din[3:0]+din[11:8];

validout<=1;

end

3:begin

out<=din[3:0]+din[15:12];

validout<=1;

end

endcase

end

end

//*************code***********//

endmodule

通过的代码

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output reg[4:0]out,//注意out和validout都是reg!

output reg validout

);

//*************code***********//

reg [15:0] din;//用来暂存,sel=0时才有效的输入d

always @(posedge clk or negedge rst)begin

if(!rst)begin

out<=0;

end

else if(!sel)begin

din<=d;

end

end

always @(sel) begin

case(sel)

0:begin

out =0;

validout =0;

end

1:begin

out =din[3:0]+din[7:4];

validout =1;

end

2:begin

out =din[3:0]+din[11:8];

validout =1;

end

3:begin

out =din[3:0]+din[15:12];

validout =1;

end

endcase

end

//*************code***********//

endmodule

可是为啥两种写法都通过呢

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?