5.

非 ~

代码:

module top_module( input in,

output out

);

assign out=~in;

endmodule6.

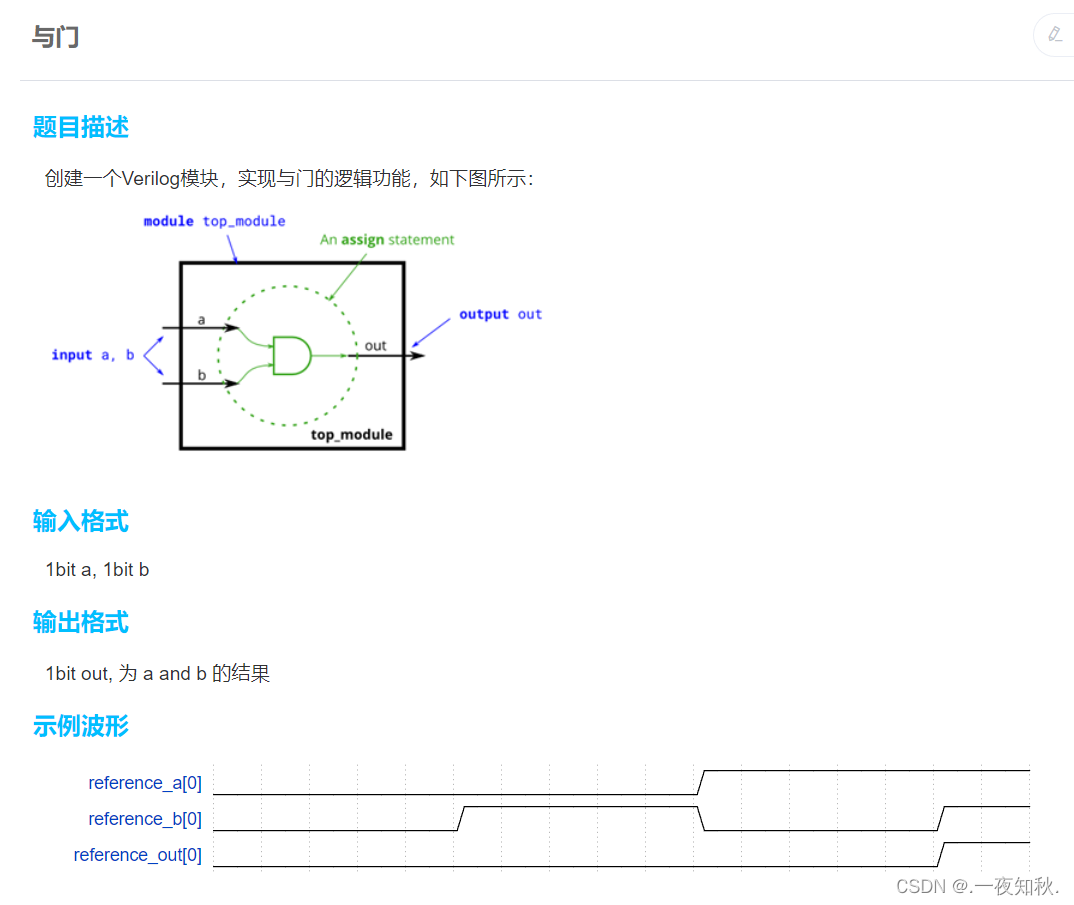

代码:

module top_module(

input a,

input b,

output out );

assign out = a&b;

endmodule

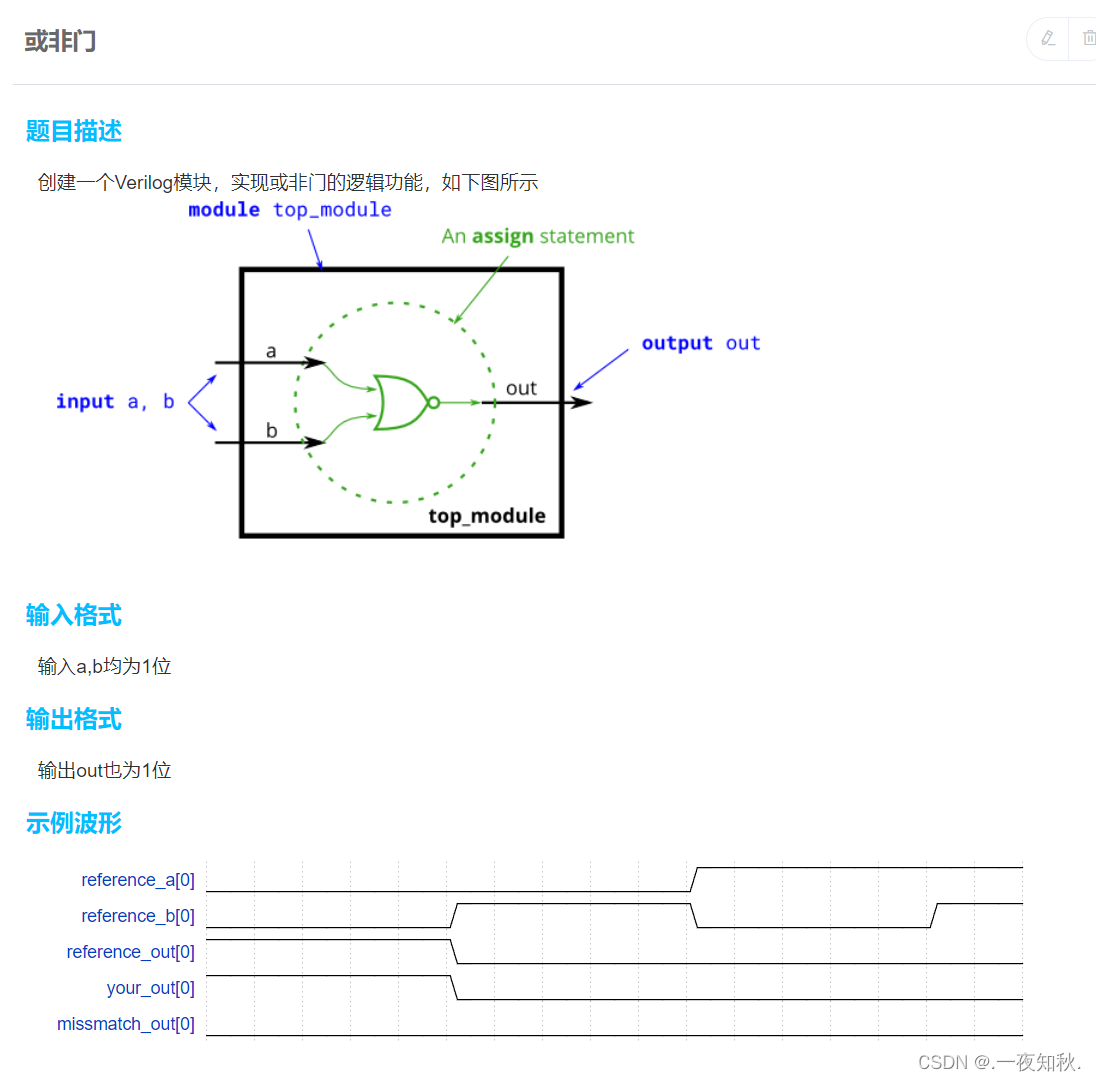

7.

tips:只有a,b均为0时,输出电平才为1,其余时刻均为低电平

代码:

module top_module(

input a,

input b,

output out );

assign out = ~(a|b);

endmodule8.

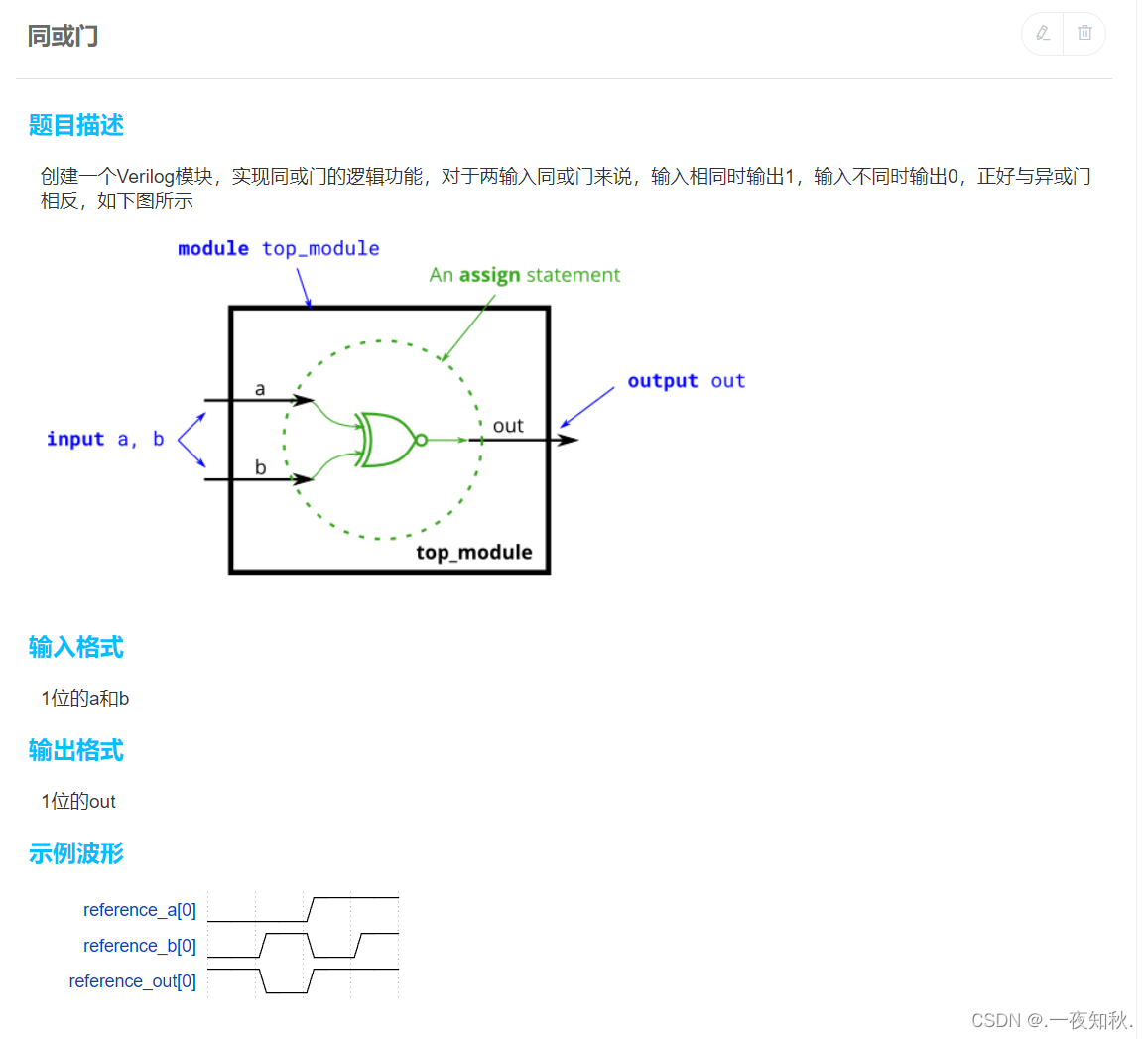

代码:

module top_module(

input a,

input b,

output out );

assign out = a==b?1:0;

endmodule

本文介绍了使用Verilog HDL实现基本逻辑门的方法,包括非门、与门及复杂的逻辑运算。通过具体的模块代码示例展示了如何利用Verilog HDL进行逻辑门的设计,并解释了每种逻辑门的工作原理。

本文介绍了使用Verilog HDL实现基本逻辑门的方法,包括非门、与门及复杂的逻辑运算。通过具体的模块代码示例展示了如何利用Verilog HDL进行逻辑门的设计,并解释了每种逻辑门的工作原理。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?