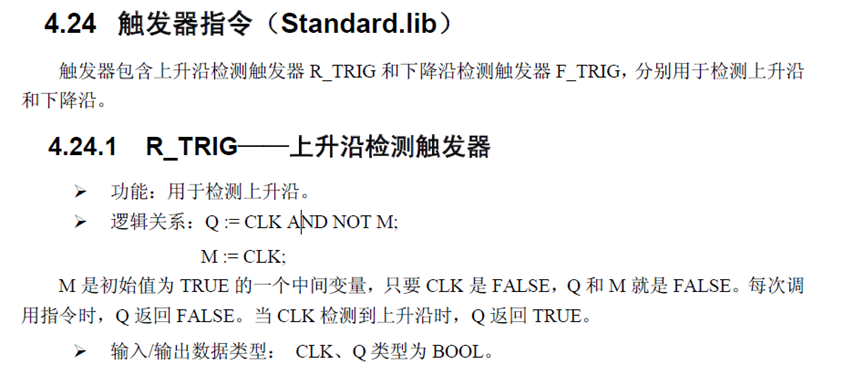

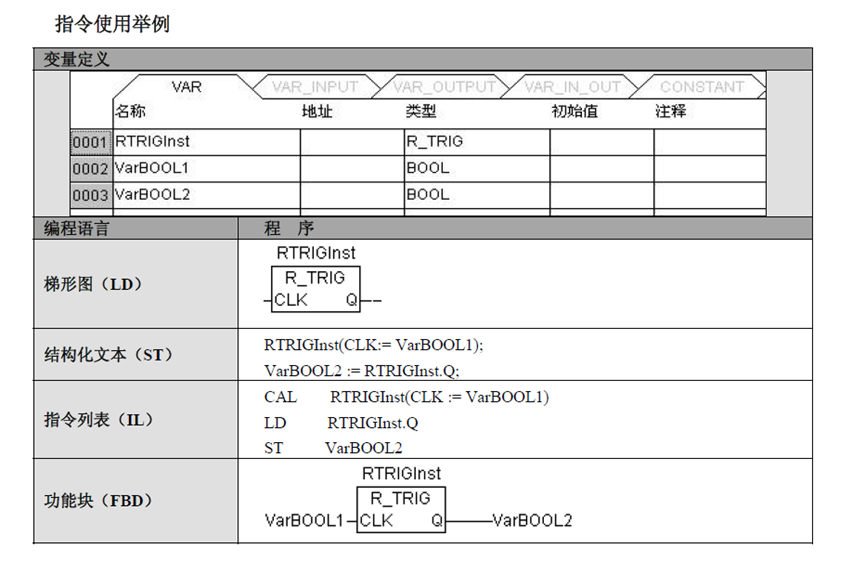

这里写的逻辑关系表达式是这样理解的

输出q=输入clk和m进行与非运算的结果

中间值m=前一次输入clk的值

(其实这个逻辑关系并不准确,因为由0变1为上升沿,由1变0为下降沿,这个逻辑关系式要加上后面的文字作为补充才算准确)

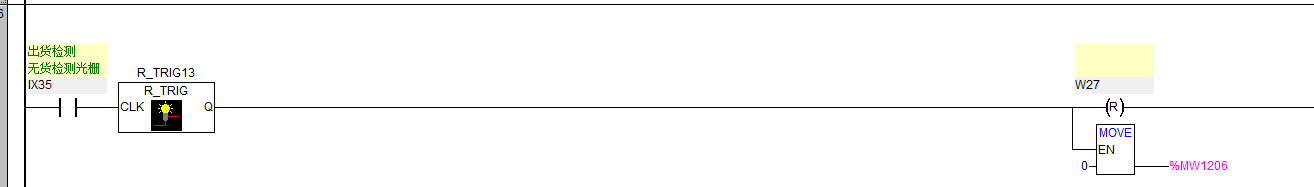

典型应用:

前面的触点触发后,母线从0变为1,产生一个上升沿,于是进行一次数据传输操作,把0赋给指定地址的数据。

- 非(NOT):标记为 ¬ 或 ~ 或 '

- 与(AND):标记为^或 ·

- 或(OR):标记为 ∨ 或

这里有点意思,我刚学数电的时候,看到与就想到加法+,看到或就想到乘法*,以为逻辑语境里的“与”和中文语境里的“加”是一个意思,以为逻辑语境里的“或”和中文语境里的“乘”是一个意思。其实大错特错了。

A逻辑语言:a或b,逻辑运算时写为a+b

例如:1或0,逻辑运算时写为1+0=1

C汉语:a与b,数学运算时为a+b

例如:1个苹果和0个苹果,数学运算时为1+0=1个苹果

B逻辑语言:a与b,逻辑运算时写为a*b

例如:1与0,逻辑运算时写为1*0=0

反正当年我学数电的时候纠结了好久,太傻了,太自以为是了,哈哈

与和或应该怎么理解?

定义:某事件发生为1,不发生为0,A、B分别是两个事件

A和B进行与逻辑运算:

A事件与B事件同时发生则称为C事件,1*1=1,1*0=0

A和B进行或逻辑运算:

A事件或B事件发生则称为C事件,1+1=1,1+0=1,0+0=0

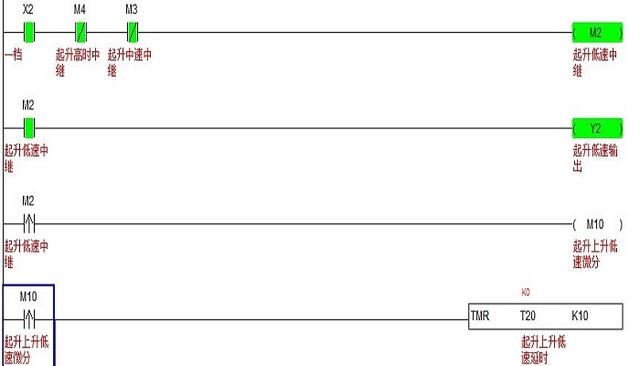

plc上升沿指令通常使用上升沿/下落指令来实现在一个扫描循环中执行的程序。

1.边脉冲指令又称脉冲执行指令,可分为接触脉冲和输出脉冲。图中如果是描述按钮的得电情况,则为0时表示按钮未按下,不能供电;1时表示按下,得电;2表示中介体为0和1。在硬件电气中没有这种状态,但是 PLC是一种软件形式模似硬件,可以有这种状态,它既不表示已经得到了电力,也不表示没有,它是在这种交换之间的某个特定时刻。

2.函数指令中 P表示上升沿。p有很多用处,如:一个按钮,按一次开,再按一关,要实现这些功能就要用到上升沿指令。按钮的功能只能通过此说明来实现。

3.上升沿信号有用.因为上升沿着该信号的扫描周期。该循环时间由程序的大小决定,如果程序已经写好,则其扫描周期是固定的。Y7可以移动。PLC执行上升沿指令没有中断执行. PLC执行上升沿指令执行一个扫描周期内有效。

延伸:升沿是指在信号从断开到接通的瞬间接通,下降沿则是信号从接通到断开的瞬间接通,而无论您的执行条件是否满足,在瞬间执行后输出就会恢复到原来的状态,通常与保持指令一起用,用保持指令做输出,用保持指令做输出,用保持指令做输出;用 OUT指令时,它的状态是看执行条件,执行条件满足 OUT就会执行输出,而执行条件满足 OUT则不执行输出。

本文解析了PLC中上升沿指令的工作原理及其典型应用场景,包括逻辑运算符的正确理解和使用,以及如何利用上升沿指令实现精确的数据传输操作。

本文解析了PLC中上升沿指令的工作原理及其典型应用场景,包括逻辑运算符的正确理解和使用,以及如何利用上升沿指令实现精确的数据传输操作。

5347

5347

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?