Overlay表示在链接时同一块地址能被覆盖使用,在多核单工程时,由于每个Core都有独立的ITCM和DTCM,因此可以使用此功能来实现。

缺点是必须自己来实现段的搬运,不能使用__main函数进行初始化;而且公用数据不能放在私有空间中,否则程序会异常。

LR_IROM1 FLASH_Core0_Start FLASH_Core0_Size { ; load region size_region

ER_IROM1 FLASH_Core0_Start FLASH_Core0_Size { ; load address = execution address

* (.isr_vector, +First)

* (InRoot$$Sections)

.ANY (+RO)

}

RAM_L DTCM_Start OVERLAY DTCM_Size {

* (.Data_Core0)

* (.Bss_Core0)

}

ARM_LIB_HEAP +0 EMPTY OVERLAY Heap_Size{} ; Heap region growing up

ARM_LIB_STACK DTCM_Start+DTCM_Size EMPTY OVERLAY -Stack_Size{} ; Stack region growing down

SRAM_2 SRAM_2_Start SRAM_2_Size {

.ANY (+RW +ZI)

}

}

Core1_LR_IROM1 FLASH_Core1_Start FLASH_Core1_Size { ; load region size_region

Core1_ER_IROM1 FLASH_Core1_Start FLASH_Core1_Size { ; load address = execution address

* (.Core1_isr_vector, +First)

startup_Core1.o (+RO)

* (.Code_Core1)

}

Core1_RAM_L DTCM_Start OVERLAY DTCM_Size {

* (.Data_Core1)

* (.Bss_Core1)

}

Core1_ARM_LIB_HEAP +0 EMPTY OVERLAY Heap_Size{} ; Heap region growing up

Core1_ARM_LIB_STACK DTCM_Start+DTCM_Size EMPTY OVERLAY -Stack_Size{} ; Stack region growing down

}

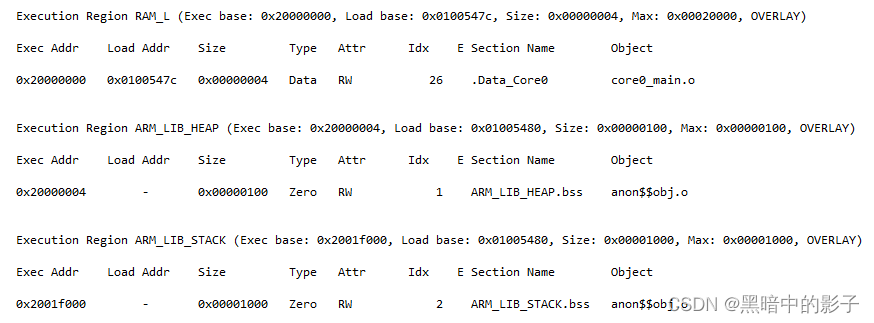

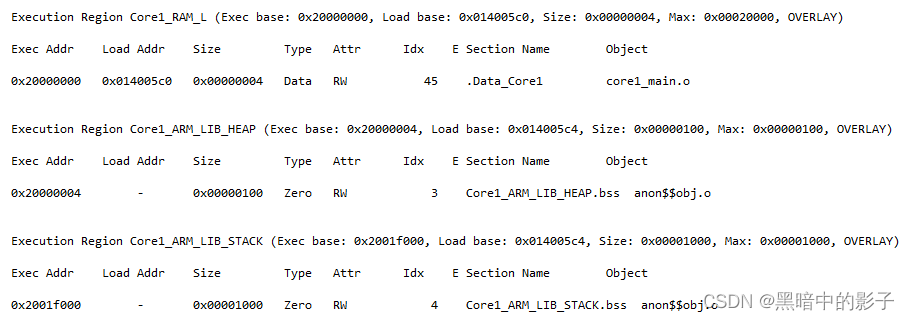

实际效果:

本文讨论了在多核单工程中使用Overlay技术,如何利用ITCM和DTCM分开存储,以及其限制,如自定义段搬运、初始化限制和公用数据位置。还展示了实际的内存区域分配情况,包括LR_IROM1、RAM_LDTCM和堆栈/堆内存区的配置。

本文讨论了在多核单工程中使用Overlay技术,如何利用ITCM和DTCM分开存储,以及其限制,如自定义段搬运、初始化限制和公用数据位置。还展示了实际的内存区域分配情况,包括LR_IROM1、RAM_LDTCM和堆栈/堆内存区的配置。

4759

4759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?