create_clock -name <name> -period <period> -waveform {<rise_time> <fall_time>} [get_ports <input_port>]| 参数 | 含义 |

|---|---|

| -name | 时钟名称 |

| -period | 时钟周期,单位为ns |

| -waveform | 波形参数,第一个参数为时钟的第一个上升沿时刻,第二个参数为时钟的第一个下降沿时刻 |

| -add | 在同一时刻源上定义多个时钟时使用 |

# Define the clocks for the GTX blocks

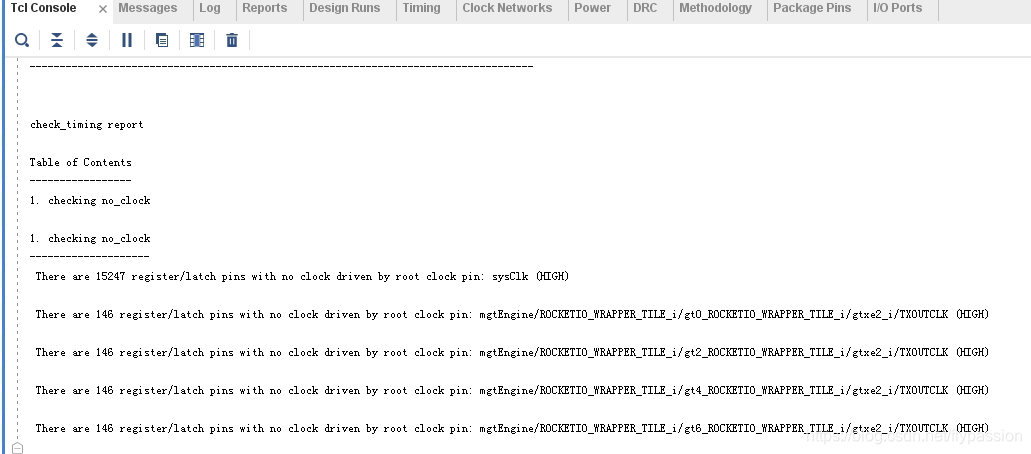

create_clock -name gt0_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt0_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK]

create_clock -name gt2_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt2_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK]

create_clock -name gt4_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt4_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK]

create_clock -name gt6_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt6_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK]

create_clock -name clk0 -period 10.0 -waveform {0 5} [get_ports clk0]

create_clock -name clk1 -period 8.0 -waveform {2 8} [get_ports clk1]

create_generated_clock -name <generated_clock_name> \

-source <master_clock_source_pin_or_port> \

-multiply_by <mult_factor> \

-divide_by <div_factor> \

-master_clock <master_clk> \

<pin_or_port>| 参数 | 含义 |

|---|---|

| -name | 时钟名称 |

| -source | 产生该时钟的源时钟 |

| -multiply_by | 源时钟的多少倍频 |

| -divide_by | 源时钟的多少分频 |

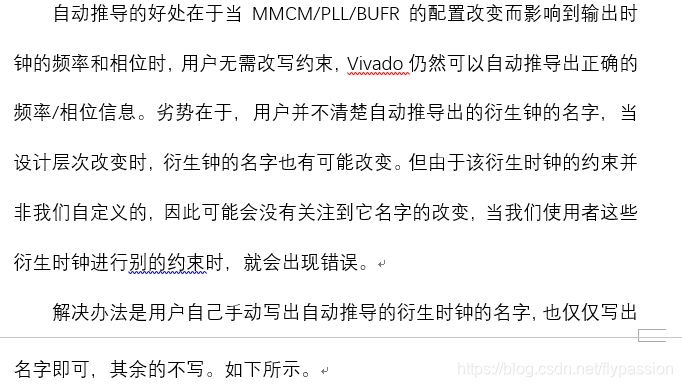

create_generated_clock -name <generated_clock_name> \

-source <master_clock_source_pin_or_port>

set_clock_groups -asynchronous -group <clock_name_1> -group <clock_name_2>

set_clock_groups -physically_exclusive -group <clock_name_1> -group <clock_name_2>

create_clock -period 10 -name clk1 [get_ports clk1]

create_clock -period 8 -name clk2 [get_ports clk2]

set_clock_groups -asynchronous -group clk1 -group clk2

create_clock -name clk1A -period 20.0 [get_ports clk1]

create_clock -name clk1B -period 10.0 [get_ports clk1] -add

create_clock -name clk1C -period 5.0 [get_ports clk1] -add

create_clock -name clk2 -period 10.0 [get_ports clk2]

set_clock_groups -physically_exclusive -group clk1A -group clk1B -group clk1C

set_clock_groups -asynchronous -group "clk1A clk1B clk1C" -group clk2

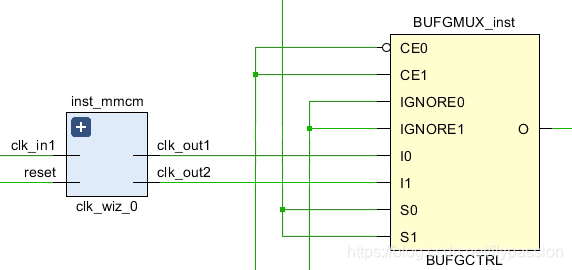

set_clock_groups -logically_exclusive \

-group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT0]] \

-group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT1]]

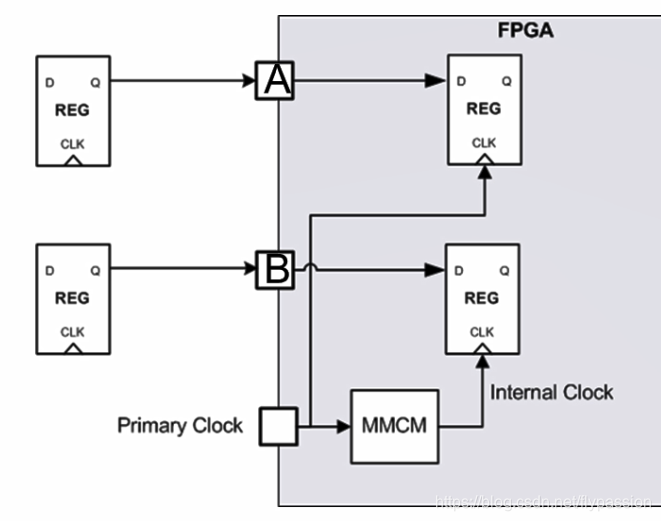

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virclk -period 6.4

set_input_delay 2 -clock sysclk [get_ports A]

set_input_delay 2 -clock virclk [get_ports B]

set_max_delay <delay> [-datapath_only] [-from <node_list>][-to <node_list>][-through <node_list>]

set_min_delay <delay> [-from <node_list>] [-to <node_list>][-through <node_list>]| 参数 | 含义 |

|---|---|

| -from | 有效的起始节点包含:时钟,input(input)端口,或时序单元(寄存器,RAM)的时钟引脚. |

| -to | 有效的终止节点包含:时钟,output(inout)端口或时序单元的数据端口. |

| -through | 有效的节点包含:引脚,端口,线网. |

(来源:科学计算technomania ,作者猫叔)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?